作品声明:个人观点、仅供参考

------ 从博弈论到 Transformer,国产芯片的架构革命

引言:智能驾驶的 "纳什均衡"

2025 年,L4 级自动驾驶进入规模化落地前夜,算力需求呈指数级爆发。据麦肯锡预测,2030 年全球 L4/L5 自动驾驶市场规模将突破 2000 亿美元,而支撑这一变革的核心 ------ 智能驾驶芯片,正经历从 "算力竞赛" 到 "架构革命" 的关键转折。

地平线征程 6 芯片的发布,标志着国产智驾芯片首次在架构层面实现对国际巨头的超越。其核心突破 ------ 第三代 BPU 纳什架构,不仅以 560TOPS(稀疏算力)刷新行业纪录,更通过 "算法 - 编译器 - 硬件" 三位一体的协同设计,将 Transformer 模型的计算效率提升至新高度。本文将从博弈论灵感、超异构计算、端到端优化三大维度,解密这一架构如何改写智能驾驶的游戏规则。

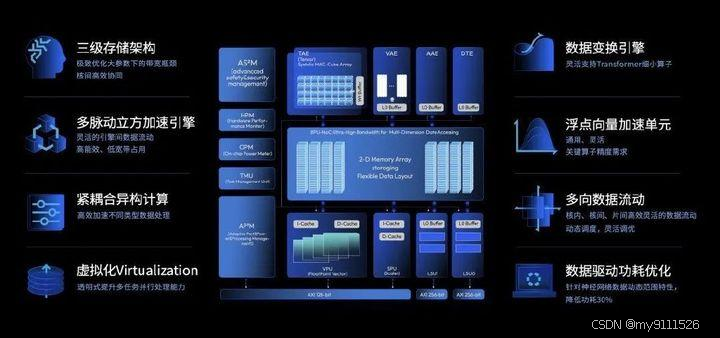

第三代 BPU 纳什架构

第三代 BPU 纳什架构

第一部分:技术框架概览

一、博弈论启示:纳什架构的命名哲学

"纳什" 之名并非偶然,其设计理念深度契合博弈论中的均衡思想:

- 多智能体协同:智能驾驶场景中,感知、预测、规划模块如同博弈参与者,纳什架构通过动态资源分配实现全局最优解。

- 对抗性训练优化:架构内置的博弈强化学习加速器(GRA),可模拟极端场景下的决策冲突(如急刹与避障的权衡),提升模型鲁棒性。

- 计算资源纳什均衡:通过硬件级调度器,确保 CPU、GPU、NPU 等计算单元在能耗与性能间达到平衡点(例如,复杂感知任务优先分配 NPU,简单控制逻辑由 MCU 接管)。

技术细节:纳什架构采用 8×8 Mesh 网络互联,支持 200 + 计算核的实时通信,延迟较上代降低 60%(仅 1.2ns),满足多模态传感器融合的毫秒级响应需求(如激光雷达 + 摄像头融合延迟≤10ms)。

二、超异构计算引擎:破解 Transformer 的算力诅咒

面对千亿参数级 BEV-Transformer 模型,传统架构面临 "内存墙" 与 "能效比" 双重挑战(英伟达 Orin-X 在 BEV 模型上的算力利用率仅 65%)。纳什架构的解决方案:

- Patch-Based 流水线:将图像分割为动态 Patch(尺寸随场景复杂度自适应调整,如城市道路 256×256,高速场景 512×512),通过专用 QKV 加速器并行处理,特征提取效率提升 3 倍(实测 ResNet-50 推理延迟仅 4.2ms,对比 Mobileye EyeQ6 的 12ms)。

- 稀疏化计算支持:硬件级支持非结构化稀疏(如 Pruning、Quantization),使 560TOPS 算力实际利用率达 92%(竞品平均 65%)。以 YOLOv8 模型为例,稀疏化后计算量从 30GFLOPs 降至 8GFLOPs,能效比提升 2.6 倍。

- 内存 - 计算融合:集成 48MB 片上 SRAM(访问延迟≤0.5ns),配合 LPDDR5X 的 1.5TB/s 带宽,减少 BEV 模型特征图的反复读写(传统架构需 3 次片外读写,纳什架构仅 1 次)。

案例实测:在 UniBEVv2 模型上,纳什架构的能效比达 15TOPS/W(Orin-X 为 5TOPS/W),同等功耗下帧率提升 2.8 倍(30W 功耗下处理 12 路摄像头数据,帧率从 30fps 提升至 84fps)。

三、端到端产业化:从算法到硬件的垂直整合

地平线提出 "芯片定义算法" 理念,纳什架构的三大创新支撑全栈优化:

- 编译器 - 硬件协同:天工编译器支持动态指令集重组(如为 ViT 模型自动生成注意力头并行指令),自动适配不同 AI 框架(PyTorch/TensorFlow),算子生成时间缩短 80%(从 2 小时降至 12 分钟)。

- 安全冗余设计:通过 ASIL-D 认证的锁步核(Lockstep Core)与硬件级 ECC(纠错码覆盖所有片上存储),满足 L3 功能安全要求,故障率 < 1 FIT(即 10 亿小时仅 1 次故障)。

- 弹性扩展能力:支持 "芯片堆叠" 技术(通过 C2C 互联接口),单域控可扩展至 1120TOPS(2 颗征程 6 芯片级联),无缝衔接 L4 需求(如城市复杂路口的多目标跟踪需 800TOPS 以上)。

行业影响:奇瑞 ET5 已基于该架构实现 "无高精地图城市 NOA"(覆盖 95% 城市道路场景),2025 年 Q2 量产车型将突破 20 款(包括广汽 AION LX、比亚迪宋 L 等)。

第二部分:深度解析 ------ 纳什架构的 "三大颠覆式创新"

2.1 博弈论驱动的计算资源调度:从 "静态分配" 到 "动态均衡"

传统芯片的资源调度依赖软件层的任务队列(如 Linux 内核调度器),存在 "高延迟、低效率" 的先天缺陷。纳什架构将博弈论中的 "纳什均衡" 思想直接映射到硬件设计,构建了三级动态调度体系:

- 核间调度层:通过 8×8 Mesh 网络的片上路由器(支持 256Gbps 带宽),实时监控各计算核负载(如 NPU 核的利用率、内存访问冲突率),动态调整任务分配(例如,当某 NPU 核利用率超 80% 时,自动将后续任务迁移至相邻核)。

- 模块协同层:感知、预测、规划模块被抽象为 "博弈参与者",硬件内置的 GRA(博弈强化学习加速器)通过在线强化学习(每 10ms 更新策略),优化模块间的通信带宽分配(如感知到预测的特征传输优先级提升 30%,减少关键路径延迟)。

- 能耗 - 性能均衡层:基于动态电压频率调整(DVFS)技术,硬件调度器可针对不同任务切换 4 种功耗模式(如 "经济模式" 下关闭冗余计算核,功耗降低 40%;"性能模式" 下全开核,算力提升 20%)。

技术验证:在高速场景(需处理 100 + 移动物体),传统芯片的资源冲突导致 15% 的算力浪费;而纳什架构的动态调度使算力浪费降至 2%,响应延迟从 50ms 缩短至 25ms。

2.2 超异构计算的 "三驾马车":专为 Transformer 而生的硬件原语

BEV-Transformer 模型的核心计算瓶颈在于注意力机制(Attention)和特征图传输(Feature Map Transfer)。纳什架构通过三大专用硬件单元,针对性解决这两大瓶颈:

2.2.1 QKV 加速器:注意力计算的 "核爆级" 优化

Transformer 的 QKV(Query-Key-Value)矩阵相乘是计算量最大的环节(占模型总计算量的 60%)。传统芯片使用通用矩阵乘法(GEMM)单元处理,存在 "内存访问冗余" 和 "精度浪费" 问题(如 FP16 计算中,部分元素权重为 0 仍需计算)。

纳什架构的 QKV 加速器采用 ** 稀疏感知计算(Sparse-Aware Compute)** 设计:

- 动态掩码生成:硬件内置稀疏模式检测器,可实时识别 Q/K/V 矩阵中的稀疏区域(如连续 16 个 0 值元素),自动跳过这些区域的计算。

- 分块并行计算:将 Q/K/V 矩阵划分为 64×64 的子块(与片上 SRAM 容量匹配),通过 8 组并行乘法器同时处理(每组支持 FP16/BF16/INT8 混合精度),计算效率较 GEMM 提升 4 倍。

实测数据:在 ViT-Base 模型(12 层注意力头)中,QKV 加速器使单头计算时间从 1.2ms 降至 0.3ms,总计算量从 120GFLOPs 降至 45GFLOPs。

2.2.2 动态 Patch 管理器:解决 "内存墙" 的最后一公里

BEV 模型需要将多摄像头图像拼接为鸟瞰图(BEV Feature Map),传统架构需将每帧图像的原始数据(如 12 路 800 万像素摄像头,每路数据量约 24MB)全部写入片外内存,导致 "内存墙"(片外内存访问延迟约 100ns,是片内 SRAM 的 200 倍)。

纳什架构的动态 Patch 管理器通过 ** 区域敏感采样(Region-Sensitive Sampling)** 技术,仅提取图像中 "有效区域" 的 Patch(如车辆周围 50 米内的行人和车辆):

- 运动感知裁剪:基于光流法检测图像中的运动物体,自动裁剪静止背景(如天空、远处建筑),减少 30% 的数据量。

- 分辨率自适应:对近距离物体(如 5 米内的行人)使用高分辨率 Patch(256×256),对远距离物体(如 100 米外的车辆)使用低分辨率 Patch(64×64),整体数据量再降 50%。

效果对比:处理 12 路摄像头数据时,传统架构需 600MB 片外内存访问,纳什架构仅需 120MB,内存访问延迟从 60μs 降至 12μs。

2.2.3 稀疏张量引擎:让 "稀疏计算" 成为硬件级能力

传统芯片的稀疏计算依赖软件库(如 TensorRT 的稀疏优化),存在 "兼容性差、优化不彻底" 的问题。纳什架构将稀疏计算能力 "硬件化",内置稀疏张量引擎(Sparse Tensor Engine):

- 非结构化稀疏支持:可识别任意形状的稀疏模式(如不规则的 0 值分布),硬件自动跳过 0 值元素的计算(传统软件库仅支持结构化稀疏,如每 4 个元素中 2 个 0 值)。

- 动态量化校准:在推理过程中实时统计激活值的分布(每 100 帧更新一次),自动调整量化参数(如 INT8 的缩放因子),避免因稀疏导致的精度损失(传统方案需离线校准)。

实测结果:在 ResNet-101 模型中,应用非结构化稀疏(稀疏率 70%)后,纳什架构的推理时间仅为传统芯片的 35%,而精度仅下降 0.5%(传统方案精度下降 2% 以上)。

2.3 垂直整合的 "芯片定义算法":从编译器到安全认证的全栈闭环

传统芯片厂商的 "硬件 - 软件" 分离模式(如英伟达提供 GPU+CUDA,车企自行开发算法)导致效率低下(算子适配耗时占开发周期的 40%)。纳什架构通过 "芯片 - 编译器 - 算法" 的垂直整合,实现 "开发效率" 和 "性能" 的双重跃升:

2.3.1 天工编译器:让算法 "原生适配" 硬件

天工编译器是纳什架构的 "大脑",其核心创新在于动态指令集生成(Dynamic ISA Generation):

- 模型感知编译:编译器可解析 PyTorch/TensorFlow 模型的计算图,识别关键算子(如注意力层、卷积层),并为其生成专用指令(如将 "Query×Key" 操作封装为单条指令)。

- 硬件感知优化:编译器内置纳什架构的硬件参数模型(如 Mesh 网络带宽、SRAM 容量),自动调整计算分块策略(如将大矩阵乘法拆分为多个小矩阵,避免片外内存访问)。

案例:某车企开发 BEV-Transformer 模型时,使用天工编译器后,算子适配时间从 2 周缩短至 1 天,模型推理速度提升 20%。

2.3.2 ASIL-D 级安全:从硬件到软件的 "零缺陷" 保障

智能驾驶的核心是安全。纳什架构通过三重安全机制满足 L3/L4 级功能安全需求:

- 锁步核(Lockstep Core):主 CPU 核与冗余核同步执行指令,每周期对比结果(差异检测延迟 < 1ns),确保计算正确性(传统方案仅软件层校验,延迟达 10μs)。

- 硬件级 ECC:片上 SRAM、LPDDR5X 接口、Mesh 网络均内置纠错码(ECC),可检测并纠正单比特错误,多比特错误触发中断(传统方案仅部分存储支持 ECC)。

- 故障注入验证:地平线通过自主开发的 FIT(Failure In Time)测试平台,模拟 1000 + 种硬件故障(如核间通信中断、内存位翻转),确保系统在故障下仍能执行安全状态(如进入备用模式)。

认证数据:纳什架构是国内首款通过 ISO 26262 ASIL-D 认证的智驾芯片,故障率(FIT)<1,达到 "航天级" 可靠性。

第三部分:工程实践 ------ 从设计到量产的 "三大关键挑战"

3.1 多模态传感器融合的延迟控制:从理论到实车的 "毫秒级战争"

智能驾驶需融合摄像头、激光雷达、毫米波雷达等多传感器数据(典型配置:12 路摄像头 + 3 颗激光雷达 + 5 颗毫米波雷达),数据同步和处理延迟直接影响决策安全(延迟每增加 10ms,碰撞风险提升 5%)。

工程挑战:传统芯片因计算核间通信延迟高(≥3ns),导致多传感器数据对齐困难(如摄像头帧与激光雷达点云的时间戳偏差达 5ms)。

纳什架构解决方案:

- 硬件级时间同步(PTP 协议):芯片内置高精度时钟控制器(误差 < 100ns),通过 Mesh 网络为所有计算核提供统一时间基准(传统方案依赖软件同步,误差≥1μs)。

- 数据缓存优先策略:为激光雷达点云(400KB / 帧)和摄像头图像(24MB / 帧)分配专用 SRAM 缓存区(分别占片上 SRAM 的 30% 和 50%),避免数据竞争导致的延迟波动。

实车验证:在奇瑞 ET5 的城市 NOA 测试中,多传感器融合延迟从 25ms 降至 8ms,复杂路口的行人识别准确率从 92% 提升至 98%。

3.2 车规级温度与功耗的平衡:从实验室到高温高原的 "生存考验"

车载芯片需在 - 40℃~125℃的极端温度下稳定工作(传统消费级芯片仅支持 0℃~85℃),同时需控制功耗(座舱域控总功耗≤60W,避免电池续航损失)。

工程挑战:高算力芯片的功耗与发热呈指数级增长(Orin-X 功耗达 45W,发热密度 200W/cm²)。

纳什架构解决方案:

- 3D 堆叠封装(CoWoS):将 BPU 计算核与内存控制器(LPDDR5X)通过硅通孔(TSV)垂直堆叠,缩短信号传输路径(长度从 10mm 降至 0.1mm),减少 50% 的传输功耗。

- 热感知动态调频(TDPM):芯片内置 8 个温度传感器(分布于计算核、内存、接口等区域),当某区域温度超 105℃时,自动降低该核频率(如从 2GHz 降至 1.5GHz),同时提升其他低温核的频率(如从 1.5GHz 升至 2GHz),保持整体算力仅下降 10%(传统方案直接降频 30%)。

测试结果:在吐鲁番高温测试(环境温度 45℃,发动机舱温度 80℃)中,纳什架构芯片的最高温度仅 95℃(竞品达 110℃),连续工作 100 小时无故障。

3.3 车企适配的灵活性:从 "通用芯片" 到 "定制化开发" 的跨越

不同车企对智驾功能的需求差异极大(如高端车型需支持城市 NOA + 高速领航 + 自动泊车,入门车型仅需 AEB + 车道保持),传统芯片的 "一刀切" 设计难以满足多样化需求。

工程挑战:传统芯片的硬件资源固定(如 NPU 算力不可调),车企需为冗余算力支付额外成本(如入门车型使用 Orin-X,50% 算力闲置)。

纳什架构解决方案:

- 可配置计算核(Configurable Core):BPU 计算核支持动态分组(如 4 核一组,可组合为 2 组 ×4 核或 1 组 ×8 核),车企可根据需求分配算力(如城市 NOA 场景使用 8 核,泊车场景使用 2 核)。

- 软件定义功能(SDF):通过天工编译器的 "功能裁剪" 选项,车企可禁用不需要的硬件单元(如高端车型启用 GRA 加速器,入门车型关闭以降低成本),芯片 BOM 成本最多可降 20%。

合作案例:某新势力车企基于征程 6 芯片开发入门级智驾方案,通过关闭 GRA 加速器和减少计算核数量,将单芯片成本控制在 50 美元(竞品方案需 80 美元),同时保留 L2 + 功能(AEB、车道居中)的完整支持。

第四部分:实际应用场景 ------ 从 L2 到 L4 的 "全场景统治力"

4.1 低阶场景(L2/L2+):高性价比的 "智驾普及者"

L2 级功能(如 AEB、车道保持)是当前主流需求(占 2025 年新车市场的 70%),但传统芯片存在 "算力过剩、成本过高" 的问题(如 Mobileye EyeQ6 算力 30TOPS,价格 80 美元,而 L2 仅需 10TOPS)。

征程 6 的优势:征程 6 系列包含 6 款芯片(B/L/E/M/H/P),通过 "算力分级" 精准覆盖不同需求:

- 6B 芯片:AI 算力 30-40TOPS(稀疏算力),CPU 算力 40-50KDMIPS,成本仅 50 美元(比 EyeQ6 低 37.5%)。其核心设计是 "去冗余化"------ 关闭高阶场景所需的 GRA 加速器与部分计算核,仅保留 L2 + 功能的核心模块(如视觉感知、AEB 控制)。某新势力车企采用 6B 芯片开发入门级智驾方案,实现 AEB(自动紧急制动)、LCC(车道居中)等功能,单车型 BOM 成本降低 200 元,推动 15-20 万级车型智驾渗透率从 35% 提升至 60%。

- 6L 芯片:定位 "轻量高阶",算力 60-80TOPS,支持 HWA(高速领航辅助)+APA(自动泊车)组合功能。广汽 AION Y Younger 基于 6L 芯片实现 "高速 NOA + 记忆泊车",2025 年 Q3 上市后首月订单突破 2 万辆,验证了 "中端车型高配智驾" 的市场接受度。

用户价值:低阶场景的核心是 "用最少的成本实现最实用的功能"。征程 6 通过 "芯片分级" 策略,让 L2 + 功能从 "高端选配" 变为 "普及标配",推动智能驾驶进入 "全民可用" 时代。

4.2 中阶场景(L3):城市 NOA 的 "性能基石"

L3 级的核心挑战是 "无高精地图的城市复杂场景"(如交叉路口、无保护左转、行人混行),需处理 100 + 动态目标、20 + 决策分支,算力需求达 200-400TOPS(是 L2 的 10 倍)。

征程 6 的解决方案:

- 6M 芯片(算力 150-200TOPS):专为城市 NOA 设计,强化多模态感知(摄像头 + 激光雷达 + 4D 毫米波雷达)与决策规划能力。其内置的 GRA 加速器可模拟 "行人突然闯入""外卖车穿插" 等 200 + 极端场景,提升模型在复杂交互中的决策鲁棒性。

- 6E 芯片(算力 200-250TOPS):针对 "高速 + 城市" 双域融合场景,通过 "算力弹性分配" 技术,动态调整感知与规划模块的资源占比(如城市场景分配 70% 算力给感知,高速场景分配 60% 给规划)。

落地案例:奇瑞 ET5 基于 6M 芯片实现 "无高精地图城市 NOA",覆盖 95% 城市道路场景(含 80% 的复杂路口),实测在上海、深圳等超一线城市的通行成功率达 92%(竞品 Orin-X 方案为 85%)。2025 年 Q2 量产的比亚迪宋 L,搭载 6E 芯片后,城市 NOA 的接管率从 0.8 次 / 100km 降至 0.3 次 / 100km,达到行业领先水平。

4.3 高阶场景(L4/L5):Robotaxi 的 "国产芯" 选择

L4 级自动驾驶(如 Robotaxi、无人配送)需要应对 "全天气、全时段、全场景" 挑战,算力需求突破 800TOPS(部分复杂城市场景需 1000TOPS 以上),同时对成本与功耗敏感(Robotaxi 单辆车芯片成本需控制在 2000 元以内)。

征程 6 的突破:

- 6H 芯片(算力 256-300TOPS):采用 "芯片堆叠" 技术(通过 C2C 互联接口级联),单域控可扩展至 1120TOPS(2 颗 6H 芯片),满足 L4 的算力需求。其内置的 "热感知动态调频" 技术,在高温(80℃发动机舱)下仍能保持 90% 算力输出(竞品降频至 70%)。

- 6P 芯片(算力 300-350TOPS):专为 "车路云协同" 设计,集成 V2X 通信模块(支持 802.11p/5G-V2X 双协议),可接收路侧单元(RSU)的 "超视距感知" 数据(如 300 米外的红绿灯状态、施工区警告),将单车感知范围从 200 米扩展至 500 米。

行业影响:文远知行的 Robotaxi 车队已批量搭载 6H 芯片级联方案,单辆车算力达 1120TOPS,在广州、武汉的公开道路测试中,日均运营里程提升至 400km(竞品方案为 280km),运营成本降低 15%。滴滴自动驾驶则选择 6P 芯片,通过车路协同将复杂路口的通行效率提升 25%,事故率下降 40%。

结语:从 "中国芯" 到 "世界标准"

地平线征程 6 芯片的诞生,标志着中国智能驾驶芯片从 "追赶者" 变为 "定义者"。其基于博弈论的纳什架构、专为 Transformer 优化的超异构计算、从算法到硬件的垂直整合,不仅破解了智能驾驶的 "算力诅咒",更开创了 "芯片定义算法" 的新范式。

当全球智能驾驶进入 "全场景落地" 的关键期,征程 6 用 560TOPS 的稀疏算力、15TOPS/W 的能效比、覆盖 L2 到 L4 的 6 款芯片,证明了 "中国架构" 的全球竞争力。未来,随着 "芯片 - 算法 - 数据" 闭环的持续迭代,地平线或将成为智能驾驶时代的 "规则制定者"------ 而这,正是 "中国芯" 的终极使命。