系统同步接口

文章目录

- 系统同步接口

- [📘 FPGA 输入延迟时序分析笔记](#📘 FPGA 输入延迟时序分析笔记)

-

- [1 系统同步接口:为什么"同源"还这么难?](#1 系统同步接口:为什么“同源”还这么难?)

- [2 建立时间裕量(Setup Slack)拆解](#2 建立时间裕量(Setup Slack)拆解)

- [3 保持时间裕量(Hold Slack)拆解](#3 保持时间裕量(Hold Slack)拆解)

- 后面一系列分析,均可将外部设备和FPGA想象为在一个设备内种的分析方式。即,片内两个寄存器之间的时序计算 ,时刻0点是在源时钟为起点(源同步两个时钟之间是有相位差偏斜的,而系统同步可当做没有偏斜,即clk1和clk2相减为0)

- 通过输入input_delay最大最小值,让软件知晓 如何计算建立时间裕量和保持时间裕量,才能正确分析是否违例,免得看着没时序问题,实际上隐藏时序问题不知道

- 建立时间裕量是再下一个时钟周期进行计算,时刻以源时钟开始为标准。

- input_delay和output_delay min和max,均是对外部走线源和目的相对延迟 来说(延迟分两个,内部延迟和外部延迟,input的外部是指源到FPGA端口的一段,out的外部是FPGA端口到外部设备端口这一段)。在分析时均以如何试探建立时间和保持时间的极限值来进行计算,以这个思路就好分析公式的用意。总体来说,求的是源到目的到达时间的相对值。

- 再次强调,input_delay和output_delay min和max是计算相对FPGA的外部,是外部,是外部,不管是系统同步还是源同步,要分清楚什么是外部

- 公式中时序分析中是源减目的还是目的减源,都可以,求出相对值即可,正负的问题,一般是在建立时间分析时是目的减去源,得到一个正值,如果为负值则违例。对于保持时间来说,源减去目的得到一个正值,说明数据来的慢,不会冲坏保持时间裕量中的数据,负值表示违例。因此建立时间和保持时间均以负表示违例,这样就统一了

- 公式求IO延迟中,求的是外部数据走向相对于时钟的偏差(数据和时钟的关系),因此以原数据路径到FPGA端口或者端口到外部设备的相对于时钟的延迟来计算,即外部原延迟减去时钟之间的偏差。即,数据延迟多少个外部相对时间到达目标设备的外部接口(不包括设备内部延迟)

- 为什么再分析输出延迟的时候,不计算FPGA内部的时延,之所以计算外部,就是因为内部的,FPGA自己知道,不用再计算,只计算外部时钟和数据之间相对的偏差即可

📘 FPGA 输入延迟时序分析笔记

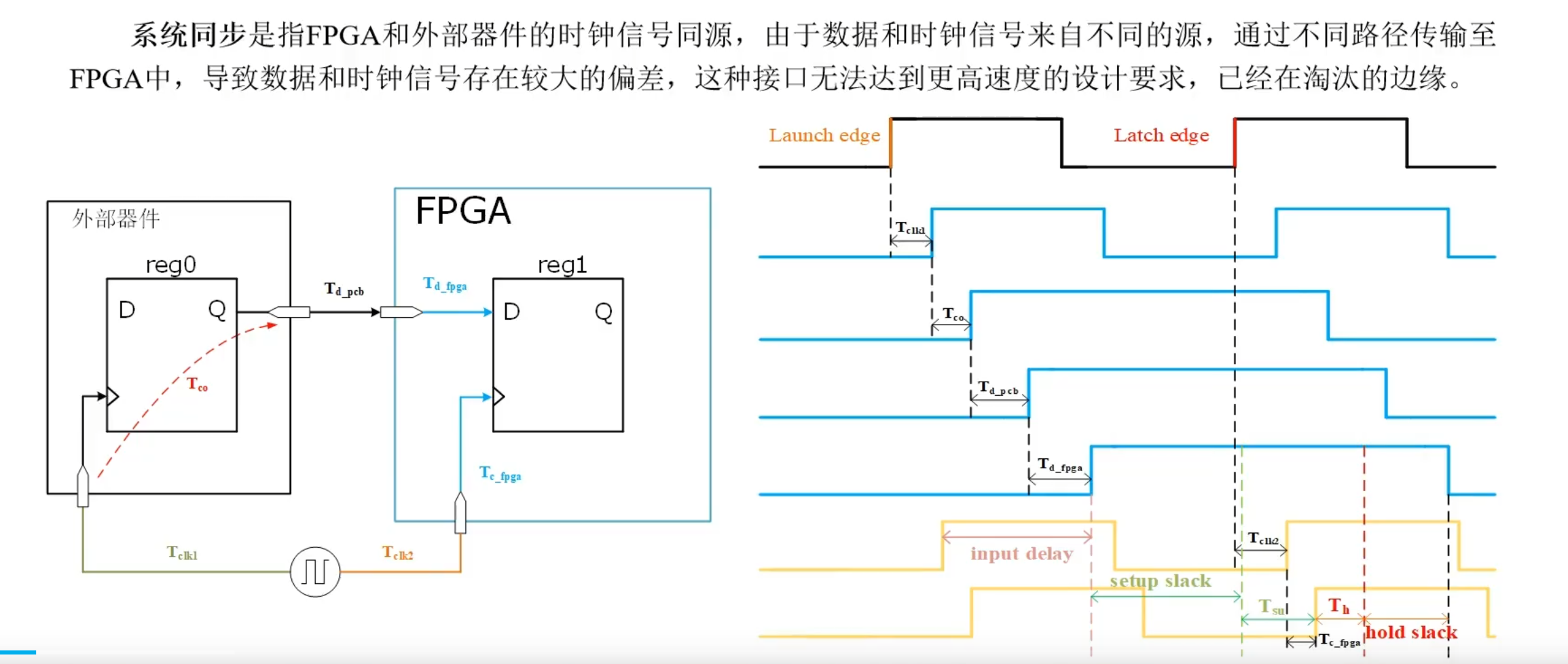

1 系统同步接口:为什么"同源"还这么难?

- 定义:FPGA 与外部器件共用同一颗晶振 ,但数据/时钟走线长度不同 → 产生板级 skew。

- 现状:高速场景(>200 MHz)几乎被淘汰,源同步 上位;但成本敏感板卡(MCU+FPGA、工业控制)仍在用。

- 痛点:PCB 走线 1 cm ≈ 60 ps,正反各跑 5 cm 就吃掉 300 ps ------28 nm FPGA 的 400 MHz 周期才 2.5 ns,12% 就这么没了。

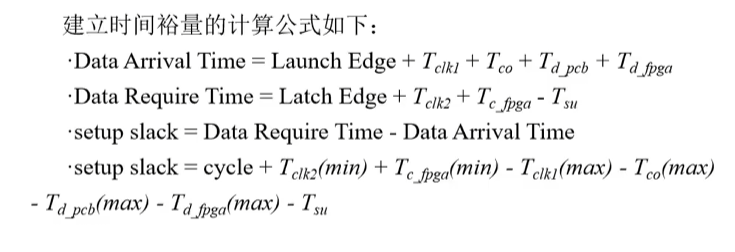

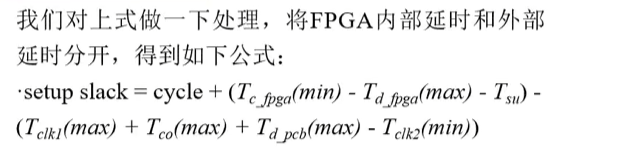

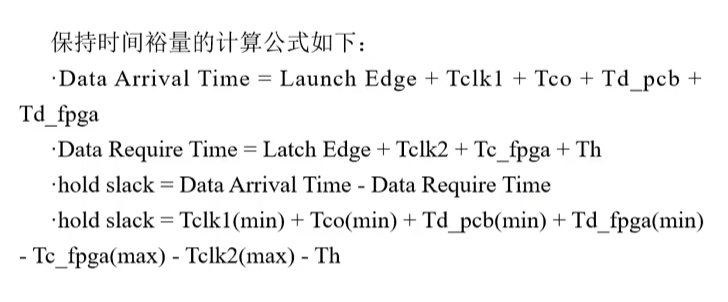

2 建立时间裕量(Setup Slack)拆解

直接贴图

- 需要保持清醒的时,所有路径的计算延迟都是从约定好的0时刻开始(也就是主时钟约束的开始)

公式分析和记忆要点:

- 建立时间:需求时间减去到达时间。因为需要时间是在下个时钟周期采样,所以要加上一个时钟周期。

- 保持时间:源减去目的。注意这里是在同一周期的计算,所以不需要T

- Tclk1和Tclk2,因为是系统同步,一般这两个时钟到达端口可以认为是相等或者近似的(源同步则不一定)

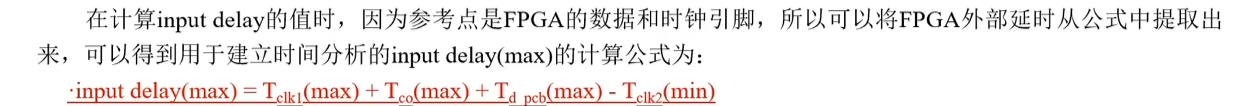

这里整理的公式比较重要,为了后续做IO约束有帮助(IO延迟约束,计算的时板外的PCB走线的时间)

- 其中注意是Tclk1减去Tclk2或者是Tclk2-Tclk1,就是要理解这个偏移量对求Max时是最差好事最好来计算,当然是求最差,要加上一个值来算(因为偏差时都有可能得,尽可能让这个值变大就行,下面保持时间就是经可能变小即可,不要死记硬背)

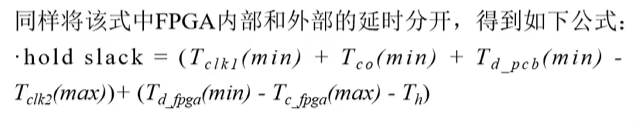

3 保持时间裕量(Hold Slack)拆解

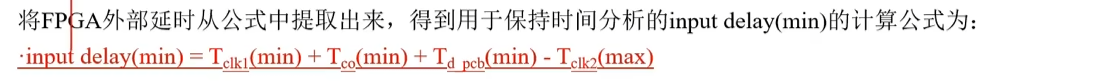

- 这里是求input_delay最小

由上面公式即可算出IO约束

- 后面所有的时序约束都类似,学会一个,后面源同步,系统同步基本上分析套路都类似,只是一些小细节上不一样