一、简介

为了创建芯片内部的微型器件,我们需要不断地沉积一层层的薄膜并通过刻蚀去除掉其中多余的部分,另外还要添加一些材料将不同的器件分离开来。每个晶体管或存储单元就是通过上述过程一步步构建起来的。我们这里所说的"薄膜"是指厚度小于1微米(μm,百万分之一米)、无法通过普通机械加工方法制造出来的"膜"。将包含所需分子或原子单元的薄膜放到晶圆上的过程就是"沉积"

要形成多层的半导体结构,我们需要先制造器件叠层,即在晶圆表面交替堆叠多层薄金属(导电)膜和介电(绝缘)膜,之后再通过重复刻蚀工艺去除多余部分并形成三维结构。可用于沉积过程的技术包括化学气相沉积 (CVD)、原子层沉积 (ALD) 和物理(等离子)气相沉积 (PVD),采用这些技术的方法又可以分为干法和湿法沉积两种。

二、成膜工艺

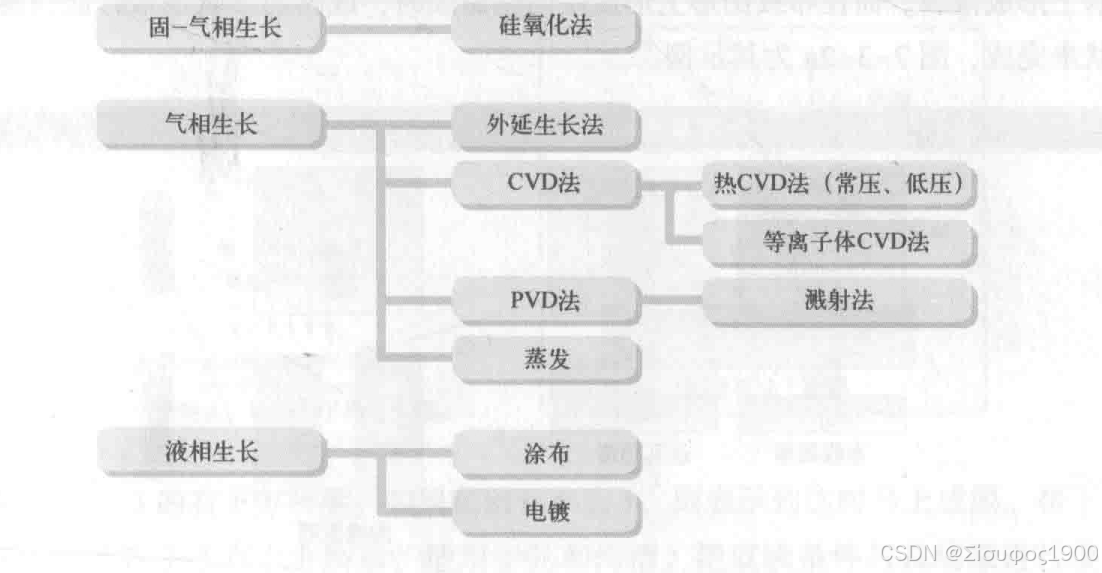

分类

半导体工艺中使用的薄膜通常以气相沉积的方法来成膜。当然,还有采用液相方法进行涂 布和电镀的,这两种多用于其他用途,一般都是用气相沉积来实现的。气相成膜的特点包括

1.利用化学反应,可以精确控制薄膜厚度和质量。

2.干燥气氛,容易控制反应。

3.容易维持洁净环境(材料、气氛)。

4.可以均匀地大面积成膜,

5.在某些情况下,可批量处理大量的晶圆

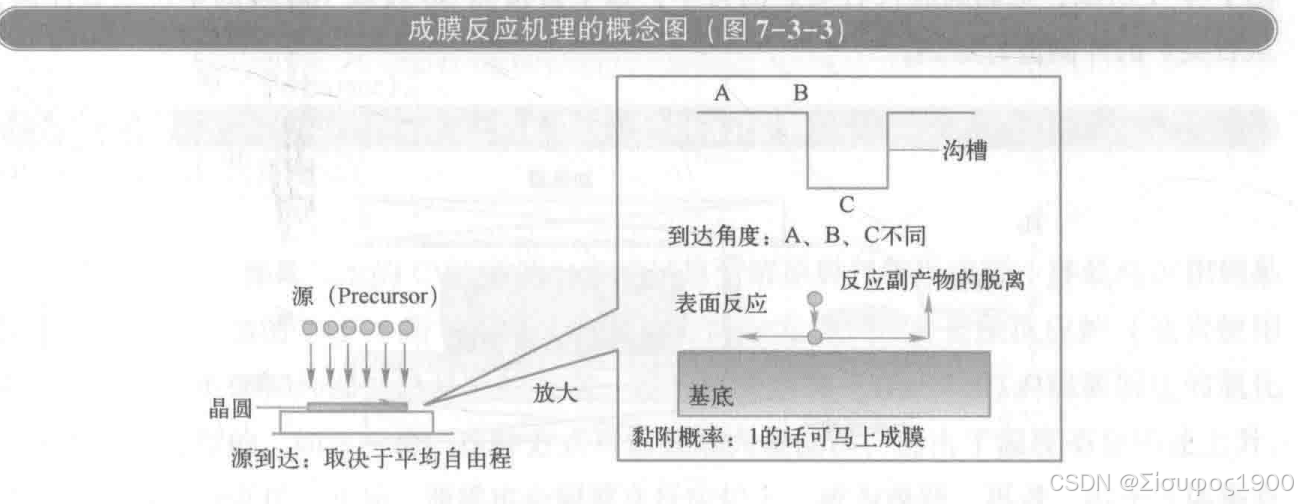

成膜机理

为什么是氧化硅膜?

在半导体器件早期阶段,我们使用的不是硅,而是同在Ⅳ主族的错。然而,转瞬之

间锗就把主角的位置让给了硅。究其原因,地表含有大量的硅,从材料的储量来看,硅

具有先天优势。另一方面,锗的热氧化膜不稳定,而硅的热氧化膜则相对稳定。这导致

了MOS晶体管的发展。此外,硅比锗具有更大的带隙。,因此在耐热性和耐压方面也更

有利。

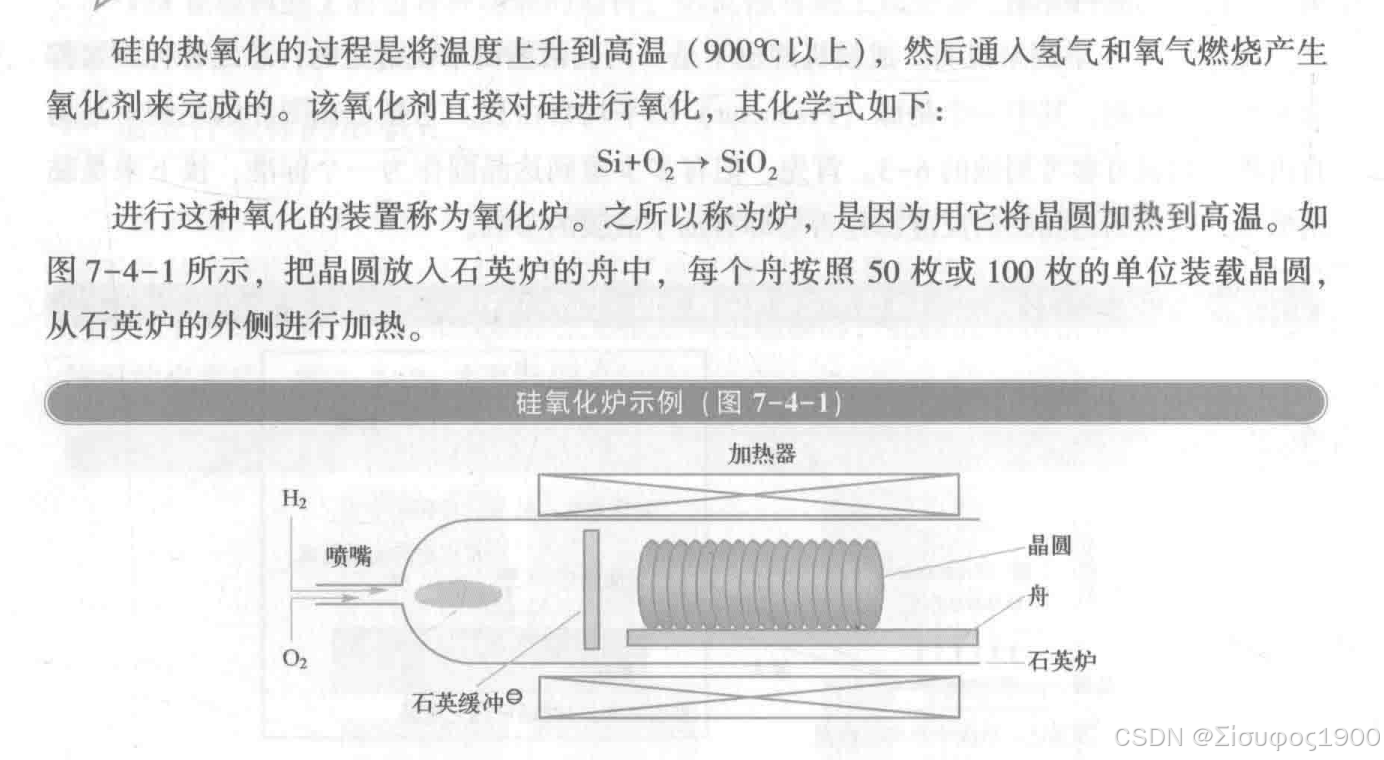

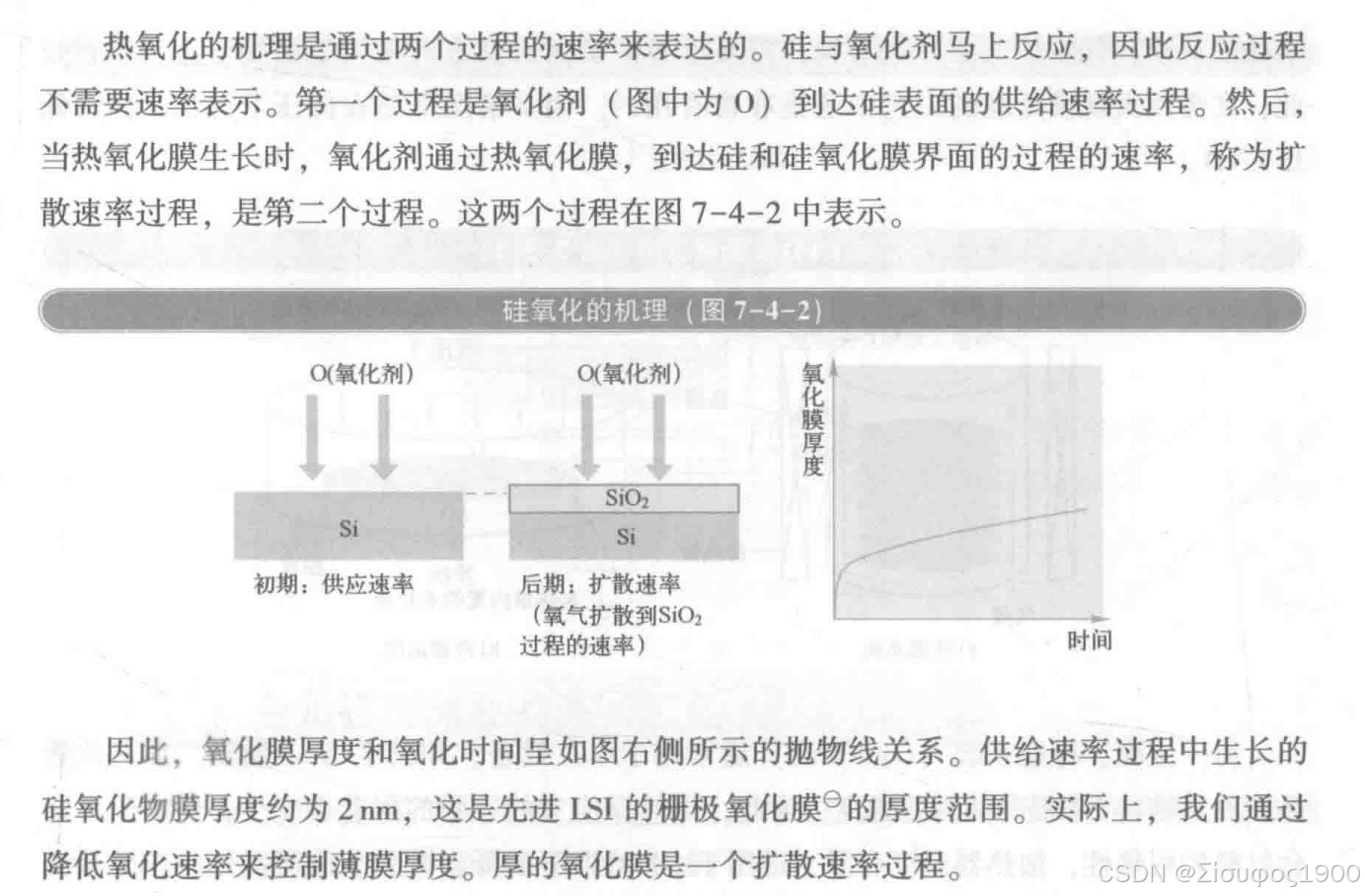

氧化硅膜机理

三、化学气相沉积 (CVD)

原理

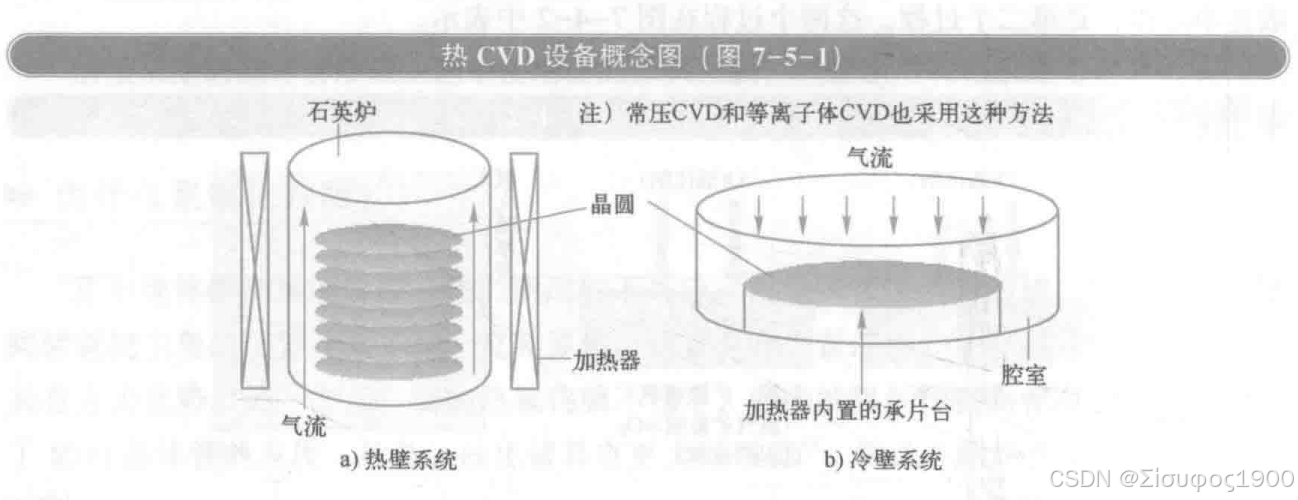

热CVD是一种最基本的CVD方法,它通过热分解原料气体形成源,并最终沉积到晶圆上形成薄膜。温度的施加有两种方法。一种是从反应炉(通常使用耐热性好的石英炉)外部加热晶圆的类型,称为热壁系统(HotWal)。前面所述的氧化炉也是这种类型的。如图所示,这种方式可以处理大量晶圆,但由于温度不会迅速上升因此处理时间会更长。此外,薄膜也会附着在反应炉上,成为难题。再者,由于气体垂直于晶圆流动,气体从上面开始消耗,需要沿着炉子的长度方向来调整温度分布。尽管如此,在需要大规模处理的工艺中还是非常有用的。很多情况下是在低压下沉积,称为低

压 CVD。

示意图

另一方面,冷壁系统(ColdWall)通常用于单片设备,如图7-5-1所示,加热放置

晶圆的承物台。来提高晶圆的温度。为此,虽然反应室的薄膜的附着会变少,但由于承物

台材料的耐热性,加热器温度有限,适用于500℃以下的低温成膜。前面提到的热壁系统

适用于500℃或更高温度的沉积。因为是单片品圆处理,处理时间很短,但如果数量很大

则要花费更长的时间。常压CVD和等离子体CVD也是这种方式,当然,有时在低压下

沉积。

四、物理气相沉积 (PVD)=等离子沉积

原理

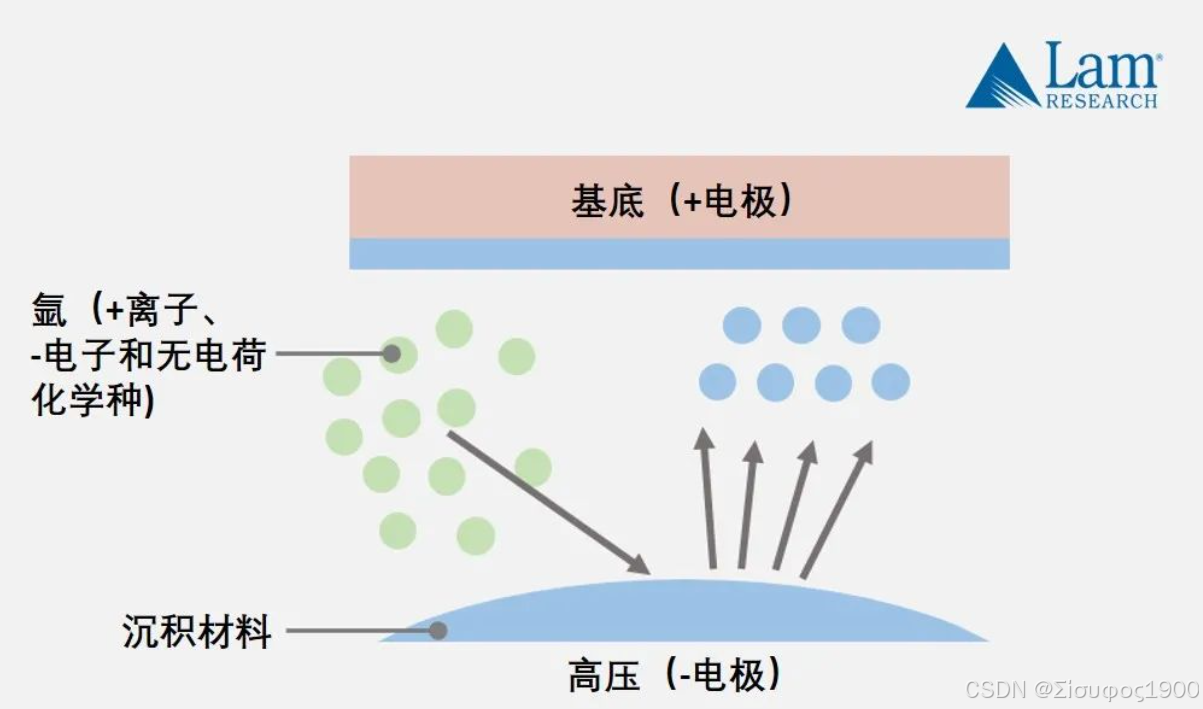

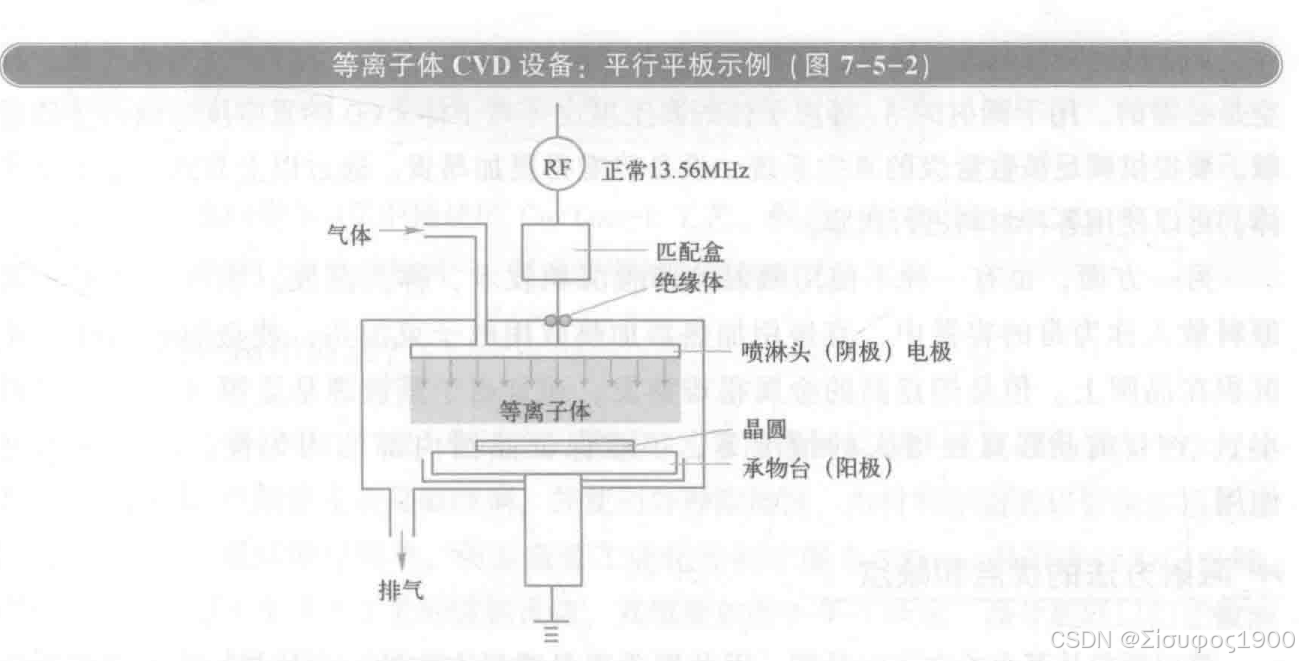

等离子CVD的优点是原料气体被等离子分解,因此可以保持较低的成膜温度。晶圆是放置在阳极一侧构成阳极对。最初,考虑在铝布线上形成保护膜(钝化),但现在用于各种成膜,后面介绍的 Low-k膜也可以采用等离子体 CVD。

产生等离子体的方法不限于如图7-5-2所示的平行平板电容耦合型,也有使用ECR(Electron CyclotronResonance,电子回旋共振)放电产生高密度等离子体的方法

示意图

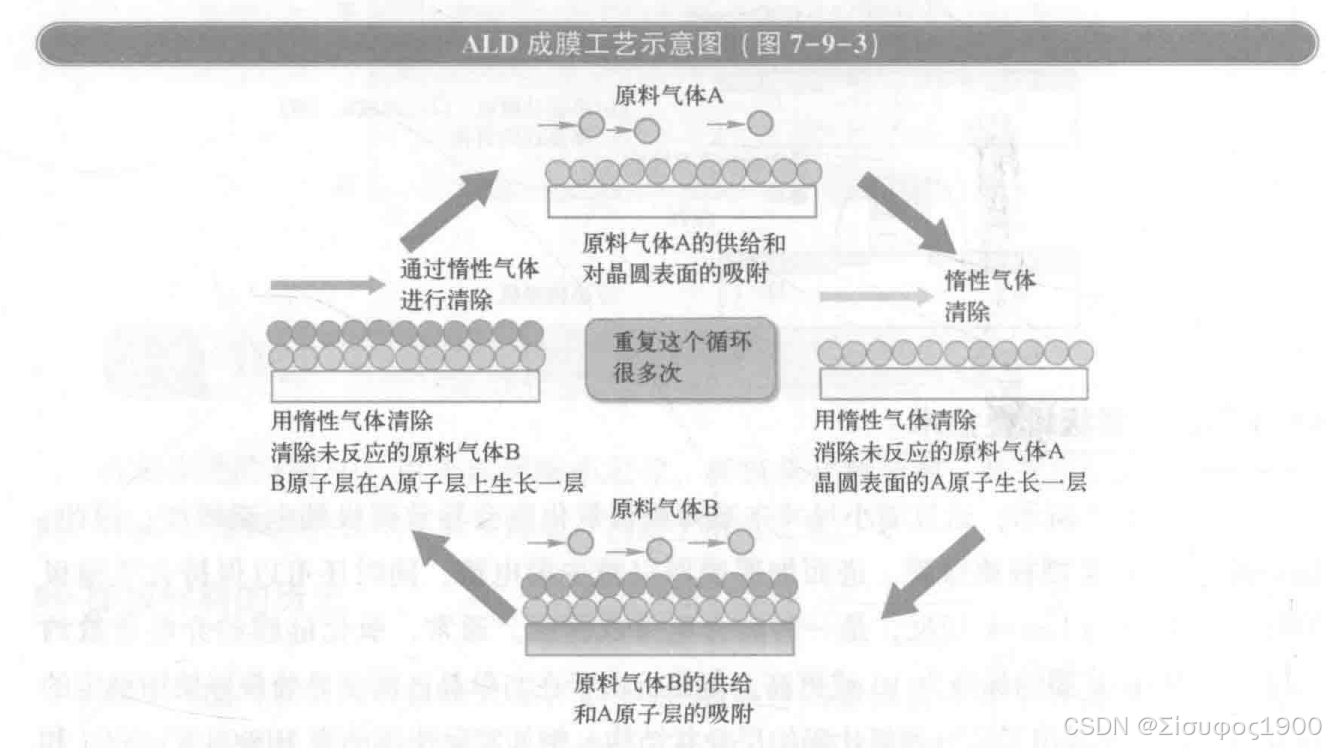

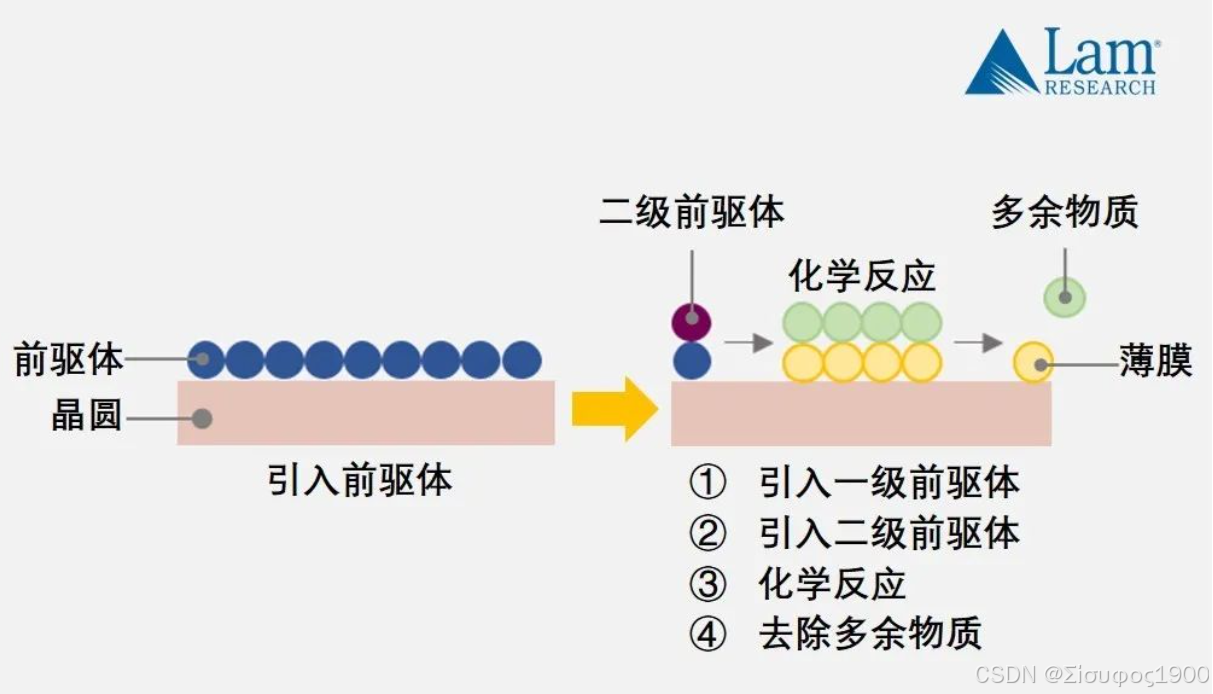

五、原子层沉积 (ALD)

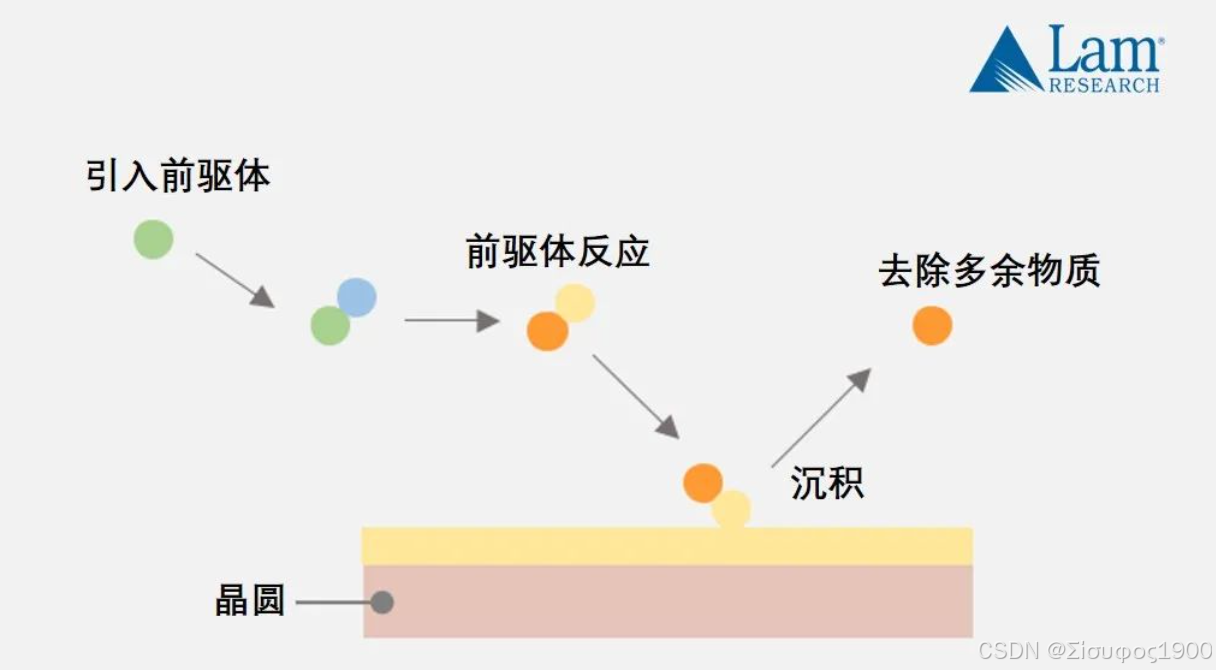

ALD 工艺主要通过重复沉积和清除(Purge)来生长薄膜。与之前描述的沉积方法最大的不同是,气体的供应比较独特。这是因为只要一次原料气体的供应量发生变化,ALD过程就不再起作用。