在FPGA开发过程中,可能会由于静电或电源短路,导致FPGA部分管脚损坏,表现的现象是程序可以下载,也可以运行,但部分损坏的管脚无法控制输出高低电平,那么如何检测FPGA管脚是否正常呢?本文介绍3种方法,最后一种方法最有效。

方法1:内部二极管测量

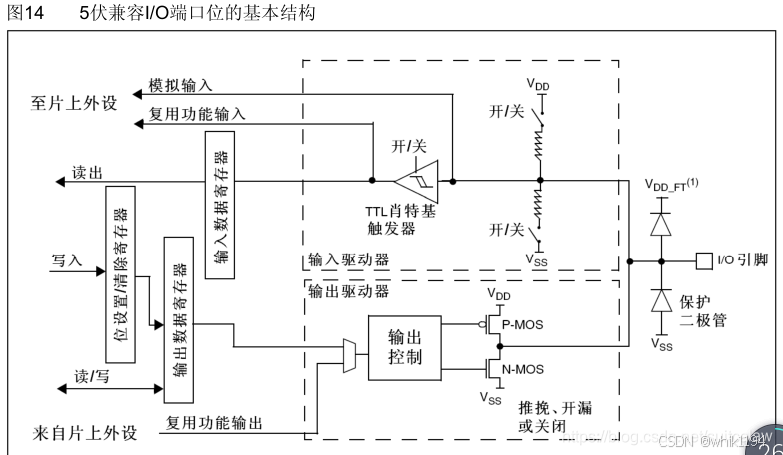

无论是FPGA还是MCU,管脚内部都分别有上下两个钳位二极管,分别连接到VCC和GND,使用万用表的二极管档可以简单判断管脚是否正常。

具体操作是:芯片断电,红色表笔接GND,黑色表笔接管脚,如果万用表显示的电压在0.7v左右,则说明该管脚到GND的保护二极管正常,若显示为零,说明二极管已经被击穿。红色表笔接VCC,黑色表笔接管脚,如果万用表显示的电压在0.7v左右,则说明该管脚到VCC的保护二极管正常,如果以上两步均正常,说明该管脚内部的两个保护二极管正常。

方法2:对地阻抗测量

断电情况下,使用万用表的电阻档,可以简单判断管脚是否正常。以Xilinx ZYNQ系列FPGA为例,其每个管脚对地阻抗大概为7.5KΩ左右,如果出现对地阻值过大或过小,则说明该管脚可能存在短路或损坏。

方法3:管脚输出变化的电平状态

设计专用测试程序,配置所有的FPGA管脚输出高低变化的电平,改变周期可以设置为1秒钟,下载程序到FPGA,使用万用表或示波器测量管脚的输出状态是否有变化。如果无变化,恒为0或1,则说明该管脚已损坏。

同理,也可以设计测试程序将所有的FPGA管脚配置成输入模式,并分别连接到LED上进行指示,外部通过跳线给定0或1的输入信号,观察FPGA的LED灯是否有变化,以此判断FPGA管脚是否正常。