直接序列扩频Matlab仿真和FPGA实现。

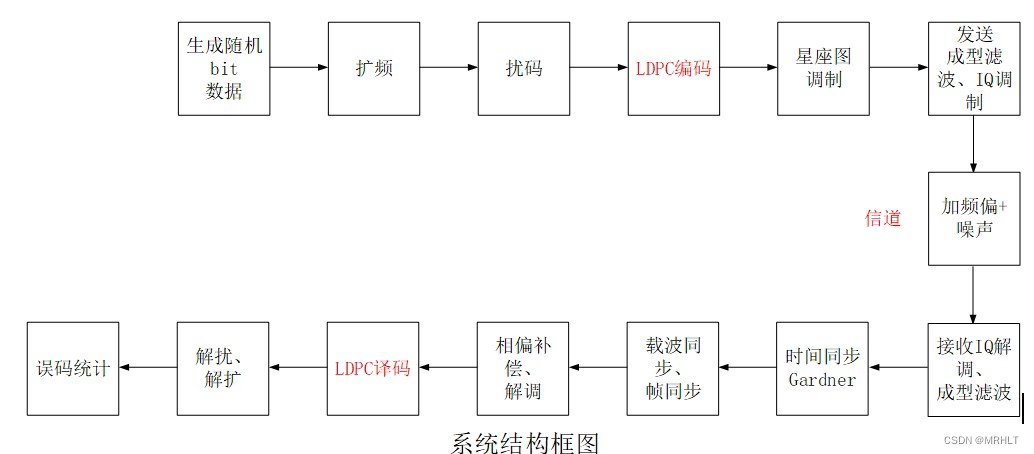

嘿,朋友们!今天咱们来聊聊直接序列扩频(Direct Sequence Spread Spectrum,DSSS),并且会通过 Matlab 进行仿真,再探讨一下如何在 FPGA 上实现它。

什么是直接序列扩频

直接序列扩频是一种常见的扩频通信技术,它将待传输的信息信号与高速率的扩频码序列相乘,从而扩展信号的频谱带宽。这样做的好处多多,比如抗干扰能力强、隐蔽性好等。

Matlab 仿真

生成扩频码

首先,我们得有一个扩频码。这里以 m 序列为例,在 Matlab 中可以轻松生成。

matlab

% 生成 m 序列

n = 5; % 寄存器阶数

feedback = [5 3]; % 反馈抽头

initial_state = [1 1 1 1 1]; % 初始状态

m_sequence = comm.MSequenceGenerator('FeedbackTapPattern', feedback, 'InitialConditions', initial_state);

spread_code = step(m_sequence, 2^n - 1);代码分析:

n定义了寄存器的阶数,阶数越高,生成的 m 序列长度就越长。feedback是反馈抽头,不同的抽头组合会生成不同的 m 序列。initial_state是寄存器的初始状态。comm.MSequenceGenerator是 Matlab 自带的 m 序列生成器,step函数用于生成指定长度的 m 序列。

生成原始信号并扩频

接下来,我们生成一个简单的原始信号,然后用扩频码对其进行扩频。

matlab

% 生成原始信号

original_signal = randi([0 1], 1, 10); % 生成 10 位随机二进制信号

% 扩频

spread_signal = kron(original_signal, spread_code); % 用 Kronecker 积进行扩频代码分析:

randi([0 1], 1, 10)生成一个长度为 10 的随机二进制信号。kron函数用于计算 Kronecker 积,它将原始信号的每个比特与扩频码相乘,从而实现扩频。

加噪声并解扩

为了模拟实际通信中的噪声干扰,我们给扩频信号加上高斯白噪声,然后再进行解扩。

matlab

% 加噪声

SNR = 10; % 信噪比(dB)

noisy_spread_signal = awgn(spread_signal, SNR);

% 解扩

despread_signal = kron(ones(1, length(original_signal)), spread_code) .* noisy_spread_signal;

despread_signal = reshape(despread_signal, length(spread_code), [])';

received_signal = sum(despread_signal, 2) > 0;代码分析:

awgn函数用于给信号添加指定信噪比的高斯白噪声。- 解扩的过程就是将接收到的扩频信号与扩频码再次相乘,然后对每个比特对应的扩频码长度内的信号求和,根据和的正负判断原始比特是 0 还是 1。

绘制波形

最后,我们把原始信号、扩频信号和解扩后的信号绘制出来,直观地看看它们的波形。

matlab

% 绘制波形

figure;

subplot(3,1,1);

stem(original_signal);

title('原始信号');

subplot(3,1,2);

stem(spread_signal);

title('扩频信号');

subplot(3,1,3);

stem(received_signal);

title('解扩后的信号');FPGA 实现

在 FPGA 上实现直接序列扩频,我们需要用到 Verilog 或 VHDL 语言。这里简单说一下实现思路。

扩频模块

扩频模块的主要功能是将输入的原始信号与扩频码相乘。以下是一个简单的 Verilog 代码示例:

verilog

module spreader (

input wire clk,

input wire reset,

input wire [0:0] original_signal,

output reg [0:0] spread_signal

);

reg [4:0] m_sequence;

always @(posedge clk or posedge reset) begin

if (reset) begin

m_sequence <= 5'b11111;

end else begin

m_sequence <= {m_sequence[3:0], m_sequence[4] ^ m_sequence[2]};

end

end

assign spread_signal = original_signal ^ m_sequence[0];

endmodule代码分析:

clk是时钟信号,reset是复位信号。m_sequence是 m 序列寄存器,通过移位和异或操作生成 m 序列。spread_signal是扩频后的信号,通过原始信号与 m 序列的第一位异或得到。

解扩模块

解扩模块的功能是将接收到的扩频信号与扩频码再次相乘,并进行积分判决。这里就不给出具体代码了,思路和 Matlab 中的解扩过程类似。

通过以上的 Matlab 仿真和 FPGA 实现,我们对直接序列扩频有了更深入的了解。希望大家在实际应用中能够灵活运用这些知识,实现更高效的通信系统!

以上就是今天的分享,咱们下次再见啦!