基于riscv指令集的五级流水线CPU设计及其验证 可以上板,且有详细说明和代码注释 基于vivado平台进行验证 包括verilog源代码、汇编验证代码、详细的说明文档(47页)以及PPT Modelsim quartus vivado都跑过,确认代码没有问题 已

本文深入剖析一套完整、可综合、可上板验证的 RISC-V 五级流水线 CPU 设计。该设计严格遵循 RISC-V RV32I 指令集规范,实现了经典的取指(IF)、译码(ID)、执行(EX)、访存(MEM)和回写(WB)五级流水线架构,并集成了关键的流水线优化技术,包括前递(Forwarding)、冒险检测(Hazard Detection)以及分支预测逻辑,确保了处理器在面对数据冒险和控制冒险时仍能高效、正确地执行指令。此外,该设计还创新性地整合了 Cache 子系统和 AHB 总线外设接口,使其不仅是一个教学模型,更是一个具备实用价值的软核处理器。

1. 核心架构:五级流水线

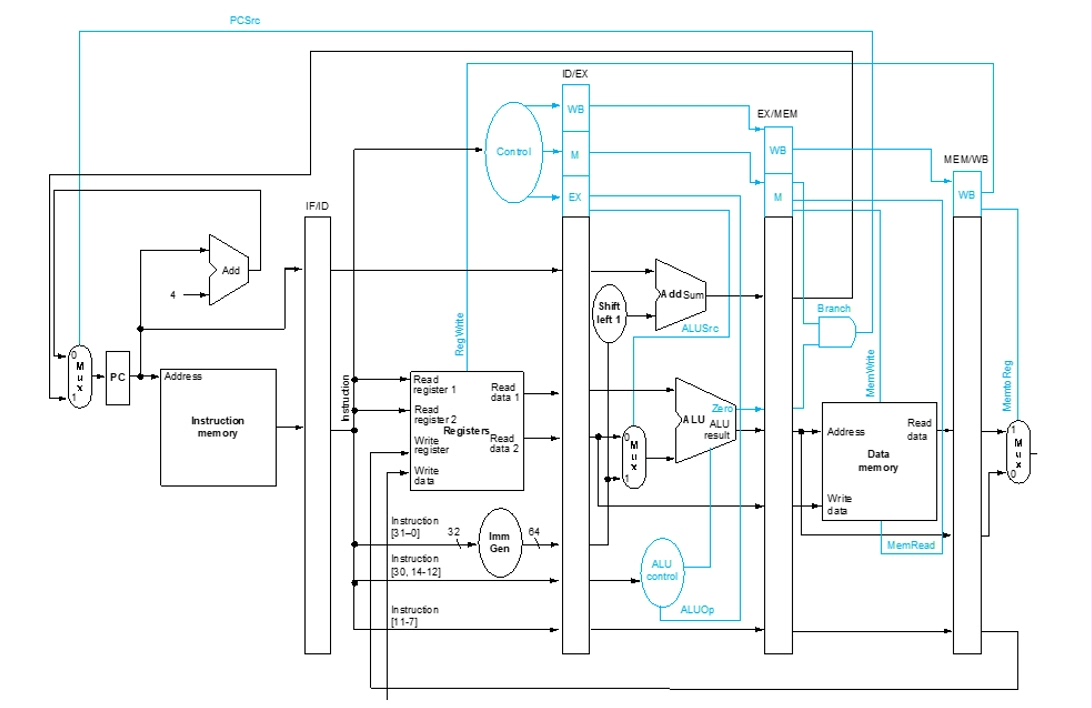

处理器的核心是其五级流水线结构,每一级由专用的流水线寄存器(IF/ID、ID/EX、EX/MEM、MEM/WB)分隔,确保指令在每个时钟周期都能向前推进一级。

- 取指(IF) :程序计数器(PC)模块根据当前指令的执行结果(顺序执行或跳转)生成下一条指令的地址。该地址被送入指令存储器(

ram_ins),在一个周期内取出对应的 32 位机器码指令。 - 译码(ID) :在此阶段,指令被解析。控制单元(

Control)根据操作码(opcode)生成一系列控制信号(如RegWrite、MemRead、ALUSrc等),这些信号将贯穿整个流水线,指导后续各阶段的操作。同时,指令中的寄存器索引(rs1, rs2, rd)被提取出来,用于从 32 个通用寄存器堆(Ram_Reg32)中读取操作数。立即数生成单元(immGen)则负责根据不同指令类型(I-type, S-type, B-type, U-type, J-type)从指令中提取并符号扩展出 32 位立即数。 - 执行(EX) :这是算术和逻辑运算的核心阶段。ALU 控制单元(

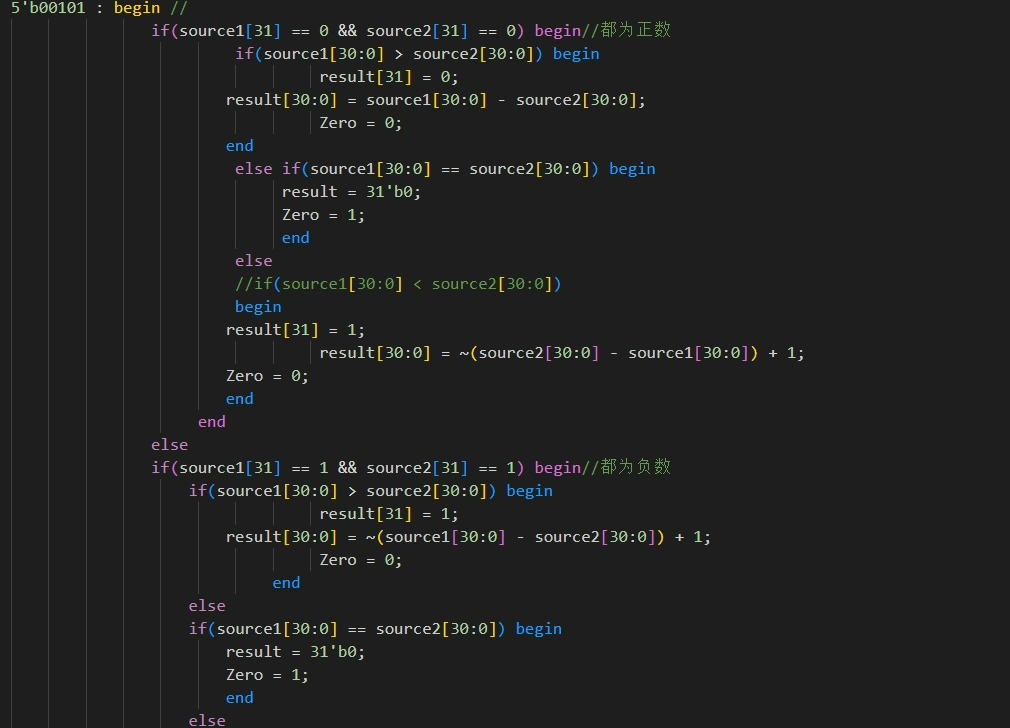

ALUCtrl)根据译码阶段传来的Func3/Func7字段和ALUOp信号,生成一个 5 位的ALUCtrl信号,精确地控制 ALU(ALU)执行何种操作(如加、减、与、或、移位、比较等)。ALU 的两个操作数分别来自寄存器堆和多路选择器,后者根据ALUSrc信号决定是使用寄存器 rs2 的值还是立即数。 - 访存(MEM) :对于 Load/Store 指令,此阶段负责与数据存储器交互。ALU 在 EX 阶段计算出的有效地址在此阶段被用作数据存储器(

ram_data)的地址。MemRead和MemWrite信号控制存储器的读写操作。对于非访存指令,此阶段通常是一个直通(bypass)。 - 回写(WB) :指令执行的最终结果被写回到寄存器堆。结果来源由多路选择器决定:可以是 ALU 的计算结果(如

add指令),也可以是访存阶段从数据存储器中读出的数据(如lw指令),或者是用于实现跳转链接(jal,jalr)的返回地址(PC+4)。

2. 关键优化:解决流水线冒险

为了保证流水线在各种指令组合下都能正确执行,设计中实现了两种核心的冒险处理机制。

- 数据冒险与前递(Forwarding) :当一条指令依赖于前一条尚未完成回写的指令的结果时,就会发生数据冒险。前递单元(

ForwardingUnit)通过监控流水线中后续指令的写回目标寄存器(WriteReg)和当前指令的操作数寄存器(Reg32Source1/2),动态地将 EX/MEM 或 MEM/WB 寄存器中的中间结果直接"前递"到 ALU 的输入端,从而避免了不必要的流水线停顿(stall)。这极大地提高了处理器的指令吞吐率。 - 控制冒险与分支预测 :对于条件分支指令(如

beq),处理器在 ID 阶段无法立即知道分支是否成功,这会导致后续取指的不确定性。该设计采用了一种简单的"静态预测+冲刷"策略。冒险检测单元(HazardDetectionUnit)在 EX 阶段得到 ALU 的比较结果(Zero信号)后,会立即判断是否发生了错误预测。如果预测错误,它会向 PC 模块发出跳转信号,并同时冲刷掉 IF/ID 和 ID/EX 流水线寄存器中的无效指令,确保处理器从正确的地址开始取指。

3. 存储系统:集成 Cache 与内存管理

该设计的一个显著特点是集成了一个直接映射(Direct-Mapped)的 Cache 子系统(Cache 和 Cacheblock)。Cache 作为 CPU 和主存之间的高速缓冲,能够显著减少因访问慢速主存而造成的性能损失。Cache 控制器实现了基本的写回(Write-Back)和写分配(Write-Allocate)策略。当发生 Cache Miss 时,控制器会自动将所需的数据块从主存加载到 Cache 中,并在必要时先将被替换的脏块(Dirty Block)写回主存。这种设计使得处理器在运行具有局部性特征的程序时性能得到大幅提升。

4. 外设扩展:AHB 总线接口

为了增强处理器的实用性,设计通过一个 AHB 从设备多路复用器(AHB_slaveMux)将 CPU 连接到外部世界。通过将地址空间的高位(如 0x8...)映射到不同的外设(如 LED、数码管、UART、按键、定时器),CPU 可以像访问内存一样通过 Load/Store 指令与这些外设进行交互。这种基于内存映射 I/O(MMIO)的设计方式,使得软件开发变得极为简单和统一。

5. 总结

这套 RISC-V 五级流水线 CPU 设计是一个功能完备、结构清晰且经过硬件验证的优秀范例。它不仅完整实现了 RV32I 指令集,还通过前递、冒险检测、Cache 和 AHB 总线等高级特性,展示了从一个基础教学模型向一个具备实用价值的软核处理器演进的关键技术路径。其模块化的代码结构和详尽的注释,为学习计算机体系结构、数字逻辑设计以及 RISC-V 生态提供了极佳的实践素材。