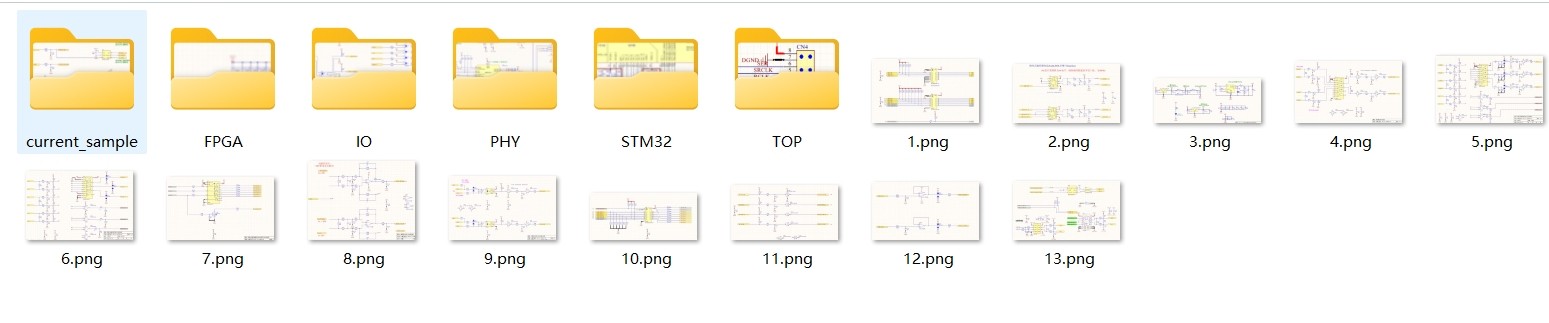

基于stm32f103和fpga的伺服驱动器资料,电流环在fpga内部处理以提升运行效率

在自动化控制领域,伺服驱动器扮演着至关重要的角色。今天咱们来聊聊基于STM32F103和FPGA搭建的伺服驱动器,尤其是将电流环放在FPGA内部处理来提升运行效率这件有趣的事儿。

STM32F103与FPGA的搭档

STM32F103是意法半导体推出的一款性价比极高的32位微控制器,它有着丰富的外设资源,比如定时器、ADC等,适合处理一些逻辑控制和数据采集任务。而FPGA(现场可编程门阵列)则以其并行处理能力强、可定制性高著称,特别适合高速信号处理。把它们俩结合起来,可谓是强强联手,能让伺服驱动器性能更上一层楼。

为啥把电流环放FPGA里

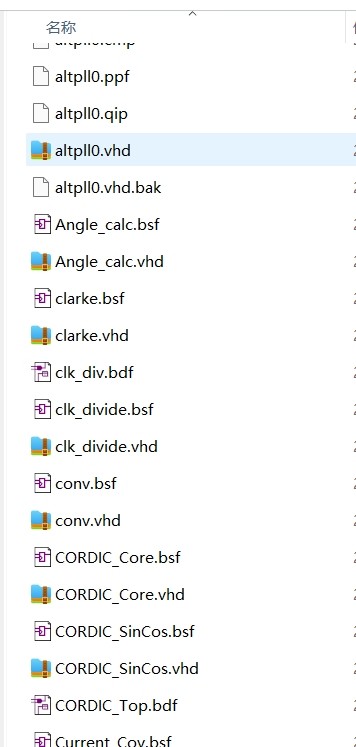

电流环是伺服驱动器控制的关键环节,它的响应速度和精度直接影响到电机的性能。传统上,电流环可能在单片机或者DSP中处理,但这些处理器大多是串行处理数据。FPGA就不一样了,它可以通过硬件描述语言(如Verilog或VHDL)来实现并行处理,大大提高电流环的处理速度,减少延迟,从而提升整个伺服驱动器的运行效率。

FPGA里的电流环代码示例(以Verilog为例)

verilog

module current_loop (

input wire clk,

input wire rst,

input wire [15:0] current_sample,

input wire [15:0] current_reference,

output reg [15:0] pwm_duty_cycle

);

reg [15:0] error;

reg [31:0] integral;

reg [15:0] p;

reg [31:0] i;

reg [15:0] d;

reg [15:0] last_error;

// 比例系数

parameter KP = 16'd100;

// 积分系数

parameter KI = 32'd1000;

// 微分系数

parameter KD = 16'd10;

always @(posedge clk or posedge rst) begin

if (rst) begin

error <= 16'd0;

integral <= 32'd0;

p <= 16'd0;

i <= 32'd0;

d <= 16'd0;

last_error <= 16'd0;

pwm_duty_cycle <= 16'd0;

end else begin

// 计算误差

error = current_reference - current_sample;

// 比例环节

p = error * KP;

// 积分环节

integral = integral + error;

i = integral * KI;

// 微分环节

d = (error - last_error) * KD;

// 计算PWM占空比

pwm_duty_cycle = (p + (i >> 16) + d) >> 4;

last_error = error;

end

end

endmodule代码分析

- 模块定义 :

module currentloop**定义了一个名为currentloop的模块,它有输入信号clk(时钟信号)、rst(复位信号)、currentsample*(电流采样值)、current*reference(电流参考值),输出信号pwmdutycycle(PWM占空比)。 - 寄存器定义 :声明了一些寄存器来存储中间变量,像

error存误差,integral存积分值,p、i、d分别存比例、积分、微分项,last_error存上一次的误差。 - 参数定义 :设置了比例系数

KP、积分系数KI和微分系数KD,这些系数可以根据实际情况调整,以优化电流环的控制效果。 - always块:在时钟上升沿或者复位信号有效时触发。复位时,将所有寄存器清零。正常运行时,计算电流误差,然后分别算出比例、积分、微分项,最后综合得到PWM占空比,用来控制电机电流。

STM32F103与FPGA的协作

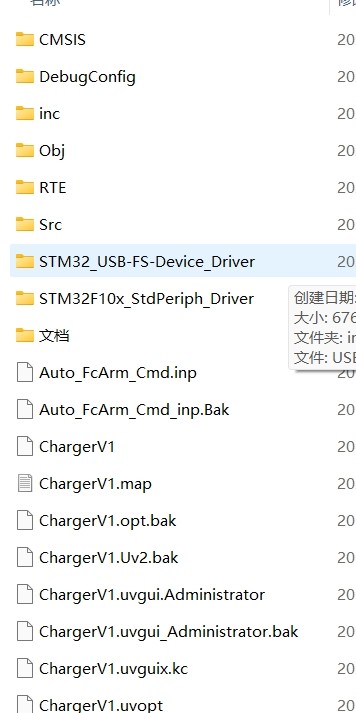

STM32F103负责采集电机的各种参数,比如位置、速度等信息,然后将电流参考值发送给FPGA。FPGA处理完电流环后,把生成的PWM信号反馈给STM32F103,由STM32F103进一步处理和输出,驱动电机运转。在这个过程中,STM32F103和FPGA分工明确,紧密配合,实现了伺服驱动器高效稳定的运行。

通过将电流环放在FPGA内部处理,并结合STM32F103强大的控制能力,我们成功打造出一款性能卓越的伺服驱动器。这种组合不仅提升了运行效率,也为自动化控制领域带来了更多可能性。希望这篇博文能给大家在相关项目开发中带来一些启发。