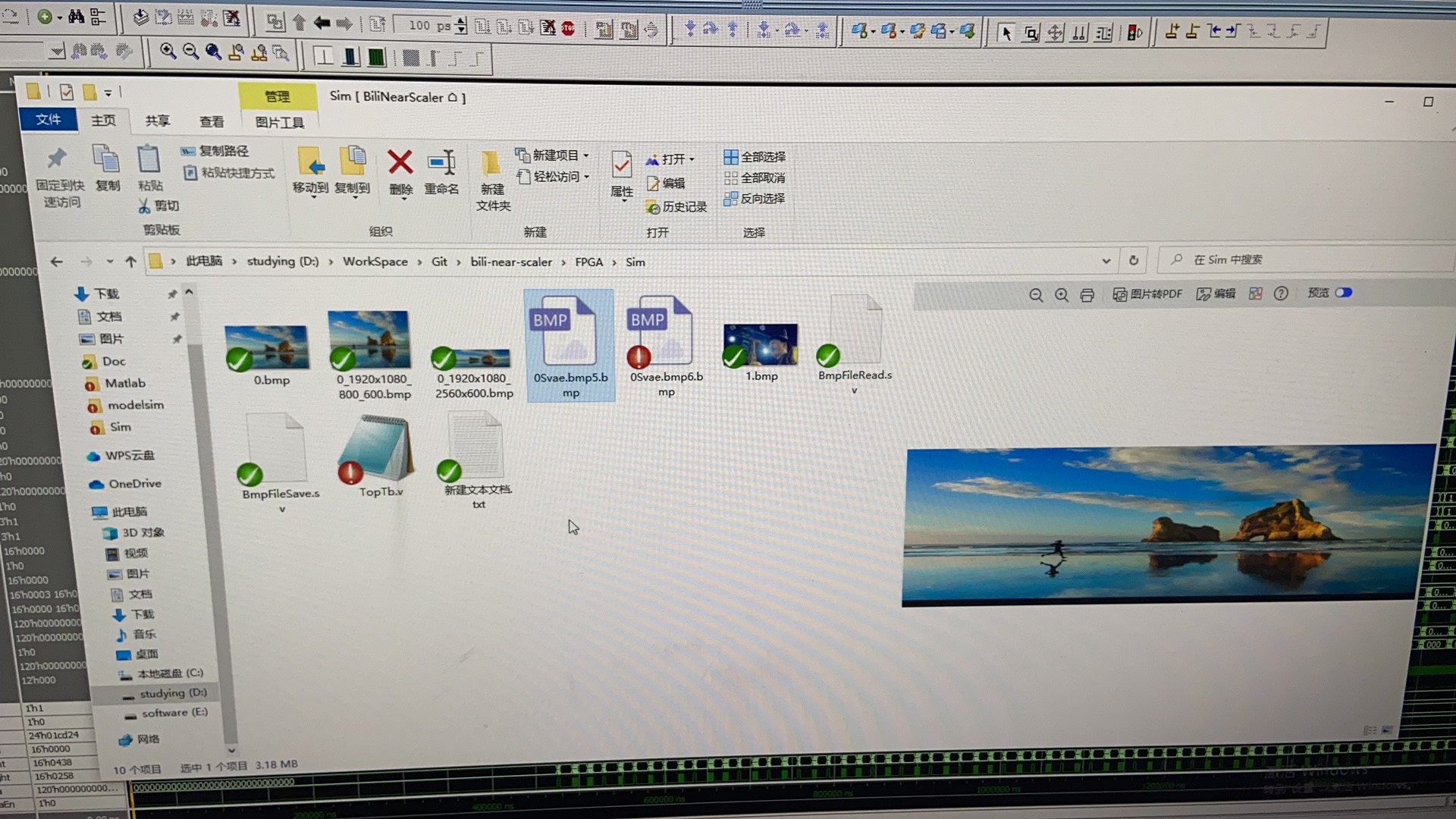

基于fpga的视频缩放算法,支持4k2k输入,4k2k输出,缩放参数可控。

最近在折腾一个FPGA视频处理项目,发现市面上的缩放方案要么延迟太高,要么资源占用爆炸。自己动手撸了个支持4K60帧的缩放架构,参数还能实时调整,实测效果居然比某些商业IP核还流畅。

整个架构分三层走:输入处理、缩放核心、输出调度。先看输入缓存部分,这里用AXI-Stream配合双口BRAM做乒乓操作。关键是要处理不同步的时钟域,特别是当输入分辨率变化时:

verilog

always @(posedge vid_clk) begin

if (vblank) wr_ptr <= 0;

else if (de_in) begin

line_buffer[wr_ptr] <= pixel_in;

wr_ptr <= wr_ptr + 1;

end

end

// 跨时钟域同步用格雷码转换

wire [15:0] rd_ptr_gray = (rd_ptr >> 1) ^ rd_ptr;

sync_cell #(.WIDTH(16)) sync_rd_ptr (.clk(vid_clk), .in(rd_ptr_gray), .out(synced_rd));缩放核心里面最吃资源的是插值算法。双线性插值虽然效果一般,但胜在硬件友好。这里用定点数运算替代浮点,省了DSP单元:

systemverilog

logic [17:0] dx_fix = phase_x[7:0] << 10; // 10位小数精度

logic [17:0] dy_fix = phase_y[7:0] << 10;

// 四个相邻像素的权重计算

assign w0 = (18'sh400 - dx_fix) * (18'sh400 - dy_fix);

assign w1 = dx_fix * (18'sh400 - dy_fix);

assign w2 = (18'sh400 - dx_fix) * dy_fix;

assign w3 = dx_fix * dy_fix;

// 最终像素计算(右移20位相当于除以2^20)

assign pixel_out = (p0*w0 + p1*w1 + p2*w2 + p3*w3) >> 20;参数控制这块做了动态重配置接口,通过APB总线实时改缩放系数。注意系数更新要和垂直消隐同步,不然画面会撕裂:

c

// 缩放系数寄存器组

typedef struct {

uint32_t h_ratio;

uint32_t v_ratio;

uint8_t sharpness;

} zoom_params_t;

// APB从机处理

always_ff @(posedge pclk) begin

if (psel && penable) begin

if (paddr == 0x10) params.h_ratio <= pwdata;

if (paddr == 0x14) params.v_ratio <= pwdata;

if (paddr == 0x18) params.sharpness <= pwdata[7:0];

end

end实测在Xilinx ZU7EV上跑,资源占用比想象中低------DSP用不到30%,BRAM占45%,关键是延迟控制在3行以内。处理4K@60Hz视频时功耗稳定在8W左右,比GPU方案省电得多。

调试时踩过几个坑:相位累加器的精度不够会导致画面抖动,后来改成20位定点才解决;边缘处理最初直接复制边界像素,结果出现黑边,改成镜像采样后自然多了。

这个架构现在支持从0.5x到8x的无级缩放,配合锐化参数可以调出不同风格。最近试着接医疗内窥镜视频流,连组织纹理都清晰可见。下一步打算加个AI超分模块,不过得先搞定TensorFlow Lite到RTL的转换...