目录

[1.1. 滤波(Filtering)------ "电路的筛子"](#1.1. 滤波(Filtering)—— “电路的筛子”)

[1.2. 去耦/旁路(Decoupling/Bypass)------ "局部小金库"](#1.2. 去耦/旁路(Decoupling/Bypass)—— “局部小金库”)

[1.3. 延时/定时(Timing)------ "电路的沙漏"](#1.3. 延时/定时(Timing)—— “电路的沙漏”)

[1.4. 耦合/隔直(Coupling/DC Blocking)------ "只传话,不过人"](#1.4. 耦合/隔直(Coupling/DC Blocking)—— “只传话,不过人”)

[第一部分:为什么图中选了 0.1µF?](#第一部分:为什么图中选了 0.1µF?)

[1. 选容值 (Value) ------ 看用途](#1. 选容值 (Value) —— 看用途)

[2. 选耐压 (Voltage Rating) ------ 也就是"降额"](#2. 选耐压 (Voltage Rating) —— 也就是“降额”)

[3. 选封装 (Package/Size)](#3. 选封装 (Package/Size))

1.电容的作用

电容(Capacitor)是电路中最基础、最重要的元件之一。如果把电流比作水流,电容就是一个"蓄水池"或者"减震器"。

在电子设计中,电容的作用千变万化,但归根结底主要有以下 4 大核心作用。结合你的 FPGA 复位电路(C128),我们可以具体来看:

1.1. 滤波(Filtering)------ "电路的筛子"

这是电容最常见的用途。

-

原理: 电容有一个特性叫"通高频,阻低频"。高频的噪声信号(像毛刺、静电干扰)很容易通过电容流到地(GND),而直流信号(比如稳定的 3.3V)过不去。

-

作用: 把电路里那些不干净的"杂质"(噪声)过滤掉,只留下干净的信号或电源。

-

场景: 在复位引脚上,

C128会把空气中感应到的瞬间尖峰电压(比如有人在旁边打手机产生的干扰)直接短路到地,防止 FPGA 莫名其妙地误复位。

1.2. 去耦/旁路(Decoupling/Bypass)------ "局部小金库"

这是你在每一个芯片的电源引脚旁边都会看到的电容(通常是 0.1µF)。

-

原理: 芯片工作时,电流忽大忽小(一下要吃很多电,一下又不吃)。电源线太长,供电反应不过来。

-

作用: 电容就像一个这就近的"临时蓄水池"。

-

当芯片突然需要大电流时,电容先放电给它吃(补水)。

-

当电压高了,电容就充电存起来(蓄水)。

-

-

效果: 保证芯片电压稳定,不会因为电压波动而死机。

对于FPGA的电源轨则是有特殊的要求:

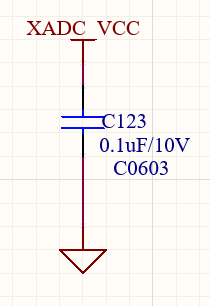

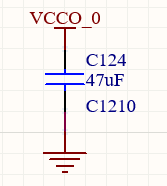

这张原理图显示的是 FPGA 的 VCCO_0 (Bank 0 的 I/O 电压)电源引脚上的一个电容 C124 (47uF, 1210封装) 。选用 47uF 这么大容量的电容,主要有以下几个核心原因:

1. 它是"大容量去耦电容" (Bulk Decoupling Capacitor)

在 FPGA 的电源设计中,电容通常分为两类,它们的职责不同,需要搭配使用:

小电容 (如 0.1uF, 0.47uF): 负责滤除高频噪声,响应速度极快,通常紧挨着芯片引脚放置(如你上一张图里的 C122)。

大电容 (如 47uF, 100uF): 负责提供瞬态电流 和滤除低频纹波。这就是 C124 的角色。

2. Xilinx 官方设计指南的推荐 (UG483)

您的芯片型号 xc7k325t 属于 Xilinx Kintex-7 系列。根据 Xilinx 7 系列 FPGA 的 PCB 设计指南 (UG483 - 7 Series FPGAs PCB Design Guide),官方对 VCCO 电源轨的去耦有明确建议:

推荐规范: 每个 Bank 通常需要配置一个 47uF 或 100uF 的大电容作为"Bulk电容",以及若干个小电容(如 4.7uF 或 0.47uF)。

这个 47uF 电容就像一个**"本地小水库"**。当 FPGA 内部逻辑突然翻转,或者多个 I/O 口同时输出高电平时,电流需求会瞬间激增。远处的电源模块(Regulator)反应不过来,这时候必须靠这个 47uF 电容里的存电先顶上去,防止电压瞬间跌落(Voltage Sag),导致系统复位或工作异常。

3. VCCO_0 的特殊性(配置 Bank)

原理图中的网络名是 VCCO_0 。在 7 系列 FPGA 中,Bank 0 非常关键,它包含了所有的配置引脚(JTAG, SPI, SelectMAP 等)。

如果 VCCO_0 电压不稳,FPGA 可能无法从 Flash 加载程序,或者 JTAG 调试会断开。

因此,在这个 Bank 放一个足量的 47uF 电容是标准操作,确保配置过程极其稳定。

4. 为什么是 C1210 封装?

容量与体积的平衡: 要在陶瓷电容(MLCC)中做到 47uF 这么大的容量,同时还要保证耐压(比如 6.3V 或 10V)和材质(通常用 X5R 或 X7R 以保证温漂小),0603 或 0805 封装通常做不到(或者太贵、降额太严重)。

低 ESR: 相比于以前常用的钽电容(黄色长方体),现代设计更倾向于使用 1210 封装的大容量陶瓷电容,因为它们的等效串联电阻 (ESR) 更低,对电源纹波的吸收效果更好。

总结

这个 47uF / 1210 电容的作用是 作为 VCCO_0 电源轨的本地储能池。它严格遵循了 Xilinx Kintex-7 的官方硬件设计规范,目的是为了应对低频瞬态电流需求,保证 FPGA 核心配置 Bank (Bank 0) 的电压绝对稳定。

1.3. 延时/定时(Timing)------ "电路的沙漏"

这是RC电路的原理。

-

原理: 电容充电和放电是需要时间的,这个时间由电阻(R)和电容(C)的大小决定(

)。

-

作用:

-

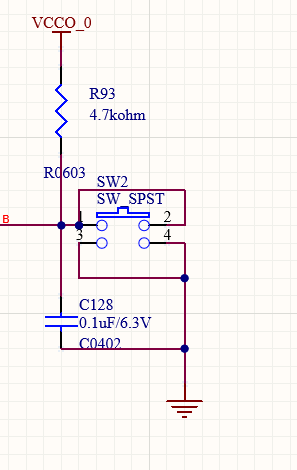

按键消抖(Debouncing): 当你按下 SW2 时,机械弹片会发生几毫秒的物理抖动。如果没有电容,FPGA 会读到"101010101"好几次变化。有了电容,电压会缓慢下降或上升,把抖动"平滑"掉,变成一个干净的信号。

-

上电复位: 刚通电时,电容需要时间充电,这能让复位信号保持低电平一小会儿,等电源彻底稳定了再释放复位,确保机器安全启动。

-

1.4. 耦合/隔直(Coupling/DC Blocking)------ "只传话,不过人"

这在音频和射频电路中很常见。

-

原理: 电容是断开的,直流电(DC)流不过去,但是交流信号(AC,比如声音信号、数据信号)可以通过感应过去。

-

作用: 连接两个电路模块。让交流信号传过去,但把两边的直流电压隔离开,互不影响。

-

口诀: "隔直通交"(隔绝直流,通过交流)。

2.实例

这是一个非常经典的 按键消抖(Debouncing) 和 抗干扰滤波 电容。

针对图中的 C128 (0.1µF / 6.3V / 0402) 以及通用的电容选型,可以分两部分来讲:

第一部分:为什么图中选了 0.1µF?

在这个电路(FPGA 复位按键)中,电容的作用有两个:

1.滤除高频噪声(防误触):

FPGA 的复位引脚 PROGRAM_B 非常敏感。如果空气中有电磁干扰(比如手机信号、静电),引脚上可能会感应出一个极短的尖峰电压。如果没有电容,FPGA 可能会误以为你要复位,导致死机。

0.1µF (100nF) 是电子设计中最标准的"高频滤除值",它能把这些极短的毛刺直接短路到地。

2.按键硬件消抖(Debouncing):

机械按键按下时,金属弹片会"抖动",在几毫秒内产生一连串的断断续续的信号(像敲鼓一样)。

- 电容配合电阻

R93(4.7kΩ) 组成了一个 RC 延时电路。 - 计算公式:

。

- 效果: 虽然 0.47ms 的时间常数对于彻底消除人手按键的抖动(通常需要 10ms~20ms)来说有点偏小,但它能平滑掉最尖锐的毛刺,配合 FPGA 内部的逻辑,足以保证复位信号干净稳定。

第二部分:平时设计时,电容一般怎么选?

选电容通常看 "三要素" :容值(容量)、耐压、封装。

1. 选容值 (Value) ------ 看用途

不用死记硬背,记住这三个"黄金标准":

-

电源滤波/去耦 (Decoupling) ------ 最常用

-

标准配置: 每一个芯片的电源引脚旁边,都要放一个 0.1µF (104)。

-

大水塘: 在电源入口处,或者芯片特别耗电时,并联一个大的 10µF 或 47µF。

-

口诀:大电容滤低频(稳压),小电容滤高频(去噪)。

-

-

按键/复位电路 (RC Circuit)

-

就像你图里这样。一般选 0.1µF ~ 1µF。

-

如果是复位引脚(RESET),0.1µF 是最通用的标准值。

-

-

晶振负载 (Crystal)

- 非常小,通常在 10pF ~ 22pF 之间(具体看晶振手册)。

2. 选耐压 (Voltage Rating) ------ 也就是"降额"

这是新手最容易踩的坑。陶瓷电容(MLCC)有一个特性:电压越高,实际容量越小(DC Bias Effect)。

-

黄金法则:耐压值 >= 2倍的工作电压。

-

3.3V 电路: 至少选 6.3V 的电容(如图中所示),最好选 10V 或 16V。如果你选 4V 的电容,实际容量可能剩下一半都不到。

-

5V 电路: 选 10V 或 16V。

-

12V 电路: 选 25V 或 50V。

-

3. 选封装 (Package/Size)

-

0603 (最推荐): 手工焊接最舒服的大小,大小适中。

-

0402 (图中用的): 比较小(像沙子一样),省空间,但是手工焊接需要镊子和好眼力。手机、FPGA核心板常用。

-

0805 / 1206: 个头大,通常用于大容量电容(如 10µF, 22µF)。

总结建议

针对FPGA 复位电路:

-

C128 选 0.1µF 是非常标准且正确的工程选择(兼顾了滤噪和一定的消抖)。

-

耐压 6.3V 对于 3.3V 电源来说是"及格"的,如果物料库里有 10V 或 16V 的同规格电容,用耐压高的会更好(容量更足,寿命更长)。

以上就是本次笔记的内容。