2.6.6 Asynchronous Set/Reset Signals(异步置位和复位信号)

异步置位和复位信号不是直接受控于primary inputs,所以shift数据的时候可能出错,所以这个置位/复位信号在shift mode时候应该设置成无效。

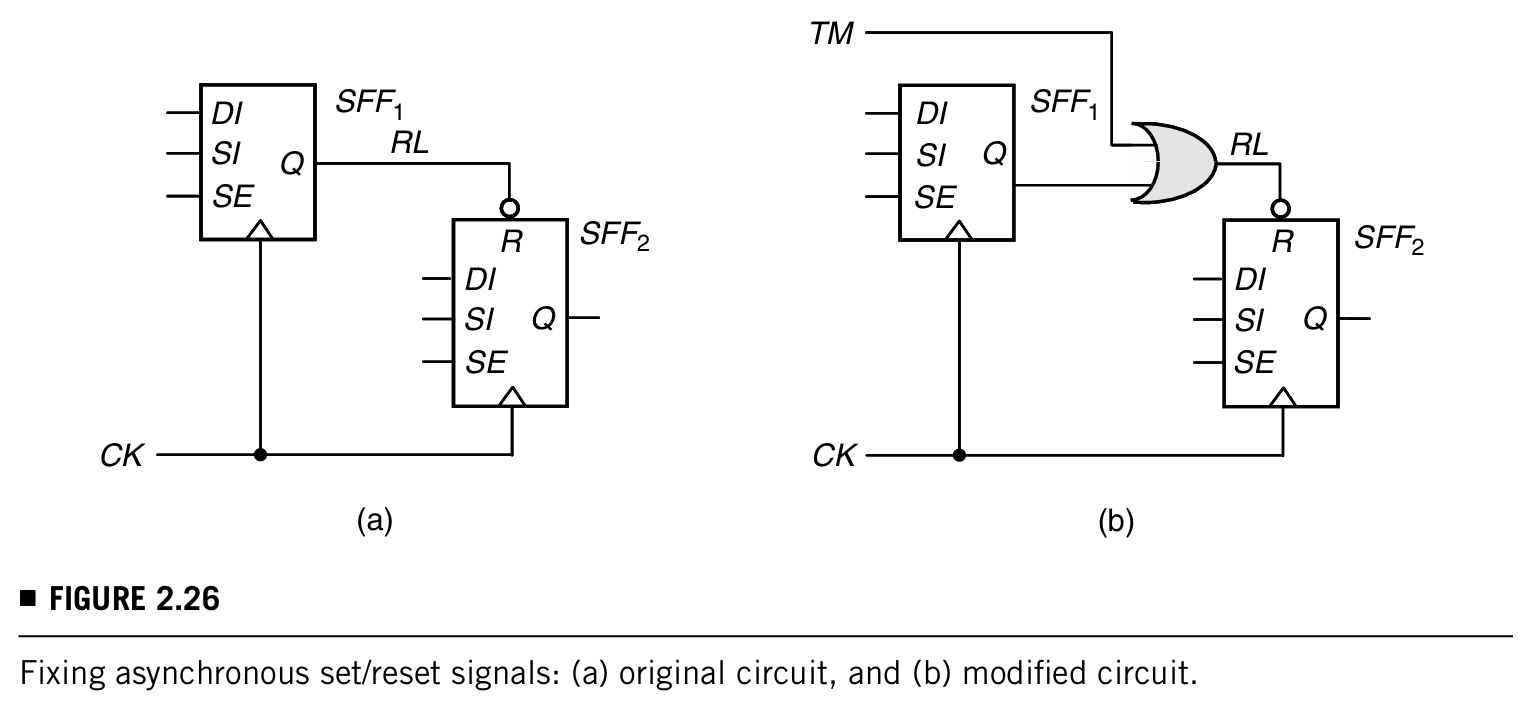

下图是个例子:

a图显示了一个异步复位信号R,异步信号通常都是被时序信号RL控制的,在测试时让异步信号无效的方法有3种:

- 用一个或门,和TM构成,整个测试过程中,TM = 1,RL就一直是1,R就不起作用。但是有个缺点就是在TM测试模式时因为异步逻辑被禁用,所以里面的故障也没法检测。

- 把TM用SE代替,那么就是shift mode下,SE = 1,异步逻辑被禁用,capture的时候还可以检测异步逻辑里面的故障。但是还有缺点就是capture的时候,时钟和异步置位/复位端口可能发生不匹配。

- 一个更好的方法,就是再开辟一个新的信号reset enable signal RE,两种模式

- RE = 1,shift和capture两个模式下异步置复位信号都无效,通过DI测试scan cell的故障

- shift mode时,RE = 1;capture mode时,RE = 0,异步置复位信号有效,不加时钟,这时候测试异步置复位逻辑

2.7 SCAN DESIGN FLOW

虽然scan design的概念不难理解,但是实际中插入scan将IC设计变成scan design还是需要非常仔细。有两个大原则:

- 不影响电路的正常功能

- scan测试能成功地被实现

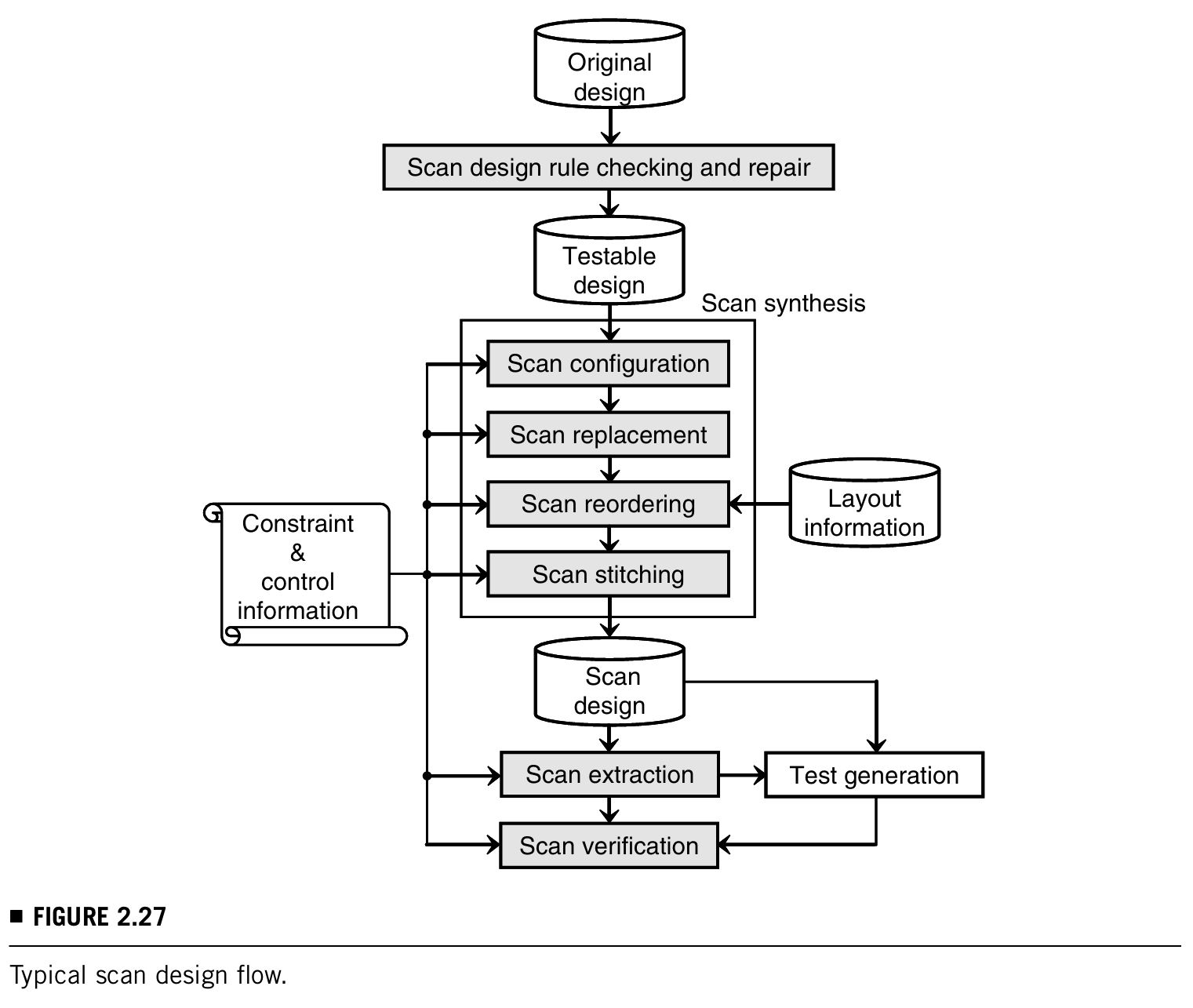

一个时序电路的典型设计flow如下图(从Original到Testable到Scan的过程):

scan design rule checking and repair :要在综合前的RTL设计做一次,也要在综合后的网表设计(netlist)阶段做一次保证都修正了

scan synthesis:把testable design转化为scan design

scan extraction:确定scan chain的数量,并提取为了ATPG准备的scan chains的scan架构

scan verification:对shift和capture操作验证期待的响应能匹配电路的行为

每个步骤会在后面的小节中细说。

2.7.1 Scan Design Rule Checking and Repair(DRC和repair)

除了scan design rules(前面有一节专门介绍)要做check和repair外,特定的时钟架构也需要在at-speed delay testing中加入。

两种操作模式下的时钟特点如下:

- shift mode:所有scan cell的时钟都来自external pins,所以相邻的scan cell的时钟偏差要被很适当地控制以成功完成shift操作

- capture mode:

- 在同一个时钟域里,完成DRC和repair后基本能保证data path的正确起始和终止

- 但是在不同时钟域里,就需要再额外注意时钟的控制以保证capture的正确执行,因为两个时钟域的时钟偏差一般都很大,而且时钟偏差会大于data path dalay,所以提出了下面的要求:

- staggered clocking scheme

- one-hot clocking scheme

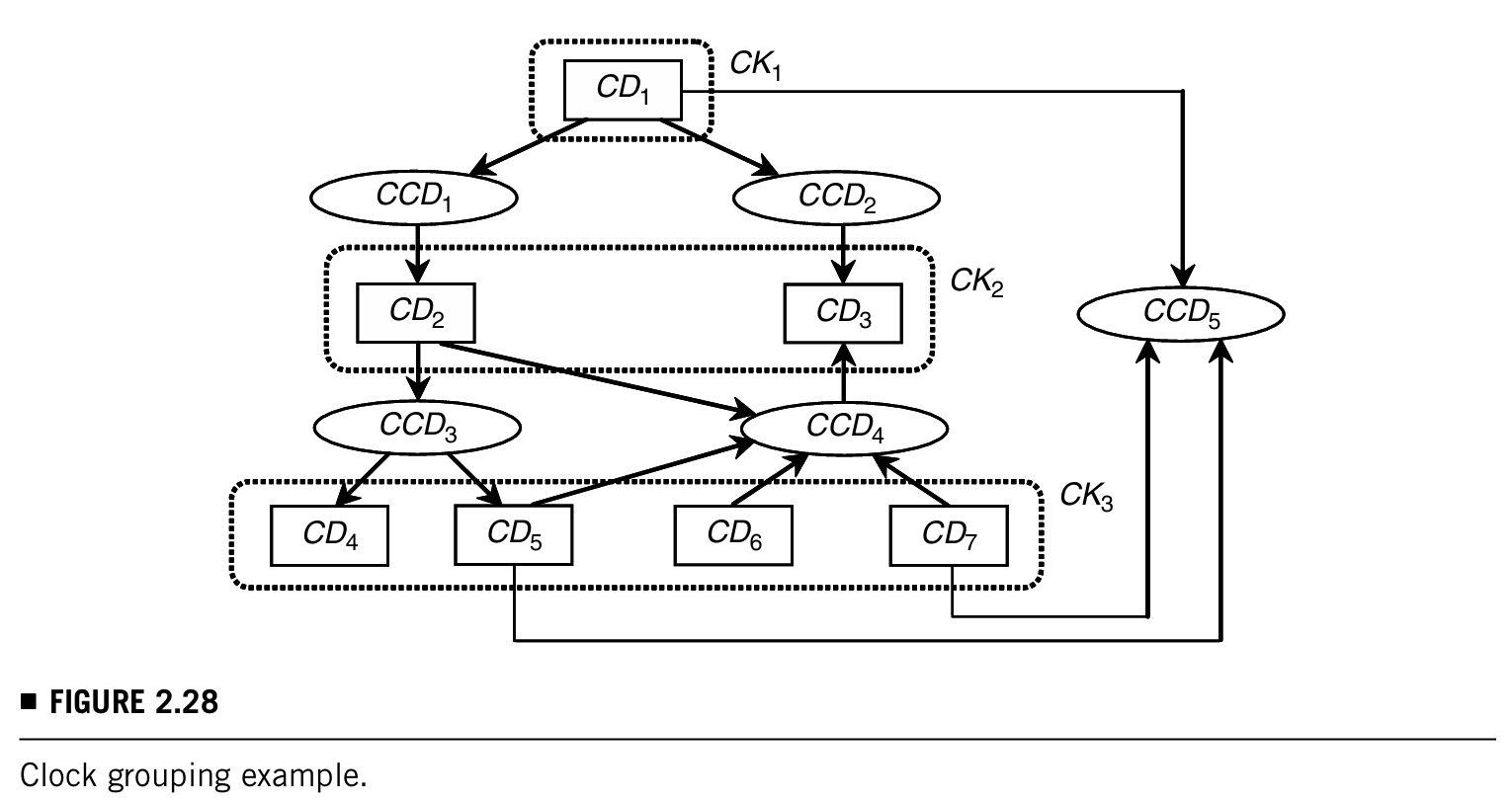

- Clock grouping:针对独立的或者内部无互联的时钟,给他们分组让他们同时工作,下面就是个例子:

图中有7个时钟域clock domains (CD1 ∼ CD7) ,5个跨时钟域的data paths (CCD1 ∼ CCD5)。其中CD2和CD3互相独立,可以被CK2同步控制;CD4和CD7互相独立,可以被CK3同步控制,所以capture时可以分为三组时钟,而不是7个独立的时钟。

2.7.2 Scan Synthesis

scan synthesis的任务就是把testable design转化为scan design,这两种设计能保证不影响original design的功能,有两个工具可以用来证实前后设计没变:

- Static analysis tools

- equivalency checkers

scan synthesis这个操作在整个流程中的位置:

- 早期,1990s,是在逻辑综合(RTL设计综合之后变为gate-level netlist)之后用一个单独的scan综合工具

- 现在,是合并到逻辑综合里面去,直接出来就是scan design的netlist,这叫one-pass

synthesis 或者single-pass synthesis。

scan synthesis flow有四个独立的步骤(图中也有,分小节细讲):

- scan configuration

- scan replacement

- scan reordering

- scan stitching