Renesas RH850-U2A中断系统介绍-3

- [1 Interrupt Function Registers](#1 Interrupt Function Registers)

- [2 Interrupt Function Registers Overview](#2 Interrupt Function Registers Overview)

-

- [2.1 ISPR --- Priority of Interrupt being Serviced](#2.1 ISPR — Priority of Interrupt being Serviced)

- [2.2 IMSR --- Interrupt Mask Status](#2.2 IMSR — Interrupt Mask Status)

- [2.3 ICSR --- Interrupt Control Status](#2.3 ICSR — Interrupt Control Status)

- [2.4 INTCFG --- Interrupt Function Setting](#2.4 INTCFG — Interrupt Function Setting)

- [2.5 PLMR --- Interrupt Priority Level Mask](#2.5 PLMR — Interrupt Priority Level Mask)

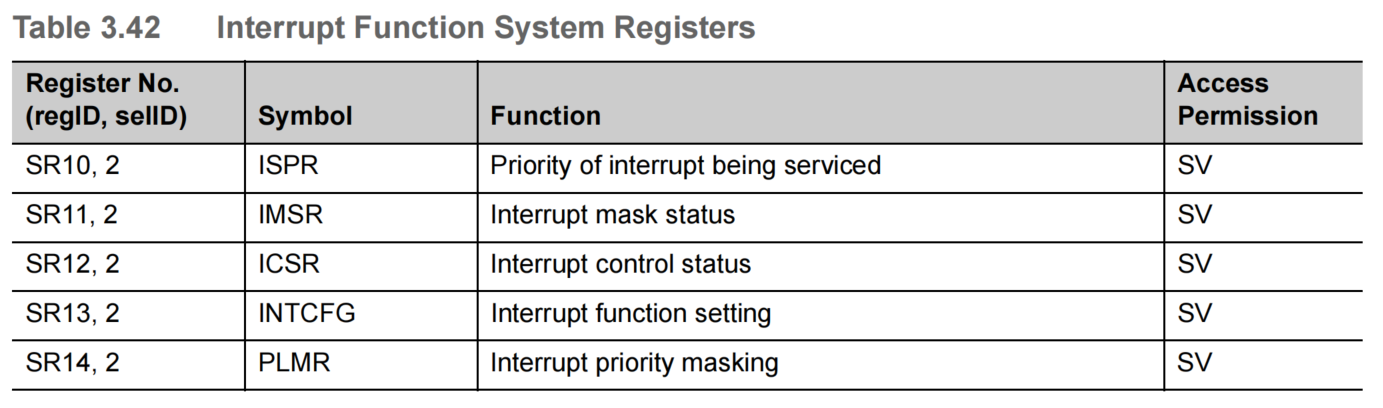

1 Interrupt Function Registers

(a) Interrupt Function System Registers

Interrupt function system registers are read from or written to by using the LDSR and STSR instructions and specifying the system register number, which is made up of a register number and selection ID.

2 Interrupt Function Registers Overview

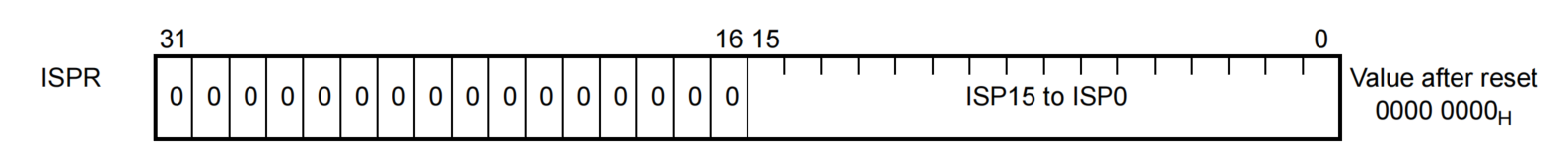

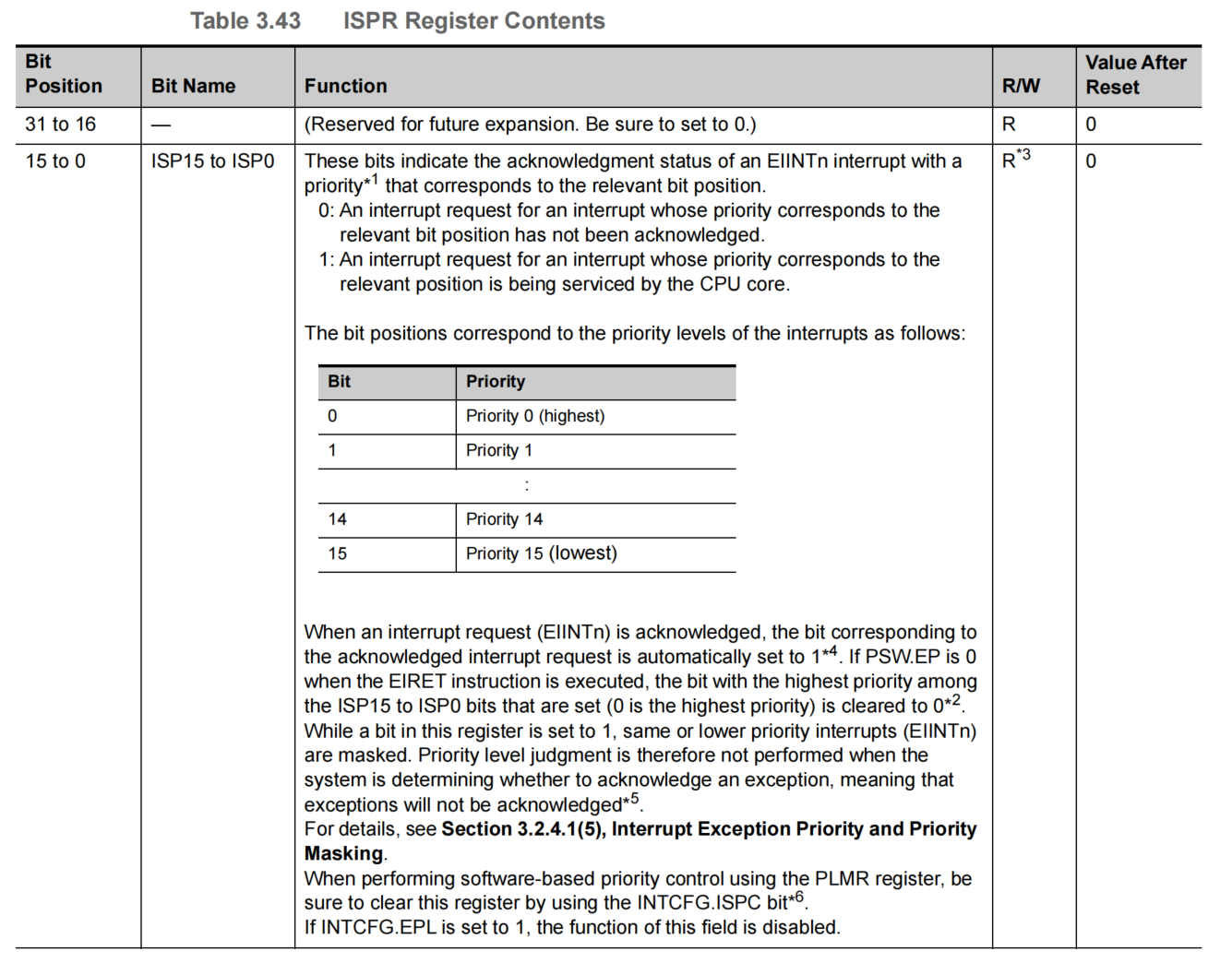

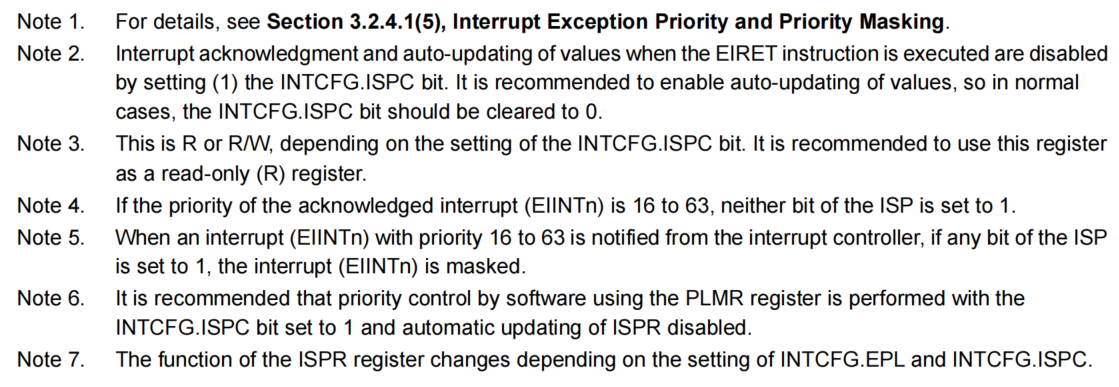

2.1 ISPR --- Priority of Interrupt being Serviced

The ISPR register holds the interrupt priority of the EI level interrupt (EIINTn) being processed by the CPU for each priority, priority ceiling by interrupt priority is performed when multiplexed interrupts occur.

For the ISPR register, the function becomes enabled if INTCFG.EPL is cleared to 0. When INTCFG.EPL is set to 1, the function of the ISPR register is disabled and acknowledgment of interrupt (EIINTn) is not controlled.

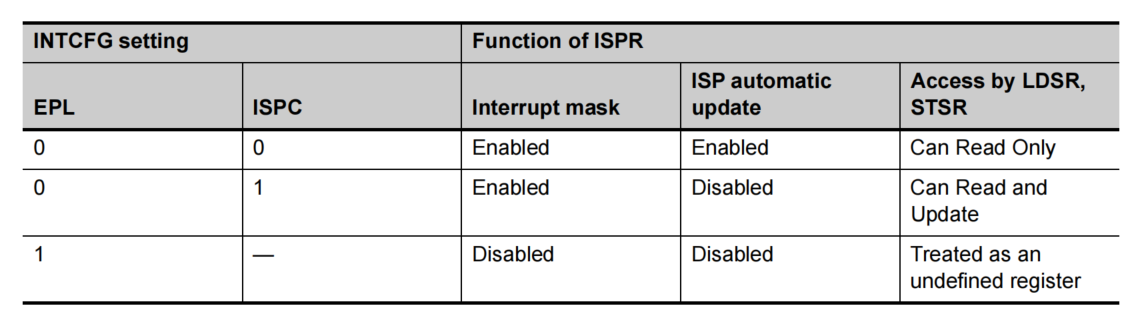

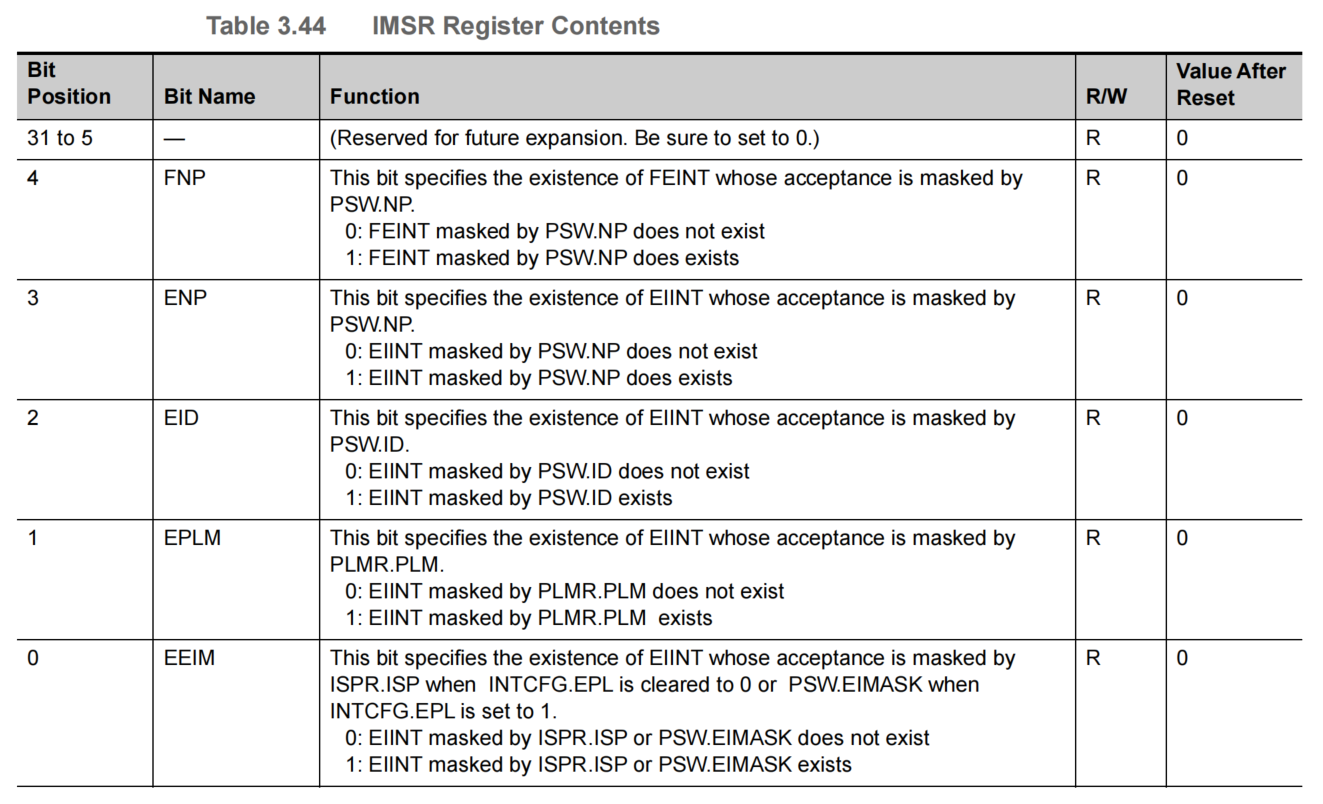

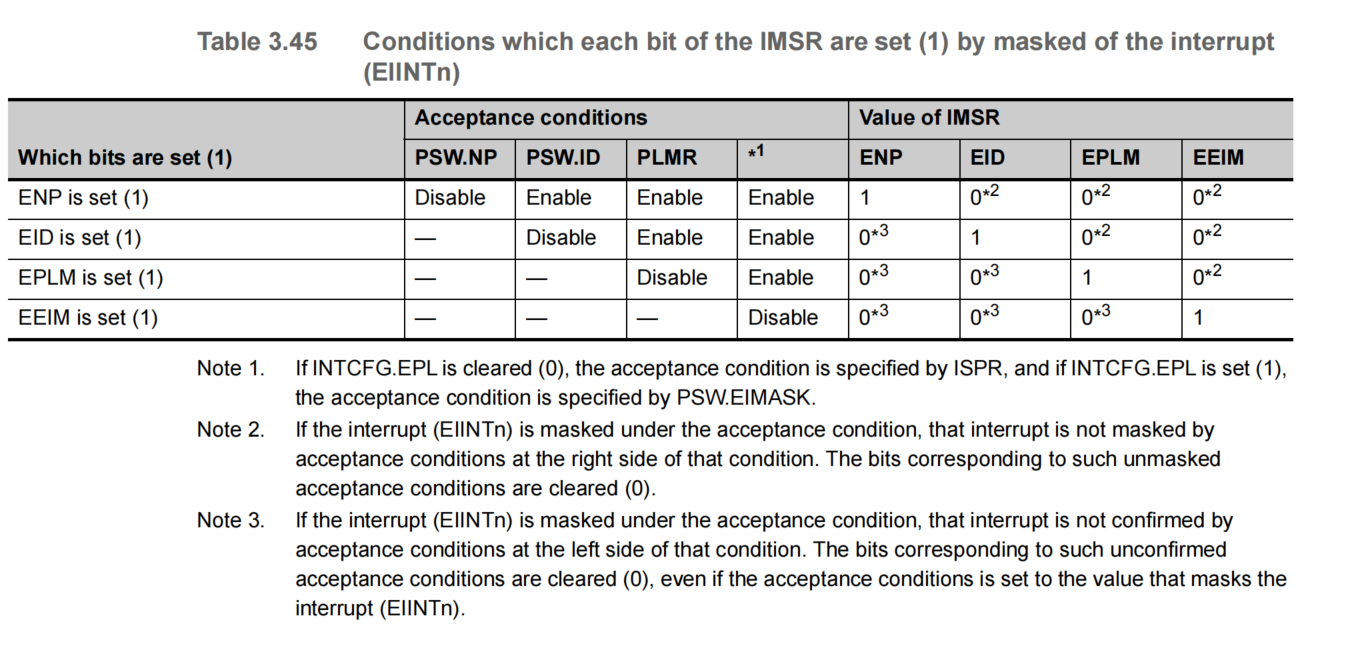

2.2 IMSR --- Interrupt Mask Status

The IMSR register is a register that indicates that interrupts notified to the CPU are masked for acceptance by the mask function in the CPU. Note that, for details of interrupt requests for updating each bit, see Section 3.2.3.3 (a), Order of updating IMSR.

(a) Order of updating IMSR

In the interrupt notified to the CPU, the acceptance conditions are confirmed in the order of ISPR or PSW.EIMASK (selected by INTCFG.EPL), PLMR, PSW.ID, PSW.NP. If the acceptance condition is set to the value that masks the interrupt, the interrupt request is masked there, and the acceptance conditions that are in the subsequent order are not confirmed. Note that depending on the type of exception, the confirmation of conditions that are not acceptance conditions do not.

Since the interrupt (EIINTn) has multiple acceptance conditions, it is set one bit at a time according to the order of confirmation of the acceptance conditions as follows.

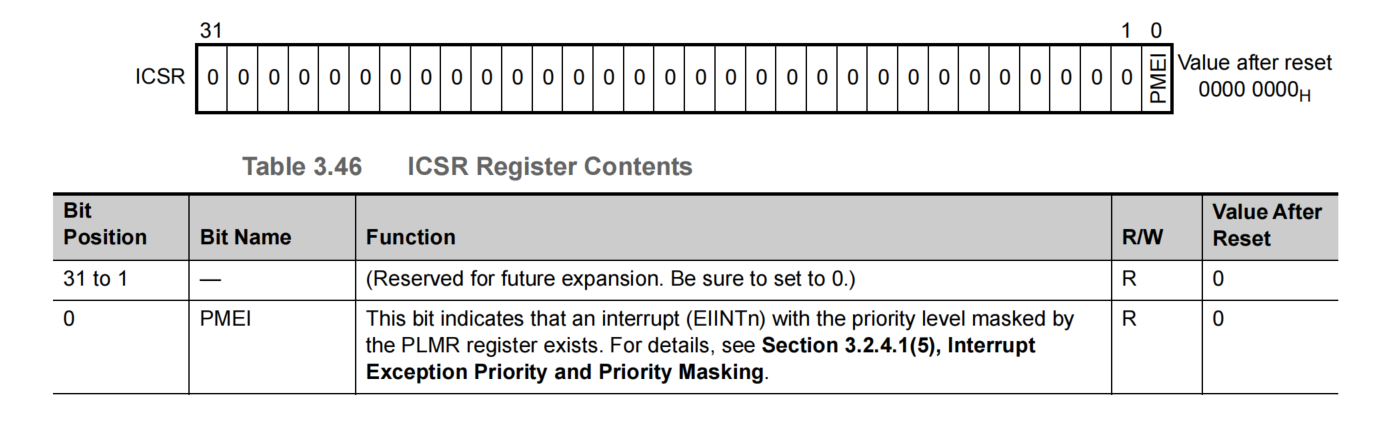

2.3 ICSR --- Interrupt Control Status

This register indicates the interrupt control status in the CPU.

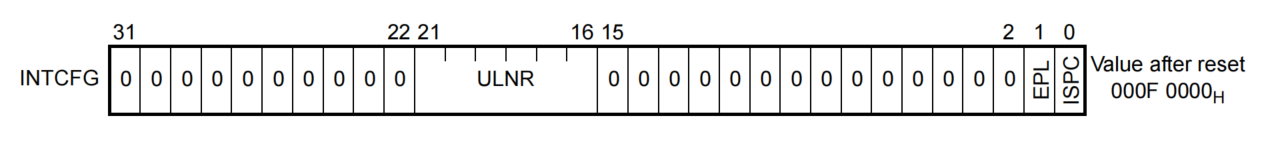

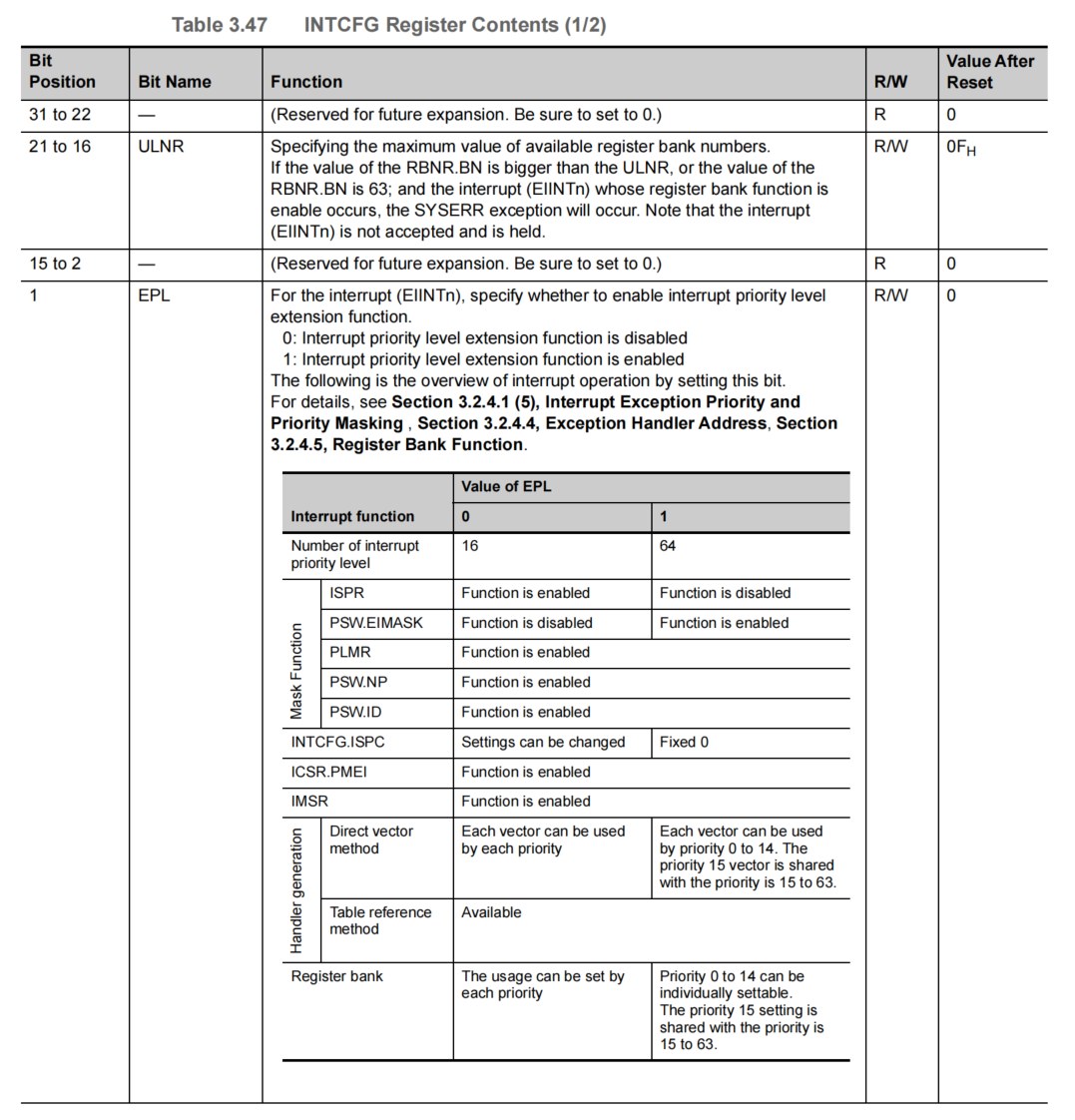

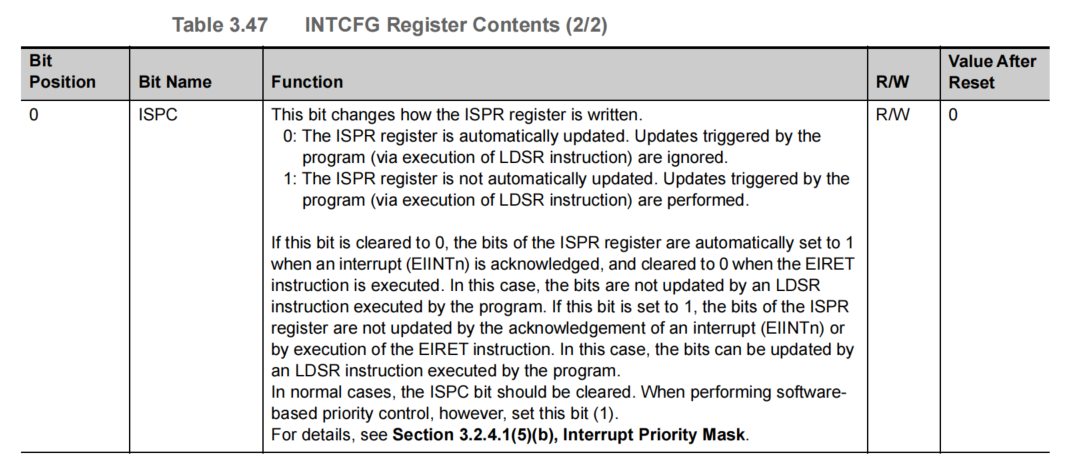

2.4 INTCFG --- Interrupt Function Setting

This register is used to specify settings related to the CPU's internal interrupt function.

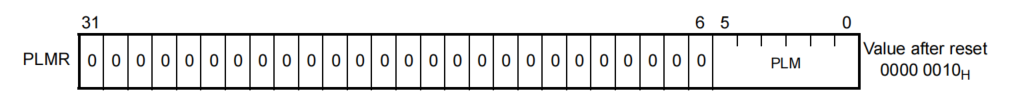

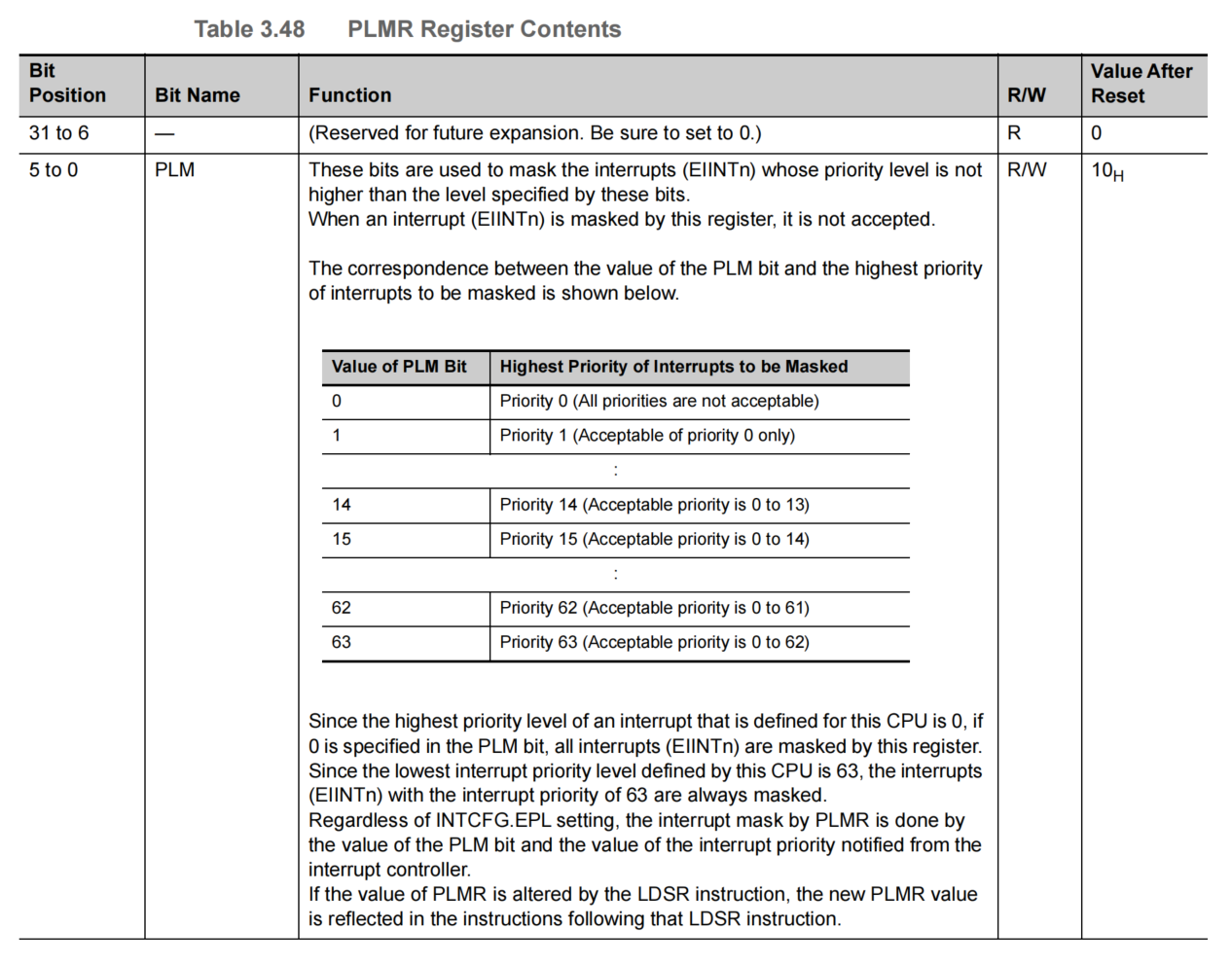

2.5 PLMR --- Interrupt Priority Level Mask

This register masks the interrupts (EIINTn) whose priority level is not higher than the level specified by these bits.