#灵感# 整理一下严重的cdc error

目录

[2、Ac_glitch03 (xxx) :](#2、Ac_glitch03 (xxx) :)

[3、Ar_unsync01 (2) :](#3、Ar_unsync01 (2) :)

[4、Clock_converge01 (2) :](#4、Clock_converge01 (2) :)

[5、Clock_glitch05 (16) :](#5、Clock_glitch05 (16) :)

[6、Clock_info03a (99) :](#6、Clock_info03a (99) :)

[7、Clock_info03c (253) :](#7、Clock_info03c (253) :)

[8、Clock_sync06 (40) :](#8、Clock_sync06 (40) :)

1、Ac_unsync01

Ac_unsync01 (xx) : Checks unsynchronized crossings for scalar signals

这个error 报告 "未同步的标量信号跨时钟域传输", Ac_unsync01违规意味着会出现情况:

-

亚稳态风险:信号可能在不稳定状态被采样

-

功能错误:逻辑可能产生错误输出

-

系统崩溃:可能导致状态机挂死或数据损坏

举例子:

Unsynchronized Crossing:

destination flop xxxxx..hi_dbit_en, clocked by xxxx.U_GMAC0_REFCLK.C,

source flop xxxx.tpe_state[0], clocked by xxxxxx.div_clk.

Reason: Sources from different domains converge before being synchronized [Total Sources: 5 (Number of source domains: 3)]

这个error 报告 "未同步的标量信号跨时钟域传输",

具体来说,有5个来自3个不同时钟域的源触发器 ,在没有同步的情况下,汇聚并驱动同一个目标触发器。

解决:添加同步器

修复的方案:

| 信号类型 | 修复方案 | 预估工作量 |

|---|---|---|

| 控制信号(使能、复位、门控) | 双触发器同步 | 简单,批量处理 |

| 状态信号(状态机状态、标志位) | 握手协议 | 中等,需两端修改 |

| 配置信号(静态或准静态) | 可waive(需论证) | 需仔细评估 |

2、Ac_glitch03 (xxx) :

Reports clock domain crossings subject to glitches

时钟域交叉毛刺风险报告。举例子:

Destination flop 'xxxx.gmac0_mac_speed_1d[1:0]' clocked by 'xxxx.U_GMAC0_REFCLK.C' can glitch (3 source(s), 2 domain(s)).

Reason :'Sources from different domains in fanin,Source reconverges'

file+line: gmac0_mac_speed_1d <= {gmac0_phy_intf_sel[0],gmac0_mac_speed} ;

具体来说,触发器gmac0_mac_speed_1d 的输入端有来自2个不同时钟域的2个源,这可能导致在目标时钟域产生毛刺。

修复:为每个时钟域信号添加同步器、添加毛刺滤波器

// 原始代码(有问题)

always @(posedge U_GMAC0_REFCLK.C) begin

gmac0_mac_speed_1d <= {gmac0_phy_intf_sel[0], gmac0_mac_speed}; // ❌

end

// 修复方案:为每个异步输入添加同步器

reg gmac0_phy_intf_sel_sync;

reg gmac0_mac_speed_sync;

// 同步器链

always @(posedge U_GMAC0_REFCLK.C) begin

// 同步 gmac0_phy_intf_sel[0]

reg sync_stage1_sel, sync_stage2_sel;

sync_stage1_sel <= gmac0_phy_intf_sel[0];

sync_stage2_sel <= sync_stage1_sel;

gmac0_phy_intf_sel_sync <= sync_stage2_sel;

// 同步 gmac0_mac_speed

reg sync_stage1_speed, sync_stage2_speed;

sync_stage1_speed <= gmac0_mac_speed;

sync_stage2_speed <= sync_stage1_speed;

gmac0_mac_speed_sync <= sync_stage2_speed;

end

// 使用同步后的信号

always @(posedge U_GMAC0_REFCLK.C) begin

gmac0_mac_speed_1d <= {gmac0_phy_intf_sel_sync, gmac0_mac_speed_sync}; // ✅

end

3、Ar_unsync01 (2) :

Reports unsynchronized reset signals in the design

Ar_unsync01 是复位相关的严重错误,报告了未同步的复位信号跨时钟域传播。

例子:

Reset signal 'xxx.U_JTAG_TRSTN.C' for 'clear' pin of flop

'xxxx_core.u_dfd_tdr_top.u_dfd_tap.capturedr_r_n', //复位信号连接到触发器的 clear 端

clocked by 'asic_top.u_asic_io.U_JTAG_TCK.C', is unsynchronized by reason: Missing synchronizer //缺少同步器

解决:添加复位同步器

4、Clock_converge01 (2) :

Flags a clock signal whose multiple fan-outs converge

标记同一个时钟信号经过不同路径后重新汇聚到同一逻辑节点的情况。

核心问题

-

同一个时钟信号(或同源时钟)通过不同路径(如经过缓冲器、分频器、门控单元等)后,重新汇聚到同一个组合逻辑节点

-

由于路径延迟不同,可能导致时钟信号在汇聚点产生毛刺或时序竞争

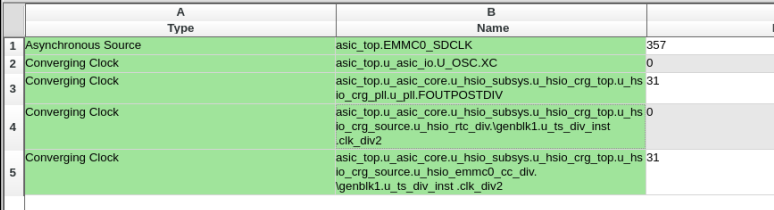

5、Clock_glitch05 (16) :

Flags asynchronous sources that converge with different domain clocks

Clock_glitch05 报告一个异步信号与多个时钟域汇聚 的问题,是内部组合逻辑。

例子:Asynchronous source 'asic_top.EMMC0_SDCLK' converges with different domain clock(s) at 'asic_top.EMMC0_SDCLK'

6、Clock_info03a (99) :

Flags cases not checked for clock domain crossings due to unconstrained clocks

例子:Clock-Net 'asic_top.u_pcie_subsys.u_pcie_dev1_x4.u_phy.upcsi_phy_rx0_clk_mux' is unconstrained

这是一个时钟未约束问题,导致SpyGlass无法对该时钟域的CDC路径进行检查。

解决:添加时钟约束:create_clock -name xxx 或者 设置 set_case_analysis 0 xxxx

7、Clock_info03c (253) :

Flags cases not checked for clock domain crossings as the clock pin of flop/latch is tied to constant or driven by quasi-static signal

Clock_info03c 是SpyGlass CDC检查中的信息性规则,用于标记那些因时钟引脚被固定为常量或由准静态信号驱动,而无法进行CDC检查的触发器/锁存器。

8、Clock_sync06 (40) :

Reports primary outputs driven by multiple clock domain flip-flops or latches

报告被多个时钟域的触发器/锁存器驱动的顶层输出端口。是接口问题。

先这么滴放着,以后再补充