最近调试了一下STM32H7 + USB3300 使用CDC进行通信,在这个过程中碰到很多坑,在这里记录一下。STM32H7系列引入了Cache和MPU,相对来说调试难度和系统架构变复杂了不少,希望我的经历能对大家有帮助。

这是一段非常有价值的调试经历,涵盖了高性能 MCU 开发中最核心的几个坑:外设 FIFO 管理、DMA 机制以及 Cache 一致性。

为了确保核心逻辑清晰,我将这段探索历程整理为一篇结构严谨的技术博客,方便你记录或分享。

极致性能:STM32H7 + USB3300 高速 USB 通信优化之路

0. 前言

在 STM32H7 上实现 USB 2.0 High-Speed (480Mbps) 传输时,硬件性能极高,但由于其复杂的架构(I/D Cache、AXI 总线、Internal DMA),开发者往往会遇到"速度上不去"或"开启缓存就挂掉"的窘境。本文记录了从 20MB/s 迈向链路极限的调优全过程。

硬件环境:

- MCU: STM32H7 系列

- PHY: USB3300 (外置高速 PHY)

- 模式: USB CDC (Communication Device Class)

1. 初始阶段:稳扎稳打的起点

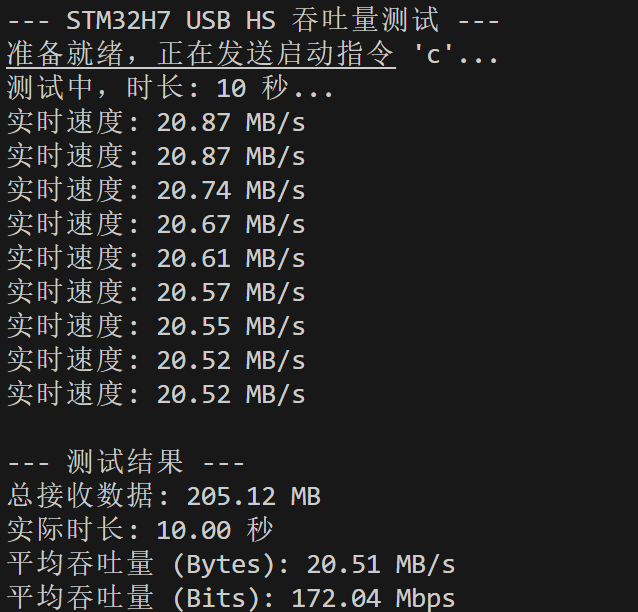

- 配置 :开启 I-Cache,失能 D-Cache,禁用 Internal DMA。

- 表现 :系统运行稳定,测速结果为 20.51 MB/s。

- 分析 :在没有 D-Cache 和 DMA 的参与下,CPU 负责搬运所有数据。虽然 20MB/s 已经超过了全速 (Full-Speed) 的理论极限,但对于 480Mbps 的高速链路来说,CPU 搬运成为了明显的瓶颈。

2. 进阶阶段:开启 Internal DMA 与 FIFO 陷阱

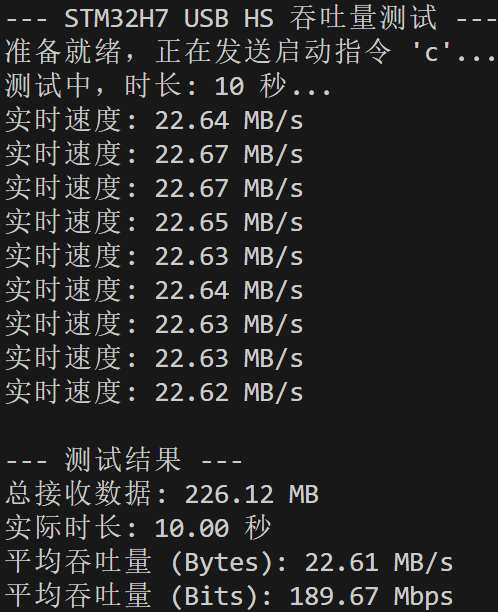

为了释放 CPU 压力并提升带宽,我们尝试开启 USB 内部的 Internal DMA。

- 遇到问题 :接收正常,但无法发送数据。

- 原因深度解析 :STM32H7 的 USB 内部 DMA 对 FIFO 的分配有严格要求。手册指出:"When DMA is used, 3n * FIFO locations should be reserved for internal DMA registers"。

- 解决方案 :重新计算并调整了

USB_OTG_HS的 FIFO 长度设置,预留出 DMA 寄存器所需的空间。 - 优化结果 :数据发送恢复正常,测速跃升至 22.61 MB/s (I-Cache ON, D-Cache OFF)。这是纯硬件搬运带来的显著增益。

3. 攻克阶段:D-Cache 的"幽灵"错误与 MPU 救场

在获得 22.61 MB/s 的成绩后,我们尝试开启 D-Cache 以进一步提升整体性能,却直接陷入了"枚举失败"的死胡同。

- 现象 :PC 端识别设备异常,得到的 PID 和 VID 均为 0。

- 奇怪的发现 :

- 数据一致性问题:开启 D-Cache 后,CPU 写入设备描述符的操作停留在 Cache 中,而 Internal DMA 直接从物理 SRAM 中读取数据。

- 结果:DMA 读到的是 SRAM 里的初始零值,导致枚举阶段发送给主机的描述符全是 0。

- 解决方案(白名单策略) :

由于 USB 库内部全局变量极多,手动刷 Cache (SCB_CleanDCache) 极其繁琐且易错。我通过 MPU (Memory Protection Unit) 划定了专属区域:- 将

RAM_D1(AXI SRAM) 整体设置为 Non-cacheable(通过 MPU Region 0)。 - 确保 USB 库的所有句柄和缓冲区都落在此非缓存区。

- 将

- 最终战果 :

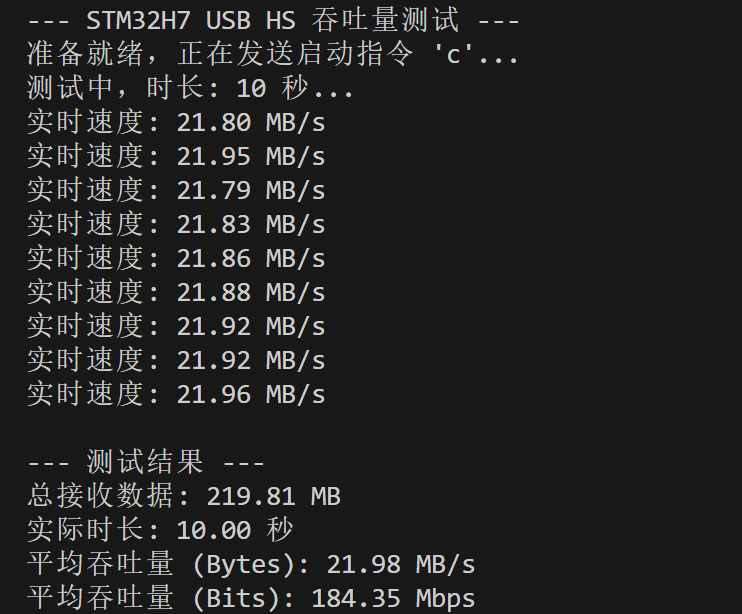

- 配置 :Internal DMA ON + I-Cache ON + D-Cache ON + MPU 局部隔离。

- 测速 :21.98 MB/s。

4. 经验总结与数据对比

为了提高处理效率,我们将三种模式下的性能与稳定性进行了直观对比:

| 配置模式 | I-Cache | D-Cache | Internal DMA | MPU 设置 | 测速结果 | 稳定性 |

|---|---|---|---|---|---|---|

| 基础模式 | 开启 | 关闭 | 关闭 | 无 | 20.51 MB/s | 稳定 |

| DMA 模式 | 开启 | 关闭 | 开启 | 无 | 22.61 MB/s | 需手动调优 FIFO |

| 完全体模式 | 开启 | 开启 | 开启 | 隔离 AXI SRAM | 21.98 MB/s | 极高(枚举正常) |

关键结论:

- DMA 是提速核心:开启 Internal DMA 后,吞吐量有质的飞跃。

- FIFO 空间补偿:开启 DMA 后必须严格按照手册公式重新计算 FIFO 大小,否则发送功能会失效。

- 一致性高于一切:在 H7 这种带 Cache 的架构中,如果不处理 Cache 一致性,USB 几乎无法正常工作。使用 MPU 将 AXI SRAM 设置为非缓存区,是兼顾开发效率与系统稳定性最平衡的方案。

结语:STM32H7 的 USB 开发不仅仅是调用库函数,更多的是在理解 CPU 缓存架构与外设 DMA 逻辑之间寻找平衡。希望这份避坑指南能为后来者节省数十小时的调试时间。