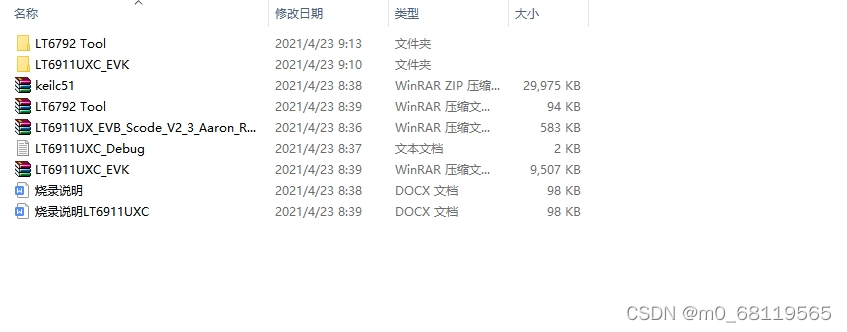

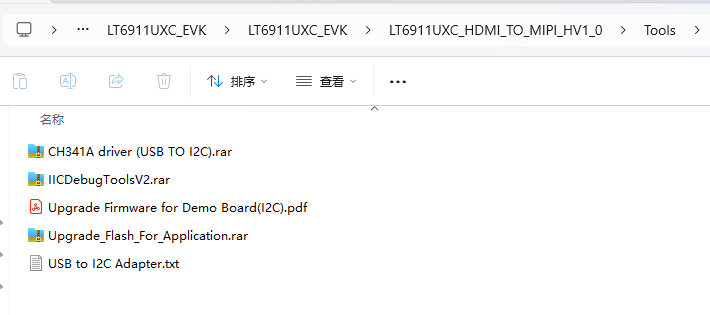

龙讯lt6911uxc,lt9611uxc资料,有源码固件,支持4k60,支持对接海思3519a和3559a,hdmi转mipi,双通道4k60

一、引言:芯片定位与代码价值

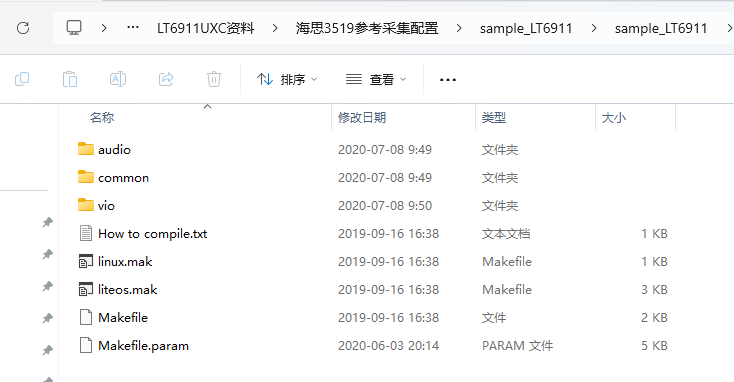

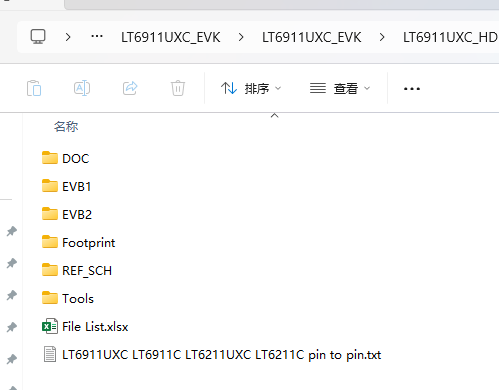

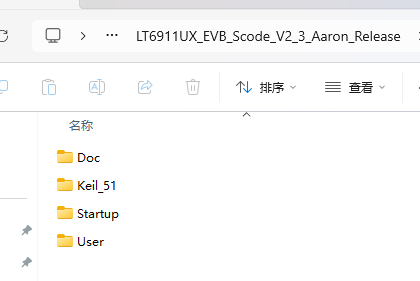

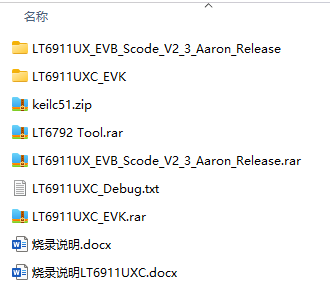

LT6911UXC 作为龙讯(Lontium)新一代高清视频转换芯片,是连接 HDMI 信号源与 MIPI 显示终端的核心桥梁,其驱动代码不仅是硬件控制的"指令集",更是实现 4K60Hz 高保真视频传输、多协议兼容、动态适配的技术载体。本文基于 LT6911UXEVB ScodeV2 3AaronRelease 源码,从架构设计逻辑 、模块功能细节 、数据交互机制 、调试优化技巧四个维度进行深度拆解,既解读代码"如何实现",更分析"为何如此设计",为工程师提供从代码理解到实战开发的完整技术参考。

二、代码架构:分层设计与模块协同

2.1 架构分层逻辑

代码采用"硬件抽象层-核心驱动层-应用配置层"三层架构,各层职责清晰、解耦性强,适配 51 单片机资源受限特性的同时,保障可维护性与扩展性:

| 架构层级 | 核心文件 | 核心职责 | 设计目标 |

|---|---|---|---|

| 硬件抽象层 | register.c、register.h | 寄存器地址映射、硬件寄存器直接读写接口 | 屏蔽硬件差异,统一寄存器访问方式 |

| 核心驱动层 | lt86121tx.c(HDMI)、mipi.c(MIPI)、edid.c(EDID) | 信号接收/发送、协议解析、时序控制 | 实现核心功能,对外提供标准化接口 |

| 应用配置层 | main.c、globalV.c、lt1704tx_dcs.c | 系统初始化调度、全局状态管理、面板控制 | 适配具体应用场景,支持参数定制 |

2.2 模块依赖关系

各模块通过"函数调用+全局变量"实现协同,关键依赖链路如下:

- 初始化链路 :

main()→LT6911UXInitialSteps()**→LT86121TXSystemInit()→ (HDMI 初始化、EDID 加载、MIPI 配置) - 数据处理链路 :HDMI 信号检测 →

Lt1704Tx_VideoChangeDetect()→ 色彩空间转换 → MIPI 数据发送 - 状态反馈链路 :硬件中断 → 全局状态变量更新(如

FlagCLKSTABLE) → 应用层逻辑响应

2.3 关键全局变量设计

globalV.c 定义的全局变量是模块间数据交互的"枢纽",按功能可分为三类,均通过 extern 声明实现跨文件访问:

- 状态标识变量 :

FlagCLKSTABLE(时钟稳定)、FlagHDMI20*(HDMI 2.0 模式)、Flag*RXHDCP22High(HDCP2.2 激活),用于快速判断硬件状态。 - 配置参数变量 :

gChipModel*(芯片型号:LT6911UX/LT6911UXC)、g*MipiFormat(MIPI 格式:RGB888/YUV4228bit)、gDisplayMode(显示模式:Video Copy/SideBySide),决定系统工作模式。 - 时序数据变量 :

gTimingStr*(存储 HDMI 时序:像素时钟、水平/垂直有效区域、消隐期)、g*MipiSetStr(MIPI 配置: lanes 数、时钟模式),是硬件参数配置的核心依据。

三、核心模块深度解析

3.1 系统初始化模块:从"上电"到"就绪"的完整流程

初始化是芯片稳定工作的基础,LT86121TX_SystemInit() 函数是核心入口,其流程设计遵循"硬件初始化→协议配置→状态准备"的逻辑,每一步均对应硬件底层需求:

3.1.1 时钟系统配置(`LT86121TX_SystemClk()`)

- 时钟源选择 :配置

BK855DREG = 0x0F,选择 24MHz 晶体作为系统时钟,而非内部 RC 时钟,确保时钟精度(±50ppm)满足 4K60Hz 信号时序要求(像素时钟误差需≤1%)。 - PLL 配置 :

BK8794REG=0x50、BK8796REG=0x28配置 PLL 倍频系数,生成 HDMI RX 所需的链路时钟(如 4K60Hz 需 148.5MHz 链路时钟)、MIPI 所需的字节时钟(如 4 lanes 需 800Mbps 字节时钟)。

3.1.2 GPIO 功能配置(`LT86121TX_GPIOInit()`)

GPIO 配置不仅是"引脚方向设置",更是硬件功能复用的关键:

- UART 引脚 :

BK859BREG = 0x80将 GPIO 配置为 UART_TX,用于调试信息输出(波特率 62500bps)。 - HDMI 5V 检测引脚 :

BK83B6REG = 0x0C配置为输入模式,检测 HDMI 源设备是否接入(5V 高电平表示接入)。 - LED 引脚 :

BK83CBREG |= 0xC0配置为输出模式,通过电平变化指示系统状态(如时钟稳定时 LED 常亮,异常时闪烁)。

3.1.3 HDMI RX 物理层初始化

物理层是 HDMI 信号接收的"第一道关卡",需解决高速信号传输中的损耗、干扰问题:

- 终端电阻校准 :

LT86121TX*RxPHY()*中BK8246_REG = 0xC1启动终端电阻校准,确保 HDMI 差分信号阻抗匹配(100Ω±10%),减少信号反射。 - 均衡器配置 :

LT86121TXRXFixEQ()中BK8734~37REG = 0xFF设置 CTLE(连续时间线性均衡器)最大增益,补偿 20m 长 HDMI 线缆的信号衰减(4K60Hz 信号在 20m 线缆中衰减约 3dB)。 - CDR 初始化 :

LT86121TX*RxCDR()*中BK8718_REG = 0x52配置 CDR 锁定顺序,确保时钟与数据同步,误码率≤1e-9。

3.1.4 初始化验证

初始化完成后,通过读取 BK86A7~AAREG(版本寄存器)确认芯片型号与固件版本,通过 LT86121TXRXFrequency_meter() 检测链路时钟频率,确保初始化成功。

3.2 EDID 管理模块:显示设备与源设备的"语言翻译官"

EDID(扩展显示识别数据)是 HDMI 协议的"握手协议",决定源设备输出的分辨率、帧率、色彩格式,本模块的设计核心是"预设+动态适配",确保兼容性与准确性。

3.2.1 EDID 数据结构解析

预设 5 种分辨率的 EDID 数据(256 字节),以默认激活的 4K60Hz EDID 为例,关键字段含义如下:

| 字节偏移 | 字段名称 | 数值 | 含义 |

|---|---|---|---|

| 0~7 | 头部 | 0x00,0xFF,0xFF,0xFF,0xFF,0xFF,0xFF,0x00 | EDID 标准头部,标识数据开始 |

| 8~17 | 厂商与产品信息 | 0x1E,0x6D,0x08,0x5B,0x79,0x4A,0x02,0x00,0x0A,0x19 | 厂商 ID(0x1E6D=龙讯)、产品 ID、生产年份 |

| 18~25 | 基本显示参数 | 0x01,0x03,0x80,0x3C,0x22,0x78,0xEA,0x30 | 分辨率支持(3840×2160)、宽高比(16:9) |

| 26~35 | 时序参数 | 0x35,0xA7,0x55,0x4E,0xA3,0x26,0x0F,0x50,0x54,0x21 | 水平/垂直消隐期、同步信号极性 |

| 128~135 | 扩展块标识 | 0x00,0x00,0x00,0xFD,0x00,0x38,0x3D,0x1E | 扩展块数量、校验信息 |

3.2.2 核心函数深度解读

- EDIDDtb BlockCalc(u8 *Pbuf) *:动态计算 EDID 时序块

- 输入参数:

Pbuf指向 EDID 数据中时序块起始地址(默认 0x36)。 - 计算逻辑:

- 水平消隐期 = 水平前肩(Hfp)+ 水平同步宽度(Hsw)+ 水平后肩(Hbp)。

- 垂直消隐期 = 垂直前肩(Vfp)+ 垂直同步宽度(Vsw)+ 垂直后肩(Vbp)。

- 将像素时钟(

g*TimingStr.PixelClock)、有效区域、消隐期等参数按 EDID 标准格式写入Pbuf。 - 设计意义:解决"预设 EDID 与实际时序不匹配"问题,例如当输入信号为 4K30Hz 时,动态调整时序块参数,避免源设备输出错误。

- 输入参数:

- EDIDCheckSumCalc(u8 *pbuf) :EDID 校验和计算

- 计算逻辑:分两部分计算(前 128 字节、后 128 字节),每部分求和后取反加 1(即 256 补码),结果写入第 127 字节(0x7F)和第 255 字节(0xFF)。

- 必要性:HDMI 源设备读取 EDID 时会校验校验和,若错误则拒绝输出信号,因此该函数是 EDID 有效性的"保障锁"。

- LT86121TXWrite EdidToShadow(void) :EDID 写入阴影寄存器

- 执行流程:

- 若

gEdidBlockCalEnable=TRUE*,调用EDID*DtbBlockCalc()动态更新时序块。 - 调用

EDIDCheckSumCalc()更新校验和。 - 循环写入 256 字节 EDID 数据到

BKB00AREG(地址寄存器)和BKB0B0REG(数据寄存器)。- 关键细节:阴影寄存器是 EDID 的"缓存区",HDMI 源设备通过 I2C 读取的是阴影寄存器数据,而非直接读取内存,确保数据稳定性。

3.2.3 EDID 配置实战建议

- 分辨率适配 :若实际面板为 1080P@60Hz,需将

#if 1从 4K60Hz 切换到 1080P 分支,并修改Default_EDID中的时序参数(如水平有效区域改为 1920,垂直有效区域改为 1080)。 - 兼容性测试:使用 HDMI 分析仪读取 EDID,验证厂商信息、分辨率列表、校验和是否正确,避免因 EDID 错误导致"无信号"问题。

3.3 HDMI 接收与处理模块:高速信号的"解码器"与"状态监测仪"

该模块是代码的"核心引擎",负责 HDMI 信号的接收、解码、状态检测,需解决高速信号同步、协议兼容、异常处理三大问题。

3.3.1 信号接收核心:PLL 与 CDR 协同

- PLL 动态调整 :

LT86121TXDHRXPLLPIX_DIVSEL()根据链路时钟频率调整 PLL 分频系数: - 若频率 > 0x186A0(100MHz):

BK821DREG=0x80(分频系数 1)。 - 若 0xC350(50MHz)< 频率 ≤ 0x186A0:

BK821DREG=0xA0(分频系数 2)。 - 若频率 ≤ 0xC350:

BK821DREG=0xB0(分频系数 4)。 - 设计目的:确保 PLL 输出的像素时钟与输入信号时钟同步,避免时序偏差导致的画面撕裂。

- CDR 锁定机制 :

LT86121TX*RxCDR()*中BK8715_REG=0x23配置 CDR 相位检测器增益,CDR 通过比较输入数据与本地时钟相位,动态调整时钟相位,实现"时钟数据恢复",确保 4K60Hz 信号(5.94Gbps 总带宽)的稳定接收。

3.3.2 状态检测:实时监控信号与协议状态

- 时钟稳定检测 :

- 中断触发:当 HDMI 链路时钟稳定时,

BK8509REG的 BIT4 置 1,触发时钟稳定中断。 - 中断处理:

LT86121TXRxClkStableISR()中设置FlagCLKSTABLE=TRUE,并启动 MIPI 配置流程。 - 异常处理:若时钟丢失(

FlagClockDisappear=TRUE*),调用LT86121TX*SystemInit()重新初始化,避免系统"死机"。

- 中断触发:当 HDMI 链路时钟稳定时,

- HDCP 协议检测 :

- HDCP1.4 检测:

LT86121TXRxHDCP14ChangeDetect()读取BK8513REG的 BIT2,若置 1 则表示输入信号为 HDCP1.4 加密,更新FlagRXHDCP14High=TRUE*,并通过BKC8*50*REG**标记 AVI 包中的加密类型。 - HDCP2.2 检测:

LT86121TX*RxHDCP22ChangeDetect()读取BKB0D2*REG*的 BIT7,若置 1 则表示输入信号为 HDCP2.2 加密,更新FlagRXHDCP22High=TRUE,并清除 HDCP2.2 重认证请求(BKB073REG=0x0B),避免重复认证导致的画面卡顿。 - 关键注意:HDCP 检测结果需同步到 MIPI 模块,若面板不支持解密,需禁用 HDCP 检测,否则会出现"有信号但黑屏"问题。

- HDCP1.4 检测:

- 热插拔检测(HPD) :

LT86121TXRxHpd(HPDStatus State)配置BKB000REG的 BIT0,控制 HPD 信号电平:- State=High:

BKB000REG |= BIT0,告知源设备"显示设备已就绪"。 - State=Low:

BKB000REG &= ~BIT0,告知源设备"显示设备断开"。 - 应用场景:当 HDMI 线缆拔插时,通过 HPD 信号变化触发源设备重新读取 EDID,实现"即插即用"。

3.3.3 错误检测与调试

- 误码计数读取 :

LT86121TXRXCH0*ErrorCnt()等函数读取各通道误码计数(BKB09B~A0REG),若误码计数持续增加,说明信号传输质量差,需:- 调整 HDMI 线缆(更换为屏蔽线缆)。

- 增加均衡器增益(修改

BK87*38~39_REG数值)。

- 调试信息输出 :通过 UART 打印

LT86121TXRXFrequencymeter()结果(链路时钟频率)、FlagCLKSTABLE(时钟状态)、FlagRXHDCP22High(HDCP 状态),快速定位"无信号""画面花屏"等问题。

3.4 MIPI 发送模块:视频信号的"格式转换器"与"面板驱动者"

MIPI 模块是代码的"输出端",负责将 HDMI 解码后的视频信号转换为 MIPI DSI/CSI 信号,其设计核心是"时序匹配"与"格式兼容"。

3.4.1 核心配置流程:从"数据格式"到"物理层传输"

以"HDMI RGB888 → MIPI YUV422_8bit(DSI 模式,4 lanes)"为例,配置流程如下:

- 色彩空间转换(

Lt1704Tx*ColorSpaceConvert())*** *- 转换逻辑:- 读取

BKB0*92*REG**的 BIT5~6,判断 HDMI 输入色彩格式(RGB888/YUV422/YUV444/YUV420)。 - 根据

g*OutputMode(默认 YUV422)配置转换寄存器: - 若输入为 RGB888、输出为 YUV422:

BK85ADREG=0xC8,启用 RGB→YUV422 转换。 - 若输入为 YUV420、输出为 YUV422:

BK85ADREG=0x00,启用 YUV420→YUV422 转换。 - 关键寄存器:

BK85AD~AFREG控制转换矩阵系数,确保色彩还原度(色差≤5%)。

- 读取

- MIPI PLL 配置(

Lt1704Tx*MipiTxPllSet())*** *- 计算逻辑:- 像素时钟(rdpixelclk)= HDMI 输入像素时钟(如 4K60Hz 为 594MHz)。

- MIPI 字节时钟(wrbyteclk)=(rdpixelclk × 色彩通道数)/(lanes 数 × 显示模式):

- 色彩通道数:RGB888 为 3,YUV422 为 2,YUV420 为 1.5。

- 显示模式:Video Copy 为 1,SideBySide 为 2。

- 示例:4K60Hz RGB888 → 4 lanes Video Copy:wrbyteclk =(594MHz ×3)/(4×1)= 445.5MHz。

- PLL 配置:根据 wrbyteclk 配置

BK82*3DREG*(频率档位)、BK82*37_REG(倍频系数),确保字节时钟误差≤2%。

- D-PHY 时序配置(

Lt1704Tx*MipiDphySet())*** *- 关键时序参数计算(以 445.5MHz 字节时钟为例):- HS 准备时间(wrhsprep):需 ≥40ns + 4×UI(UI=1/445.5MHz≈2.24ns)→ 约 49ns,对应

wrhsprep=49/2.24≈22。 - HS 零时间(wrhszero):需 ≥145ns +10×UI → 约 167ns,对应

wrhszero=167/2.24≈74。 - 寄存器配置:将计算结果写入

BKD4*2FREG*(HS 准备时间)、BKD4*30_REG(HS 零时间)等寄存器,确保 D-PHY 时序符合 MIPI 标准(MIPI D-PHY v1.2)。

- HS 准备时间(wrhsprep):需 ≥40ns + 4×UI(UI=1/445.5MHz≈2.24ns)→ 约 49ns,对应

- 协议配置(

Lt1704Tx*MipiProtocolSet())*** - 视频模式配置:BKD401REG = 0x07 | gMipiType(0x07=Burst 模式,gMipiType=0x08*=CSI 模式)。- 有效区域配置:读取 HDMI 时序(

BK86*7C~81REG*),将水平/垂直有效区域写入BKD4*0C~0DREG*(H 有效)、BKD4*06~07REG*(V 有效)。 - 数据类型配置:

BKD4*12REG=0x1E*(CSI YUV422*8bit 数据类型),确保面板能正确解析数据格式。

- 有效区域配置:读取 HDMI 时序(

3.4.2 显示模式差异化设计

代码支持两种显示模式,适配不同分辨率面板:

| 显示模式 | 适用场景 | 核心配置差异 | 寄存器标志 |

|---|---|---|---|

| Video Copy | 普通分辨率(≤1080P) | 单端口输出,水平有效区域为实际分辨率 | BKD444REG=0x00、BK85F5REG=0xFF |

| SideBySide | 高分辨率(4K) | 双端口并行输出,水平有效区域=实际分辨率/2 | BKD444REG=0x00(LT6911UXC)、BK85F5REG=0xF5 |

3.4.3 MIPI 调试常见问题与解决

- 画面倒置 :调整

BKB001REG的 BIT0~1(同步极性),若 Vsync 极性错误,设置BKB001REG |= 0x01。 - 花屏/丢点 :

- 检查 MIPI lanes 连接是否正确(如 lane0 与 lane1 是否反接,可通过

Lt1704Tx_MipiLaneSwap()调整 lane 顺序)。 - 增加 HS 时序参数(如

wrhslpx从 22 调整为 25),提高时序余量。

- 检查 MIPI lanes 连接是否正确(如 lane0 与 lane1 是否反接,可通过

- 无显示 :检查

InitPanel()中 DCS 指令是否正确,若面板为 DSI 类型,需确保SleepOut*(0x11)和Display*On(0x29)指令发送成功。

3.5 辅助模块:系统稳定运行的"支撑柱"

3.5.1 面板控制模块(lt1704tx_dcs.c)

- DCS 指令原理 :MIPI DCS 是面板控制的"标准协议",通过短包(2 字节)或长包(>2 字节)发送指令,代码中

cmdlist数组存储自定义 DCS 指令(如亮度调整、Gamma 校正)。 InitPanel()执行流程 :- 发送

Sleep*Out**指令:唤醒面板(面板默认休眠,需 120ms 延时稳定)。 - 发送

Display*On指令:开启面板显示(需 200ms 延时,确保面板驱动电路就绪)。 - 扩展建议:若面板需要 Gamma 校正,可在

cmdlist中添加0x26(Gamma 设定)指令,并配置相应参数。

- 发送

3.5.2 全局状态管理(globalV.c)

- 状态变量更新机制:

- 中断服务函数(如时钟稳定中断)直接更新状态变量(

FlagCLKSTABLE=TRUE)。 - 轮询函数(如

LT86121TXRxHDCP22ChangeDetect())比较新旧状态,若变化则更新变量并触发后续逻辑。 - 多模块协同示例 :当

FlagCLKSTABLE=TRUE且FlagHdmiStable=TRUE**时,Lt1704TxVideoChangeDetect()才会执行视频转换,避免"时钟未稳定时转换导致的错误"。

四、数据流程:从"HDMI 输入"到"MIPI 输出"的完整链路

以"4K60Hz HDMI RGB888 信号 → MIPI DSI YUV422_8bit 信号"为例,数据流转的每一步均对应代码模块的协同工作:

- 步骤 1:源设备连接与 EDID 协商

- HDMI 源设备接入,芯片检测到 5V 高电平(

BK859DREG & BIT3=1),触发LT86121TXRx5VChangeDetect(),设置FlagRX5V_High=TRUE。 - 源设备通过 I2C 读取芯片阴影寄存器中的 EDID,确认支持 4K60Hz RGB888 格式,开始输出信号。

- HDMI 源设备接入,芯片检测到 5V 高电平(

- 步骤 2:HDMI 信号接收与同步

- HDMI 信号经线缆传输到芯片 RX 引脚,经均衡器补偿后,由 CDR 恢复时钟与数据。

LT86121TXRXFrequency*meter()*检测链路时钟为 148.5MHz,LT86121TXDHRXPLLPIXDIVSEL()配置 PLL 分频系数为 1,生成 594MHz 像素时钟。- 时钟稳定后,触发时钟稳定中断,设置

FlagCLKSTABLE=TRUE。

- 步骤 3:色彩空间转换与时序提取

Lt1704Tx*ColorSpaceConvert()检测输入为 RGB888,输出为 YUV422,配置BK85ADREG=0xC8,启动转换。Lt1704Tx*MipiProtocolSet()读取BK867C~81REG,提取水平有效区域 3840、垂直有效区域 2160,写入 MIPI 协议寄存器。

- 步骤 4:MIPI 物理层配置与数据发送

Lt1704Tx*MipiTxPllSet()**计算字节时钟为 445.5MHz,配置 PLL 生成对应时钟。Lt1704Tx*MipiDphySet()配置 HS 时序参数,确保 D-PHY 稳定工作。Lt1704Tx_MipiVideoSet()配置 4 lanes 突发模式,启动 MIPI 数据发送。

- 步骤 5:面板显示

InitPanel()发送 DCS 指令唤醒面板,面板接收 MIPI 数据并显示 4K60Hz 画面。

- 步骤 6:状态监测与异常处理

- 主循环中持续调用

LT86121TXRxHDCP22ChangeDetect(),若 HDCP 状态变化则更新配置。 - 若检测到时钟丢失(

FlagClockDisappear=TRUE*),调用LT86121TX*SystemInit()重新初始化,恢复显示。

- 主循环中持续调用

五、性能优化与调试技巧

5.1 性能优化方向

- 时钟稳定性优化 :

- 选择高精度晶体(±20ppm),减少时钟漂移导致的画面撕裂。

- 调整

LT86121TXRxPLLSet()中BK8217REG(PLL 电荷泵电流),若电流过小则 PLL 锁定慢,过大则噪声大,建议设置为 0x29(中等电流)。

- MIPI 传输速率优化 :

- 若面板支持 4 lanes,优先配置 4 lanes(而非 2 lanes),减少单 lane 传输速率,降低误码率。

- 调整

Lt1704TxMipiDphySet()中BKD421REG(CKPOST),确保时钟后沿时序余量≥10%。

- 中断响应优化 :

- 禁用不必要的中断(如 HDCP 检测中断,若无需加密),减少 CPU 负载。

- 在中断服务函数中仅更新状态变量,避免复杂计算,确保中断响应时间≤10μs。

5.2 调试工具与方法

- UART 调试 :

-

启用

printf打印关键参数:

c

printf("PixelClock: %lu KHz\n", gPixelClock);

printf("MIPI ByteClock: %lu KHz\n", gMipiByteClock);

printf("HDCP22 State: %d\n", FlagRXHDCP22_High); -

通过串口助手查看参数,快速定位"时钟异常""HDCP 未检测"等问题。

-

- 寄存器调试 :

- 使用 JTAG 工具读取关键寄存器(如

BKB0D2REG(HDCP2.2 状态)、BK87AAREG(PLL 锁定状态)),验证配置是否生效。 - 若 MIPI 无输出,检查

BKD401REG(MIPI 模式)是否为 0x07(Burst 模式),BKD412REG(数据类型)是否正确。

- 使用 JTAG 工具读取关键寄存器(如

- 信号分析仪调试 :

- 使用 MIPI 分析仪捕获 MIPI 信号,查看 HS 模式下的眼图是否符合标准(眼高≥200mV,眼宽≥40% UI)。

- 使用 HDMI 分析仪监测 HDMI 源设备输出的时序参数,确认与 EDID 配置一致。

六、总结与展望

LT6911UXC 驱动代码是"硬件控制逻辑"与"协议标准"的完美结合,其模块化设计、动态配置机制、完善的状态检测,确保了 4K 高清视频的稳定传输。开发者在实际开发中,需重点关注 EDID 配置、HDMI 物理层参数、MIPI 时序匹配三大核心点,通过"配置→验证→调试"的循环,快速解决实际问题。

龙讯lt6911uxc,lt9611uxc资料,有源码固件,支持4k60,支持对接海思3519a和3559a,hdmi转mipi,双通道4k60

未来优化方向可包括:

- 增加动态 EDID 读取功能(从面板 EEPROM 读取 EDID,而非预设),提升兼容性。

- 支持 HDR 格式(如 HDR10),扩展色彩范围。

- 加入温度补偿机制,在高温环境下调整 PLL 参数,确保时钟稳定。

通过深入理解代码架构与功能细节,工程师可基于此代码快速开发出适配不同场景的高清视频转换产品,如车载显示、工业监控、消费类显示终端等。