低于表面码阈值的量子纠错

谷歌量子人工智能团队及合作者(2024 年 8 月 24 日)

摘要

量子纠错 [1,2,3,4] 通过将多个物理量子比特整合为一个逻辑量子比特,为实现实用化量子计算提供了路径:随着量子比特数量的增加,逻辑错误率会呈指数级被抑制。然而,这种指数级抑制仅在物理错误率低于临界阈值时才会发生。在本研究中,我们实现了两种运行在该阈值以下的表面码量子存储器:一种是距离为 7 的码,另一种是集成了实时解码器的距离为 5 的码。当码距增加 2 时,我们所构建的大型量子存储器的逻辑错误率被抑制了因子 Λ=2.14±0.02,最终实现了 101 个物理量子比特的距离 7 码,其每个纠错周期的错误率为 0.143%±0.003%。该逻辑存储器还实现了盈亏平衡突破,其寿命是最优物理量子比特寿命的 2.4±0.3 倍。我们在实时解码的情况下仍保持了低于阈值的性能,在码距为 5、周期为 1.1 微秒的条件下,实现了平均 63 微秒的解码器延迟,且解码周期数高达百万次。为探究纠错性能的极限,我们运行了距离至 29 的重复码实验,发现逻辑性能受限于罕见的关联错误事件,这类事件大约每小时发生一次,即 3×10⁹个周期。我们的研究成果展示了器件性能,若进行规模化扩展,有望满足大规模容错量子算法的运行要求。

预印本编号:APS/123-QED

一、引言

量子计算有望在量子化学 [5]、量子模拟 [6]、密码学 [7] 和优化问题 [8] 等领域实现计算加速。然而,量子信息具有脆弱性,量子操作也易产生错误。当前最先进的多量子比特平台才刚刚实现 99.9% 保真度的纠缠门 [9,10],远低于许多应用所需的低于 10⁻¹⁰的错误率 [11,12]。量子纠错的核心思想是通过将量子信息分布在多个纠缠的物理量子比特上以抵御错误,从而实现高保真度的逻辑量子比特。若物理操作的噪声低于临界阈值,随着每个逻辑量子比特所使用的物理量子比特数量增加,逻辑错误率应呈指数级被抑制。这种特性可由近似关系式表示:εd∝(pthrp)(d+1)/2该式适用于经纠错的表面码逻辑量子比特 [4,3,13]。其中,d为码距,表示每个逻辑量子比特使用2d2−1个物理量子比特;p和εd分别为物理错误率和逻辑错误率;pthr为该码的阈值错误率。因此,当p≪pthr时,逻辑量子比特的错误率随码距呈指数级被抑制,错误抑制因子Λ=εd/εd+2≈pthr/p表示码距增加 2 时逻辑错误率的降低幅度。尽管多个平台已展示了量子纠错的不同特性 [14,15,16,17,18,19,20],但尚无量子处理器明确实现低于阈值的性能。

尽管实现低于阈值的物理错误率本身是一项艰巨的挑战,容错量子计算还提出了超出原始性能的要求,包括在量子算法所需的数小时时间尺度上保持稳定性 [21],以及主动消除泄漏等关联错误源 [22]。此外,容错量子计算对经典协处理器也提出了要求:量子器件产生的校验子信息必须在生成时被快速解码 [23]。超导量子比特的快速操作时间(数十至数百纳秒)在速度上具有优势,但同时也对快速且精准的错误解码提出了挑战。

在本研究中,我们在两台超导处理器上实现了运行在阈值以下的表面码。使用 72 量子比特处理器,我们实现了集成实时解码器的距离 5 表面码;此外,使用性能相近的 105 量子比特处理器,我们实现了距离 7 表面码。这些处理器分别在码距 5 和码距 7 时实现了Λ>2。我们的距离 5 量子存储器实现了盈亏平衡突破,距离 7 码的量子信息保存时间是其最优物理量子比特的两倍以上。为识别潜在的逻辑错误平台期,我们还在 72 量子比特处理器上运行了高码距重复码,其错误率由每小时发生一次的关联错误事件主导。这类错误的成因尚未明确,构成了当前 10⁻¹⁰量级的错误平台期。最后,我们证明即使在实时解码的情况下,72 量子比特处理器仍能保持低于阈值的运行状态,满足处理器 1.1 微秒快速周期所施加的严格时序要求。

二、低于阈值的表面码量子存储器

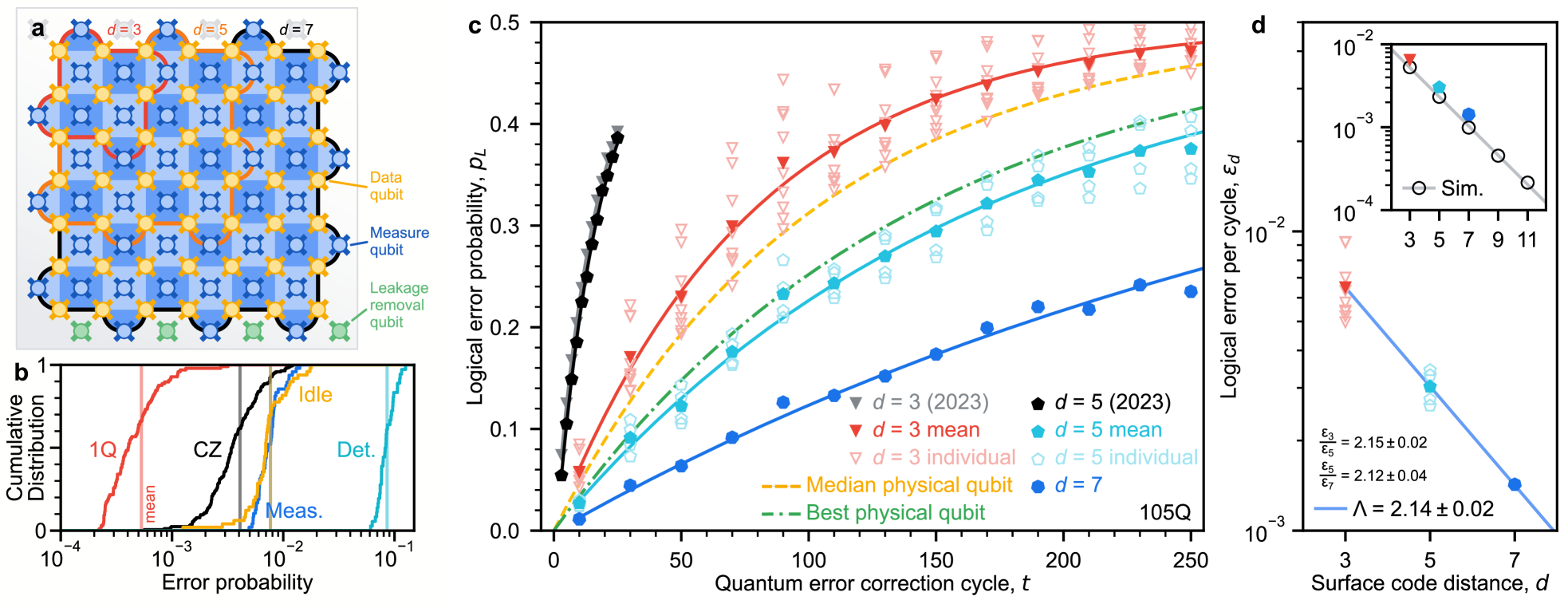

图 1:表面码性能。

a. 105 量子比特处理器上距离 7 表面码的示意图。每个测量量子比特(蓝色)对应一个稳定子(蓝色色块)。红色轮廓:用于对比的 9 个距离 3 码中的一个(3×3 阵列);橙色轮廓:用于对比的 4 个距离 5 码中的一个(4 个角落);黑色轮廓:距离 7 码。我们通过下方相邻量子比特移除每个数据量子比特(金色)的泄漏,边界处使用额外的泄漏移除量子比特(绿色)。b. 105 量子比特处理器上测量的错误概率累积分布。红色:单量子比特门的泡利错误;黑色:CZ 门的泡利错误;蓝色:测量的平均识别错误;金色:数据量子比特在测量和重置期间闲置时的泡利错误;蓝绿色:权重为 4 的探测概率(距离 7 码,250 个周期平均)。c. 不同存储器实验持续时间下的逻辑错误概率pL。每个数据点代表 105 次重复实验,经神经网络解码后,对逻辑基(XL和ZL)取平均。黑色和灰色:文献 [17] 中的数据用于对比。曲线:对码和基取平均后的指数拟合。为计算εd值,我们分别对每个码和基进行单独拟合 [24]。d. 逻辑每周期错误率εd随表面码码距d的降低。每个点的不确定度小于 5×10⁻⁵。符号与 c 图一致。d=3和d=5的均值由各码和基的单独εd拟合计算得出。直线:对公式 1 的拟合,用于确定Λ。插图:模拟至d=11的结果与实验点对比,均采用集成匹配合成解码以作对照。直线:对模拟结果的拟合,Λsim=2.25±0.02。

我们首先展示图 1a 中 105 量子比特处理器的实验结果。该处理器采用超导 transmon 量子比特的方形网格架构 [25],与此前报道的处理器相比,操作保真度有所提升 [26,17]。量子比特的平均工作T1时间为 68 微秒,T2,CPMG时间为 89 微秒,这得益于改进的制备工艺、参与率工程设计和电路参数优化。相干时间的延长提升了所有操作的保真度,如图 1b 所示。

我们还对解码算法进行了多项改进,采用了两种离线高精度解码器:一种是神经网络解码器 [27],另一种是关联最小权重完美匹配解码器 [29] 的集成集成体 [28],并结合了匹配合成技术 [30]。这些解码器运行在不同的经典硬件上,为高精度实时解码提供了两种潜在路径。为适配器件噪声,我们使用处理器数据对神经网络进行微调 [27],并对匹配图的权重采用强化学习优化 [31]。

我们按照文献 [17] 的方法,运行了包含 49 个数据量子比特、48 个测量量子比特和 4 个额外泄漏移除量子比特的距离 7 表面码量子存储器。简言之,我们先将数据量子比特制备为ZXXZ表面码 [32] 的XL或ZL基的直积态,启动表面码运行;随后重复可变数量的纠错周期,测量量子比特从数据量子比特中提取奇偶校验信息并发送至解码器;每次校验子提取后,我们执行数据量子比特泄漏移除(DQLR)[33],确保激发到高能级的泄漏是短暂的;最后通过测量单个数据量子比特确定逻辑量子比特的状态,检验解码器校正后的逻辑测量结果是否与初始逻辑态一致。

基于表面码数据,我们利用整体错误探测概率 [34] 表征处理器的物理错误率,即权重为 4 的稳定子测量对比中探测到错误的比例。对于码距d=(3,5,7),表面码的探测概率分别为pdet=(7.7%,8.5%,8.7%)。我们将探测概率随码尺寸的增加归因于有限尺寸效应 [24] 和量子比特间的寄生耦合,预计这两种效应在更大的处理器尺寸下会趋于饱和 [35]。

我们通过拟合最多 250 个周期的逻辑每周期错误率εd(对X和Z基取平均)来表征表面码的逻辑性能。我们对 9 个不同的距离 3 子网格和 4 个不同的距离 5 子网格的性能取平均,以与距离 7 码对比。最后,我们通过对ln(εd)与d进行线性回归计算错误抑制因子Λ。使用神经网络解码器时,我们观测到Λ=2.14±0.02,ε7=(1.43±0.03)×10−3(见图 1c-d);使用集成匹配合成解码时,观测到Λ=2.04±0.02,ε7=(1.71±0.03)×10−3。

此外,我们基于图 1b 中测量的各组分错误率构建噪声模型,同时纳入泄漏和量子比特间的杂散相互作用 [17,24],模拟了更高码距的逻辑量子比特。图 1d 的插图中展示了模拟结果与实验数据的对比,均采用集成匹配合成解码。我们观测到模拟与实验结果基本一致,且错误得到了显著抑制,证实表面码运行在阈值以下。

目前我们重点关注错误抑制因子Λ,因为低于阈值的性能保证了通过构建足够大的逻辑量子比特,能够超越物理量子比特的寿命和操作保真度。事实上,我们的距离 7 逻辑量子比特的寿命已超过其组成物理量子比特的两倍以上。由于逻辑量子比特与物理量子比特的噪声过程不同,二者的对比具有一定复杂性,我们在图 1c 中绘制了逻辑错误率与X、Z基初始化下平均物理量子比特错误率的直接对比。为量化量子比特寿命本身,我们采用文献 [16,24] 提出的度量标准对纯态取平均。距离 7 逻辑量子比特的寿命为 291±6 微秒,超过所有组成物理量子比特的寿命(中位值 85±7 微秒,最优值 119±13 微秒),提升因子为 2.4±0.3。我们的逻辑存储器实现盈亏平衡突破,将此前基于玻色子码的研究结果 [36,37,16] 拓展至多量子比特码,是实现逻辑运算盈亏平衡的关键一步。

三、逻辑错误敏感性

借助低于阈值的逻辑量子比特,我们可以探究该状态下逻辑错误对各类错误机制的敏感性。首先测试逻辑错误随物理错误和码距的变化规律。如图 2a 所示,我们在数据量子比特和测量量子比特上注入不同强度的相干错误,并从每次注入实验中提取两个量:一是以探测概率作为总物理错误率的代理指标;二是通过测量 10 个周期的逻辑错误概率,使用关联匹配解码 [29] 推断逻辑每周期错误率。

图 2b 中,我们绘制了距离 3、5、7 码的逻辑每周期错误率与探测概率的关系。发现三条曲线在探测概率约 20% 处相交,这与文献 [17] 研究的交叉区域基本一致。插图进一步表明,探测概率可作为1/Λ的良好代理指标。对交叉点以下的幂律拟合发现,其值约为公式 1 预测的理想值(d+1)/2的 80%。我们推测该偏差由器件中的额外关联效应导致。尽管如此,更高码距的逻辑错误降低更快,在量子处理器上原位展现出典型的阈值特性。

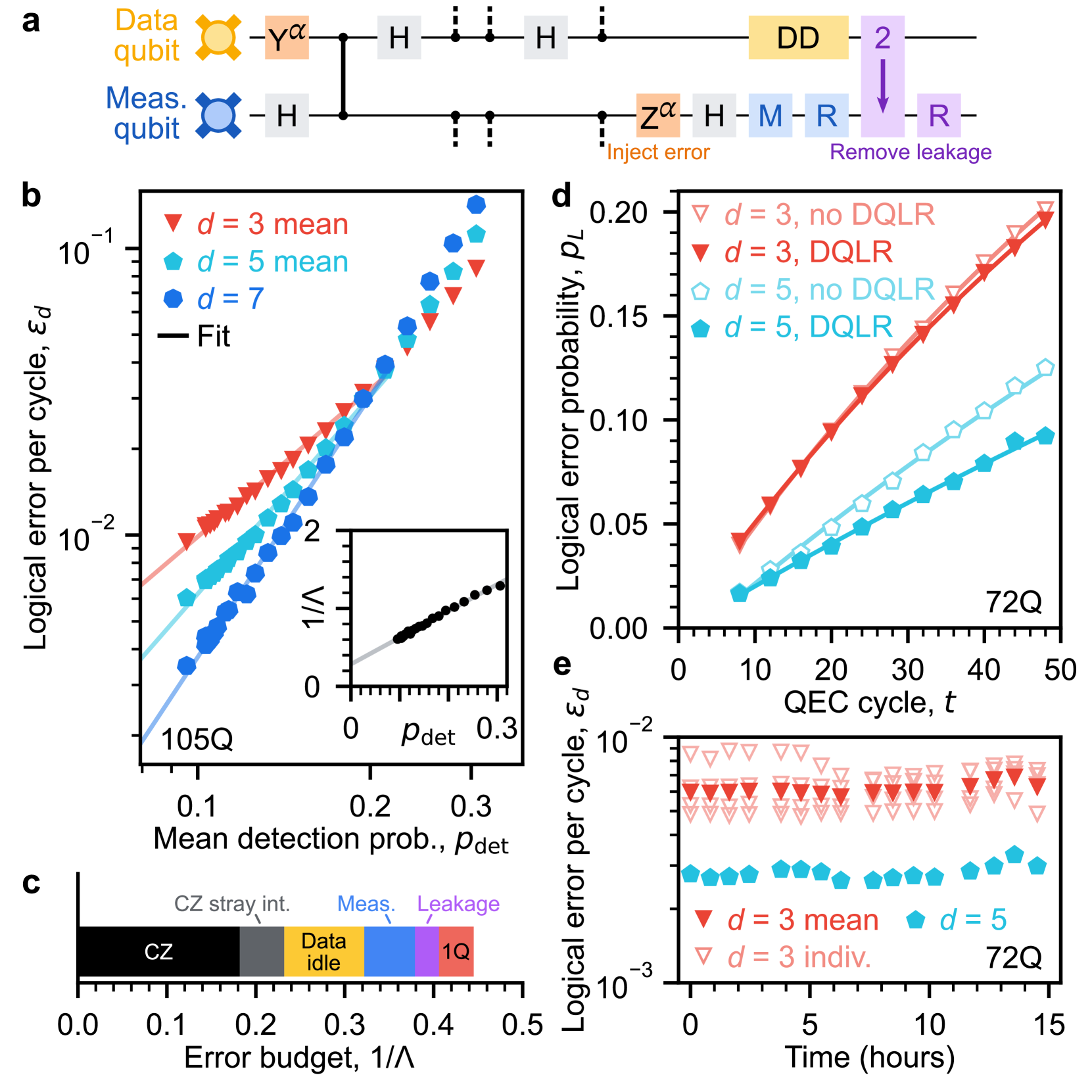

图 2:表面码中的错误敏感性

a. 表面码电路的一个周期,聚焦于一个数据量子比特和一个测量量子比特。黑色条:CZ 门;H:阿达马门;M:测量;R:重置;DD:动力学去耦。橙色:注入的相干错误;紫色:数据量子比特泄漏移除(DQLR)[33]。b. 表面码中的错误注入。距离 3 码对 9 个子码取平均,距离 5 码对 4 个子码取平均,如图 1 所示。逻辑性能对所有码的平均权重 4 探测概率作图,增加错误注入角度α会提升探测概率。每个实验包含 10 个周期,总重复次数为 2×10⁴次。直线:对交叉点及以下数据点的幂律拟合。插图:逆错误抑制因子1/Λ与探测概率的关系。直线:对1/Λ<1点的拟合。c. 基于组分错误和模拟的表面码错误预算。CZ:CZ 门错误(不含泄漏和杂散相互作用);CZ 杂散相互作用:CZ 门中由杂散相互作用导致的错误;数据闲置:测量和重置期间数据量子比特的闲置错误;测量:测量和重置错误;泄漏:CZ 门中及由热激发导致的泄漏;单量子比特门:单量子比特门错误。d. 每个周期是否执行数据量子比特泄漏移除时的逻辑性能对比。距离 3 点(红色三角形)对四个象限取平均。每个实验包含 105 次重复。曲线:指数拟合。e. 重复实验评估性能稳定性,对比距离 3 和距离 5 码。每个点代表逻辑性能随实验持续时间的扫描结果,最长至 250 个周期。

为量化关联错误与更典型的门错误的影响,我们构建了错误预算。遵循文献 [17,38] 的方法,我们估计不同组分错误对1/Λ的相对贡献,基于 72 量子比特处理器的详细模型进行模拟。该模型包含门和测量带来的局域噪声源,以及两种关联错误源:泄漏,以及 CZ 门中的杂散相互作用(可诱导关联的ZZ类和交换类错误 [24])。图 2c 展示了使用关联匹配解码时 72 量子比特处理器的1/Λ错误预算。将相同解码器应用于实验数据,错误预算对Λ的预测值偏高 20%,表明处理器中大部分(但非全部)错误效应已被捕捉。关联错误约占预算的 17%,虽非主导因素,但预计其重要性会随错误率降低而提升。总体而言,CZ 门的局域错误和关联错误是错误预算的最大贡献者,因此持续提升相干性和校准精度对进一步降低逻辑错误至关重要。

我们主动缓解的一种潜在关联错误源是 transmon 量子比特的高能级泄漏。在逻辑量子比特运行期间,我们通过多能级重置移除测量量子比特的泄漏;对于数据量子比特,DQLR 将泄漏激发转移至测量量子比特(或额外的泄漏移除量子比特)[33]。为检验泄漏的影响,我们在 72 量子比特处理器上运行距离 3 和距离 5 码,对比执行和不执行 DQLR 时的逻辑错误概率,结果如图 2d 所示。尽管激活 DQLR 对距离 3 码的性能影响不大,但显著提升了距离 5 码的性能,使Λ增加了 35%。相比之下,探测概率仅降低了 12%[24],表明仅当错误无关联时,探测概率才能作为逻辑错误抑制的良好代理指标。总体而言,解决泄漏问题对基于 transmon 量子比特的表面码运行至关重要 [39,15,33]。

最后,我们测试了对漂移的敏感性。使用 72 量子比特处理器,我们在 15 小时内 16 次测量 1 个距离 5 码和 4 个距离 3 码的逻辑性能,结果如图 2e 所示。重复实验前,我们采用频率优化策略预测二能级系统(TLS)的缺陷频率,避免量子比特在初始校准和实验期间与 TLS 耦合;此外,每四次实验后重新校准处理器,以应对量子比特频率和读出信号的潜在漂移。使用神经网络解码时,我们观测到平均Λ=2.18±0.07(标准偏差),最优Λ=2.31±0.02[24]。尽管最差的距离 3 象限性能因瞬态 TLS 的移动快于预测而出现波动,但距离 5 码的波动被抑制,表明更大的码对组件级漂移更不敏感。此外,漂移重新校准后立即进行的实验,其逻辑错误率与校准前无显著差异,说明逻辑量子比特对当前水平的量子比特频率和读出漂移具有鲁棒性。这些结果表明,超导处理器可在大规模容错算法所需的数小时时间尺度上保持稳定 [21]。

四、利用重复码探究超低错误 regime

尽管实现了低于阈值的表面码,当前逻辑错误率与实用量子计算的要求仍相差数个数量级。此前开展重复码实验时,我们发现高能撞击事件约每 10 秒发生一次,引发大规模关联错误爆发,导致逻辑错误平台期约为 10⁻⁶[17]。这类错误会阻碍未来纠错算法的运行,因此我们在新型器件上重新开展了重复码实验。

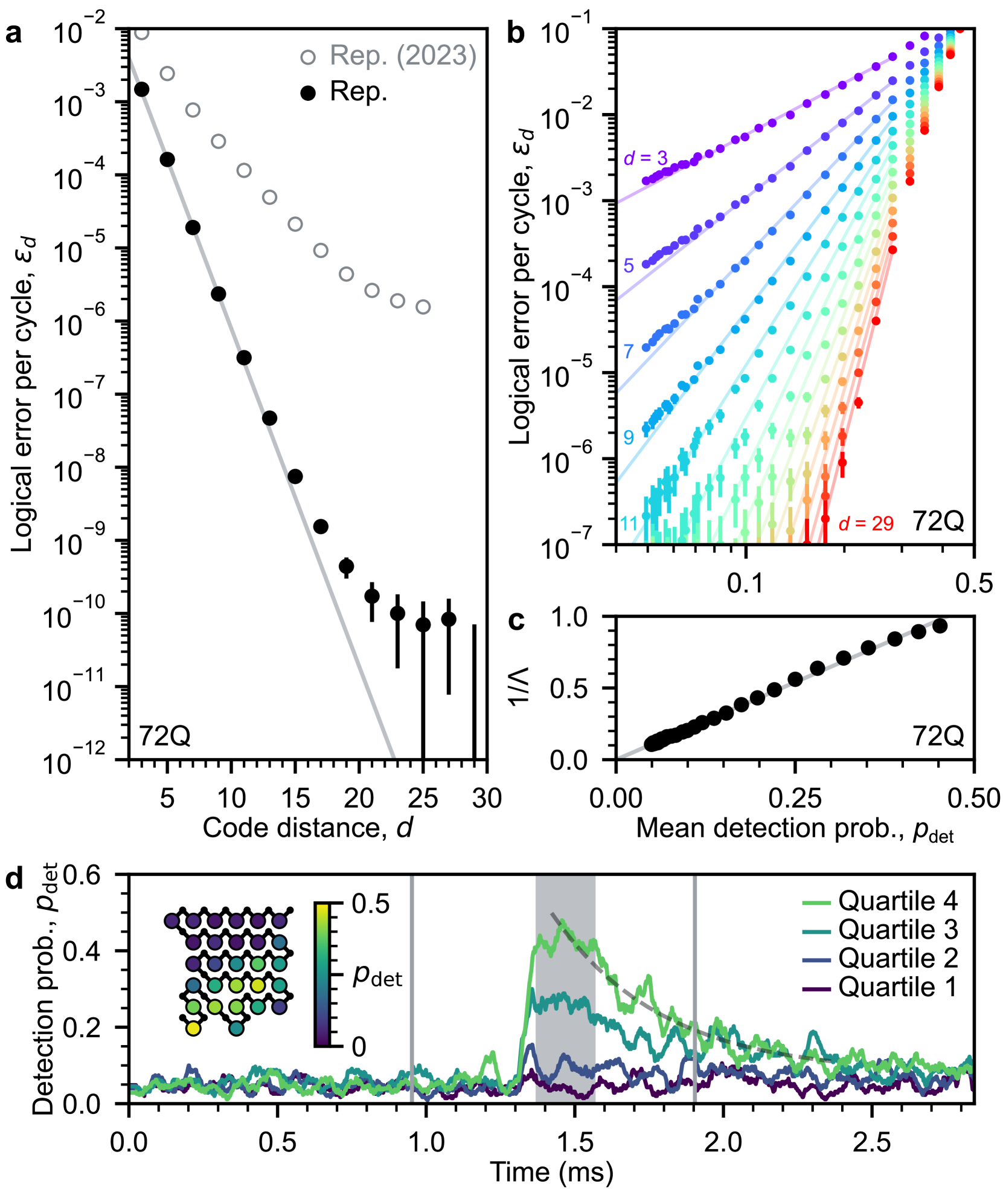

图 3:重复码中高码距的错误缩放。

a. 采用最小权重完美匹配解码时,逻辑每周期错误率εd与码距d的关系。重复码数据来自d=29、103 个周期的实验,X和Z基各 10⁷次重复。我们从相同的d=29数据集中子采样低码距重复码,对子采样结果取平均。直线:错误抑制因子Λ的拟合。纳入文献 [17] 的数据用于对比。b. 逻辑错误随注入错误的缩放。向所有量子比特注入一系列相干错误,以观测到的平均探测概率pdet作图。每个实验包含 10 个周期,取 10⁶次重复的平均。低码距同样从d=29数据集中子采样。直线:幂律拟合εd=Adpdet(d+1)/2(一个拟合参数Ad),限制条件为εd>10−7且pdet<0.3。c. 1/Λ随注入错误的缩放。典型的相对拟合不确定度为 2%。直线:拟合线。d. 导致探测概率升高的典型事件,其随时间常数 369±6 微秒呈指数衰减(灰色虚线)。绘制了三次连续实验的结果,由灰色竖线分隔。28 个测量量子比特根据灰色窗口内的平均探测概率分为四个四分位组。每条曲线代表一个四分位组的平均探测概率,时间窗口为 10 个周期。插图:灰色窗口内每个测量量子比特的平均探测概率(彩色圆点)。

我们使用 72 量子比特处理器运行距离 29 的重复码,进行 1000 个纠错周期的实验,总重复次数为 2×10⁷次,均匀分布在比特翻转和相位翻转码中。总计执行了 2×10¹⁰个纠错周期,处理器运行时间为 5.5 小时。基于 1000 个周期的逻辑错误概率pL,我们推断逻辑每周期错误率为εd=21(1−(1−2pL)1/1000)。为评估逻辑每周期错误率随码距d的缩放规律,我们遵循文献 [38] 的方法,从距离 29 的数据集中子采样低码距重复码。

对比特翻转和相位翻转重复码取平均,在拟合d=5至d=11的逻辑每周期错误率与码距关系时,我们得到错误抑制因子Λ=8.4±0.1,如图 3a 所示。值得注意的是,错误率被抑制至远低于 10⁻⁶,突破了此前观测的错误平台期。我们将高能撞击故障的缓解归因于间隙工程约瑟夫森结 [40]。然而,当码距d≥15时,我们观测到高码距下指数错误抑制的偏离,最终出现表观的 10⁻¹⁰逻辑错误平台期。尽管在距离 29 时未观测到任何错误,这可能是由于少数破坏性最强的错误爆发时随机解码正确所致。尽管该逻辑每周期错误率或许能满足部分容错应用 [11],但仍比预期高多个数量级,无法支撑更大规模的容错电路 [21,12]。

分析这些高码距逻辑故障的探测模式时,我们发现两种故障模式:第一种表现为一个或两个探测器的探测概率突然升高超过 3 倍,数十至数百个周期后恢复至初始值 [24]。这类破坏性较小的故障可能由量子比特工作频率附近出现的瞬态 TLS 或耦合器激发导致,可采用类似文献 [39,41] 的方法缓解。第二种更具灾难性的故障表现为多个探测器同时出现探测概率的大幅尖峰,如图 3d 所示。值得注意的是,这类各向异性错误爆发在空间上局限于约 30 个量子比特的区域(见插图)。在 2×10¹⁰个纠错周期中,处理器共发生 6 次这类大型错误爆发,是高码距故障的主要原因。这类爆发(如图 3d 所示的事件)与此前观测的高能撞击事件 [17] 不同,它们大约每小时发生一次(而非每几秒一次),且衰减时间常数约为 400 微秒(而非数十毫秒)。目前我们尚未明确这类事件的成因,但缓解它们仍是构建容错量子计算机的关键。这些结果再次证实,长重复码是发现量子处理器在逻辑噪声平台期新错误机制的关键工具。

此外,尽管我们已在低码距下验证了公式 1 的缩放规律,重复码使我们能够扫描至更高码距和更低逻辑错误。采用与表面码类似的相干错误注入方法,我们在图 3b-c 中展示了逻辑错误随物理错误和码距的缩放,观测到与O(p(d+1)/2)错误抑制的良好一致性。例如,将探测概率降低 2 倍,会使距离 15 时的逻辑错误率降低 250 倍,与预期的O(p8)缩放规律一致。这表明,若能在表面码中实现相近的错误抑制因子,最终将实现大规模容错量子计算机的显著错误抑制。

五、实时解码

除了高保真度的处理器,容错量子计算还需要能实时解码错误的经典协处理器。这是因为部分逻辑运算是非确定性的,其依赖于必须即时正确解读的逻辑测量结果 [23]。若解码器无法快速处理测量信息,校验子信息的累积会导致计算时间呈指数级增长。由于超导处理器的速度特性,实时解码极具挑战性:每个周期内校验子信息的传输、处理和解码吞吐量,必须与 1.1 微秒的快速纠错周期同步。我们以 72 量子比特处理器为平台,在容错量子计算架构的这一核心模块上,实现了低于阈值的运行性能。

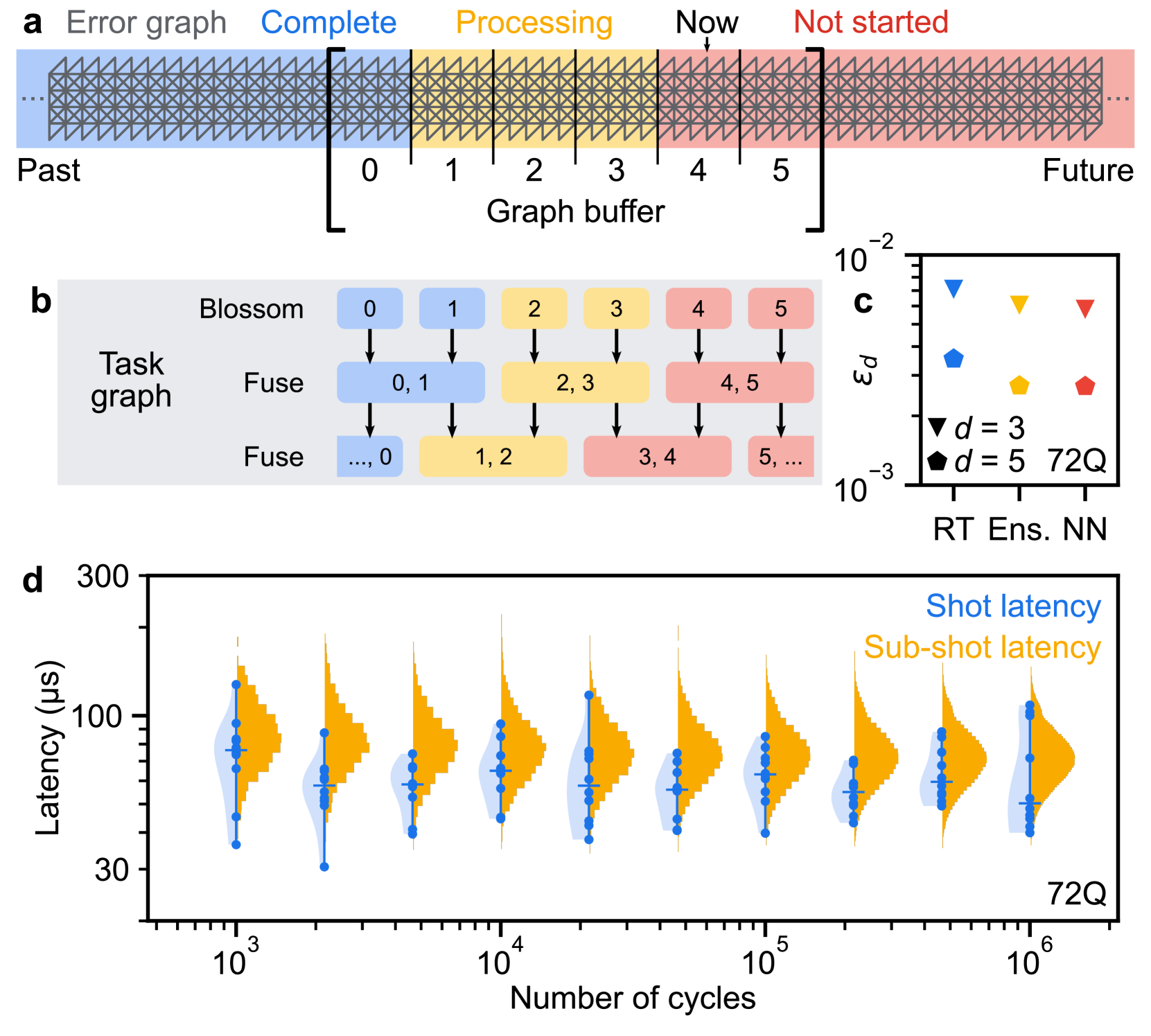

我们的解码系统始于经典控制电子器件:测量信号被分类为比特流,随后通过低延迟以太网传输至专用工作站;在工作站内,测量数据被转换为探测事件,再通过共享内存缓冲区流式传输至实时解码软件。我们采用稀疏 Blossom 算法的专用版本 [42],优化后可快速解析表面码解码中常见的局部错误配置,并行化策略与文献 [43] 类似。解码器运行在固定大小的图缓冲区中,模拟当前解码的错误图区域,且不随实验总周期数增长。不同线程负责图的不同时空区域,在流式传输校验子信息时处理对应区域 [44,45,43,46],最终融合结果以得到全局最小权重完美匹配。流式解码算法如图 4a-b 所示。我们还采用贪心边缘重加权策略,考虑 Y 型错误诱导的关联效应,提升解码精度 [29,47]。

图 4d 中,我们报告了解码器延迟,定义为解码软件接收最后一个周期的校验子测量结果,至解码器返回校正结果的时间。对于距离 5 表面码,我们通过增加纠错周期数至 10⁶来测试不同问题规模,观测到平均延迟基本保持在 63±17 微秒的净平均值,与实验时长(最长 1.1 秒)无关,表明解码问题正在实时处理。该延迟最终将决定逻辑处理器执行非克利福德门的响应时间,目前尚未包含对逻辑电路的反馈。

重要的是,即使在实时解码的严格时序要求下,我们仍能保持低于阈值的性能。我们在 72 量子比特处理器上开展专门实验,对比实时解码与相同数据的离线高精度神经网络解码,结果如图 4c 所示。我们的实时解码器使用与器件数据无关的先验,实现了ε5=0.35%±0.01%,Λ=2.0±0.1;而神经网络解码器离线解码时,实现了ε5=0.269%±0.008%,Λ=2.18±0.09。实时解码器与离线解码器的精度小幅下降是预期之内的,因为实时解码器必须运行得更快:每个周期的处理吞吐量需小于 1.1 微秒,而神经网络解码器为 24 微秒 / 周期 [27]。不过,我们预计通过引入分层解码、窗口解码等技术 [44,45,28],许多高精度解码方法最终可实现实时解码。

图 4:实时解码。

a. 流式解码算法的示意图。解码问题被划分为多个块,不同线程负责不同块。b. 处理块的任务图。探测事件允许匹配至块边界,随后在融合步骤中进行下游处理。若探测事件的配置无法通过后续融合步骤解决,解码器会标记故障。我们使用 10 个周期的块,确保标记的故障概率远低于逻辑故障概率。c. 表面码的三种解码器精度对比。包括实时解码器(RT)、集成匹配合成解码器(Ens.)和神经网络解码器(NN)。每个点的不确定度小于 10⁻⁴[24]。d. 解码器延迟与实验时长的关系。蓝色点对应单次实验结束的延迟(每个时长 10 次实验,水平条:中位数,蓝色阴影:小提琴图);黄色直方图表示子单次延迟:通过统计每个 10 周期块的数据接收后,解码器完成该块的时间得到。子单次延迟通常略长于单次实验结束延迟,因为解码器可能需要等待未来周期的探测事件融合,以处理当前周期的数据。

六、展望

在本研究中,我们实现了低于阈值的表面码量子存储器。每次码距增加 2,逻辑每周期错误率便降低超过一半,最终使距离 7 码的寿命超过其最优组成物理量子比特寿命的两倍。这种逻辑错误率随码距呈指数级被抑制的特性,为开展纠错的大规模量子算法奠定了基础。

我们的纠错处理器还在容错量子计算领域展现了其他关键进展:数小时内实现了可重复的性能,且 10⁶个周期的实验未出现性能退化,这是未来大规模容错算法的必要条件;此外,我们设计的实时解码系统,与离线解码器相比精度仅小幅下降。

尽管如此,我们仍面临诸多挑战。尽管原则上可通过扩展现有处理器实现低逻辑错误率,但实际中会耗费大量资源。根据图 1d 的预测,实现 10⁻⁶的错误率需要 1457 个物理量子比特的距离 27 逻辑量子比特。码距的增加还会带来实时解码的额外挑战,每个周期的校验子测量数量随码距呈二次增长。我们的重复码实验还发现,由关联错误爆发导致的错误平台期为 10⁻¹⁰,识别并缓解这类错误机制对运行更大规模量子算法至关重要。

不过,量子纠错也为通过处理器改进降低逻辑错误提供了指数级的优势。例如,将物理错误率降低 2 倍,可使距离 27 的逻辑性能提升四个数量级,达到与算法相关的错误率区间 [11,12]。我们还预计,随着纠错协议 [48,49,50,51,52,53,54] 和解码技术 [55,56,57] 的进步,这类资源开销将进一步降低。

量子纠错的目标是实现大规模量子算法。尽管本研究聚焦于构建鲁棒的量子存储器,逻辑计算还将面临额外挑战 [58,59]。在经典层面,我们必须确保校准协议、实时解码器、逻辑编译器等软件组件,能够扩展至运行多表面码操作所需的规模和复杂度 [60]。借助低于阈值的表面码,我们已展示了原则上可扩展的处理器性能,如今需将其转化为实际的规模化应用。

七、作者贡献

谷歌量子人工智能团队构思并设计了实验。谷歌量子人工智能的理论和实验团队开发了支撑实验的数据分析、建模和计量工具,搭建了系统、完成了校准并收集了数据。所有作者撰写并修订了本文稿及补充信息。

八、致谢

感谢 S. Brin、S. Pichai、R. Porat 和 J. Manyika 对谷歌量子人工智能团队的行政支持,以及他们持续的参与和帮助。

九、伦理声明

作者声明无利益冲突。

十、补充信息

本文附有补充材料。相关通讯及材料索取请联系 H. Neven(邮箱:neven@google.com)。

十一、数据可用性

支持本研究结果的数据可在https://doi.org/10.5281/zenodo.13273331获取。

谷歌量子人工智能团队及合作者(作者单位列表略,详见原文)

References

[1]

Shor, P. W. Scheme for reducing decoherence in quantum computer memory. Physical Review A 52, R2493 (1995).

[2]

Gottesman, D. Stabilizer codes and quantum error correction (California Institute of Technology, 1997).

[3]

Dennis, E., Kitaev, A. Y., Landahl, A. & Preskill, J. Topological quantum memory. Journal of Mathematical Physics 43, 4452--4505 (2002).

[4]

Kitaev, A. Y. Fault-tolerant quantum computation by anyons. Annals of Physics 303, 2--30 (2003).

[5]

Aspuru-Guzik, A., Dutoi, A. D., Love, P. J. & Head-Gordon, M. Simulated quantum computation of molecular energies. Science 309, 1704--1707 (2005).

[6]

Lloyd, S. Universal quantum simulators. Science 273, 1073--1078 (1996).

[7]

Shor, P. W. Polynomial-time algorithms for prime factorization and discrete logarithms on a quantum computer. SIAM Review 41, 303--332 (1999).

[8]

Farhi, E. et al. A quantum adiabatic evolution algorithm applied to random instances of an NP-complete problem. Science 292, 472--475 (2001).

[9]

McKay, D. C. et al. Benchmarking quantum processor performance at scale. arXiv preprint arXiv:2311.05933 (2023).

[10]

DeCross, M. et al. The computational power of random quantum circuits in arbitrary geometries. arXiv preprint arXiv:2406.02501 (2024).

[11]

Campbell, E. T. Early fault-tolerant simulations of the Hubbard model. Quantum Science and Technology 7, 015007 (2021).

[12]

Kivlichan, I. D. et al. Improved fault-tolerant quantum simulation of condensed-phase correlated electrons via Trotterization. Quantum 4, 296 (2020).

[13]

Fowler, A. G., Mariantoni, M., Martinis, J. M. & Cleland, A. N. Surface codes: Towards practical large-scale quantum computation. Physical Review A---Atomic, Molecular, and Optical Physics 86, 032324 (2012).

[14]

Ryan-Anderson, C. et al. Realization of real-time fault-tolerant quantum error correction. Physical Review X 11, 041058 (2021).

[15]

Krinner, S. et al. Realizing repeated quantum error correction in a distance-three surface code. Nature 605, 669--674 (2022).

[16]

Sivak, V. V. et al. Real-time quantum error correction beyond break-even. Nature 616, 50--55 (2023).

[17]

Google Quantum AI. Suppressing quantum errors by scaling a surface code logical qubit. Nature 614, 676--681 (2023).

[18]

Bluvstein, D. et al. Logical quantum processor based on reconfigurable atom arrays. Nature 626, 58--65 (2024).

[19]

Gupta, R. S. et al. Encoding a magic state with beyond break-even fidelity. Nature 625, 259--263 (2024).

[20]

Da Silva, M. et al. Demonstration of logical qubits and repeated error correction with better-than-physical error rates. arXiv preprint arXiv:2404.02280 (2024).

[21]

Gidney, C. & Ekerå, M. How to factor 2048 bit RSA integers in 8 hours using 20 million noisy qubits. Quantum 5, 433 (2021).

[22]

Terhal, B. M. & Burkard, G. Fault-tolerant quantum computation for local non-Markovian noise. Physical Review A---Atomic, Molecular, and Optical Physics 71, 012336 (2005).

[23]

Terhal, B. M. Quantum error correction for quantum memories. Reviews of Modern Physics 87, 307--346 (2015).

[24]

Google Quantum AI and Collaborators. Supplementary Information for "Quantum error correction below the surface code threshold".

[25]

Koch, J. et al. Charge-insensitive qubit design derived from the Cooper pair box. Physical Review A---Atomic, Molecular, and Optical Physics 76, 042319 (2007).

[26]

Arute, F. et al. Quantum supremacy using a programmable superconducting processor. Nature 574, 505--510 (2019).

[27]

Bausch, J. et al. Learning to decode the surface code with a recurrent, transformer-based neural network. arXiv preprint arXiv:2310.05900 (2023).

[28]

Shutty, N., Newman, M. & Villalonga, B. Efficient near-optimal decoding of the surface code through ensembling. arXiv preprint arXiv:2401.12434 (2024).

[29]

Fowler, A. G. Optimal complexity correction of correlated errors in the surface code. arXiv preprint arXiv:1310.0863 (2013).

[30]

Jones, C. Improved accuracy for decoding surface codes with matching synthesis. arXiv preprint arXiv:2408.12135 (2024).

[31]

Sivak, V., Newman, M. & Klimov, P. Optimization of decoder priors for accurate quantum error correction. arXiv preprint arXiv:2406.02700 (2024).

[32]

Bonilla Ataides, J. P., Tuckett, D. K., Bartlett, S. D., Flammia, S. T. & Brown, B. J. The XZZX surface code. Nature Communications 12, 2172 (2021).

[33]

Miao, K. C. et al. Overcoming leakage in quantum error correction. Nature Physics 19, 1780--1786 (2023).

[34]

Hesner, I., Hetényi, B. & Wootton, J. R. Using detector likelihood for benchmarking quantum error correction. arXiv preprint arXiv:2408.02082 (2024).

[35]

Klimov, P. V. et al. Optimizing quantum gates towards the scale of logical qubits. Nature Communications 15, 2442 (2024).

[36]

Ofek, N. et al. Extending the lifetime of a quantum bit with error correction in superconducting circuits. Nature 536, 441--445 (2016).

[37]

Ni, Z. et al. Beating the break-even point with a discrete-variable-encoded logical qubit. Nature 616, 56--60 (2023).

[38]

Chen, Z. et al. Exponential suppression of bit or phase flip errors with repetitive error correction. Nature 595, 383--387 (2021).

[39]

Varbanov, B. M. et al. Leakage detection for a transmon-based surface code. npj Quantum Information 6, 102 (2020).

[40]

McEwen, M. et al. Resisting high-energy impact events through gap engineering in superconducting qubit arrays. arXiv preprint arXiv:2402.15644 (2024).

[41]

Strikis, A., Benjamin, S. C. & Brown, B. J. Quantum computing is scalable on a planar array of qubits with fabrication defects. Physical Review Applied 19, 064081 (2023).

[42]

Higgott, O. & Gidney, C. Sparse Blossom: correcting a million errors per core second with minimum-weight matching. arXiv preprint arXiv:2303.15933 (2023).

[43]

Wu, Y. & Zhong, L. Fusion Blossom: Fast MWPM decoders for QEC. In 2023 IEEE International Conference on Quantum Computing and Engineering (QCE), vol. 1, 928--938 (IEEE, 2023).

[44]

Skoric, L., Browne, D. E., Barnes, K. M., Gillespie, N. I. & Campbell, E. T. Parallel window decoding enables scalable fault tolerant quantum computation. Nature Communications 14, 7040 (2023).

[45]

Tan, X., Zhang, F., Chao, R., Shi, Y. & Chen, J. Scalable surface-code decoders with parallelization in time. PRX Quantum 4, 040344 (2023).

[46]

Bombín, H. et al. Modular decoding: parallelizable real-time decoding for quantum computers. arXiv preprint arXiv:2303.04846 (2023).

[47]

Paler, A. & Fowler, A. G. Pipelined correlated minimum weight perfect matching of the surface code. Quantum 7, 1205 (2023).

[48]

Litinski, D. & Nickerson, N. Active volume: An architecture for efficient fault-tolerant quantum computers with limited non-local connections. arXiv preprint arXiv:2211.15465 (2022).

[49]

Chamberland, C. & Campbell, E. T. Universal quantum computing with twist-free and temporally encoded lattice surgery. PRX Quantum 3, 010331 (2022).

[50]

Bravyi, S. et al. High-threshold and low-overhead fault-tolerant quantum memory. Nature 627, 778--782 (2024).

[51]

Xu, Q. et al. Constant-overhead fault-tolerant quantum computation with reconfigurable atom arrays. Nature Physics 1--7 (2024).

[52]

Gidney, C., Newman, M., Brooks, P. & Jones, C. Yoked surface codes. arXiv preprint arXiv:2312.04522 (2023).

[53]

Gidney, C. Inplace access to the surface code Y basis. Quantum 8, 1310 (2024).

[54]

Cain, M. et al. Correlated decoding of logical algorithms with transversal gates. arXiv preprint arXiv:2403.03272 (2024).

[55]

Smith, S. C., Brown, B. J. & Bartlett, S. D. Local predecoder to reduce the bandwidth and latency of quantum error correction. Physical Review Applied 19, 034050 (2023).

[56]

Barber, B. et al. A real-time, scalable, fast and highly resource efficient decoder for a quantum computer. arXiv preprint arXiv:2309.05558 (2023).

[57]

Liyanage, N., Wu, Y., Tagare, S. & Zhong, L. FPGA-based distributed union-find decoder for surface codes. arXiv preprint arXiv:2406.08491 (2024).

[58]

Gidney, C. Stability experiments: the overlooked dual of memory experiments. Quantum 6, 786 (2022).

[59]

Lin, S. F., Peterson, E. C., Sankar, K. & Sivarajah, P. Spatially parallel decoding for multi-qubit lattice surgery. arXiv preprint arXiv:2403.01353 (2024).

[60]

Bombin, H. et al. Logical blocks for fault-tolerant topological quantum computation. PRX Quantum 4, 020303 (2023).