硅片集成扇出技术(SWIFT®)设计是一种面向应用处理器(AP)的先进扇出型晶圆级封装(FOWLP)方法,具有外形尺寸小、图形密度高和三维堆叠的特点------通常将内存(顶部封装)堆叠在AP(底部封装)之上。FOWLP在封装体积和厚度两方面均具有实现显著小型化的巨大潜力。其主要优势包括无基板封装、热阻低以及射频(RF)性能优异,这得益于采用薄膜金属化实现的短互连(而非引线键合或倒装芯片bump),从而产生低寄生效应。在堆叠封装(PoP)中,传统层压有机基板已达到设计密度极限,而SWIFT封装可对其进行替代。

FOWLP具有诸多显著优势。首先,它减小了包括封装z向高度在内的外形尺寸。封装厚度对信号完整性和电源完整性具有关键影响,因为随着封装高度的变化,传导路径也会发生改变。与同类层压技术相比,SWIFT封装的厚度减少了约30%,因此实现了大幅改进。其次,它能够提供更精细的图形,可支持高达2/2um(宽度/间距)的超高布线密度,从而增加了输入/输出(I/O)数量并维持了走线之间的间距。

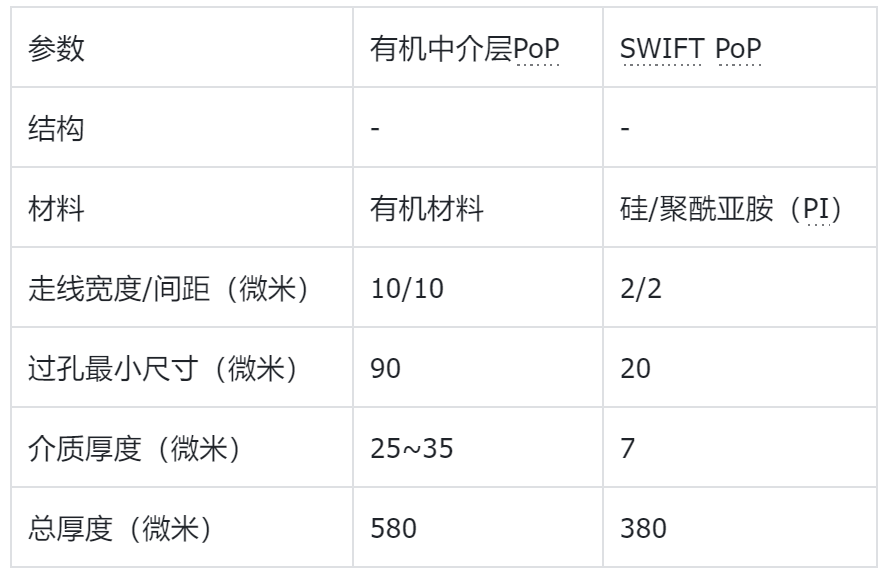

如表I所示,有机中介层PoP与SWIFT PoP的设计规则存在巨大差异,尤其是在过孔、走线和介质厚度方面,这些参数能够将大量I/O从芯片路由至球栅阵列(BGA)或内存。由于过孔尺寸减小至20um,金属间间距可进一步加宽,并且可在信号走线之间添加更多微过孔,这有助于缓解串扰问题。然而,FOWLP和SWIFT封装并不能保证一定改善串扰问题,因为信号走线宽度/间距(W/S)和过孔的大幅减小会导致信号之间的间距相应缩小,反而可能加剧串扰。因此,必须在预制造阶段确定最佳设计规则和结构。此外,接地防护走线以及在接地防护走线上添加接地过孔可缓解串扰问题,许多研究人员已在有机基板中采用了这一方法。分析了适用于SWIFT封装的有机基板设计规则,并提出了用于抑制串扰的最佳设计技术。

串扰效应会显著降低信号质量,进而影响晶圆级封装的信号完整性。如果在双倍数据速率(DDR)和高带宽内存(HBM)等高速通道上串扰效应严重,可能会导致数据传输失败。因此,应在预制造过程中对串扰效应进行预估,并通过频域分析预估来验证信号性能。

表I PoP结构对比表

电路建模

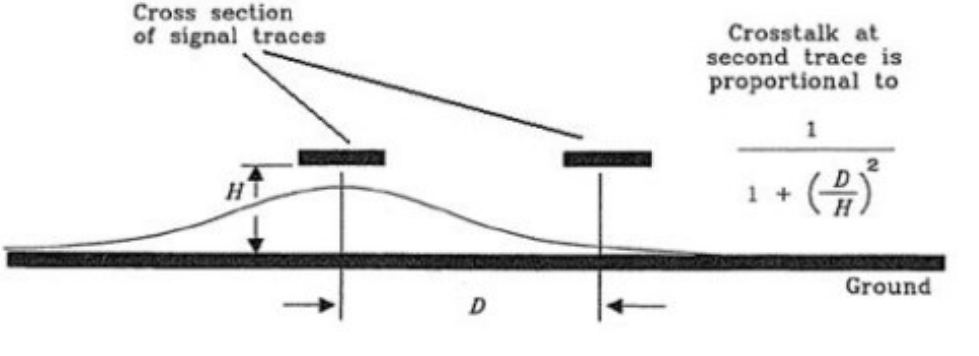

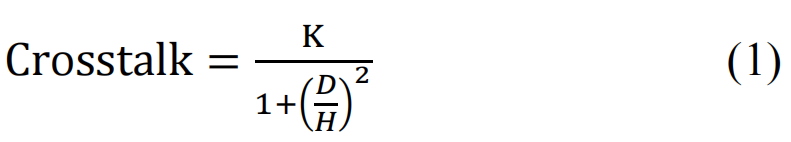

两条导体之间的串扰取决于它们的互感和互容。在高速单端内存通道或串行器/解串器(SerDes)等数字信号中,感性串扰与容性串扰相当或更大。因此,下面主要讨论感性耦合机制。集总电路的互感耦合考虑返回信号电流会产生磁场,这些磁场进而在其他电路走线上感应出电压。假设随着两条走线之间间距的增加,互感串扰也会减小,因此可通过在信号旁边添加共面接地导带并减小介质厚度来实现:

图1展示了串扰与H和D的比值关系,其中H表示介质厚度,D表示走线间距及其接地防护走线。因此,可通过走线间距和介质厚度来控制串扰效应。常数K取决于电路上升时间和干扰走线的长度,且始终小于1。

图1. 显示串扰的两条走线的横截面。

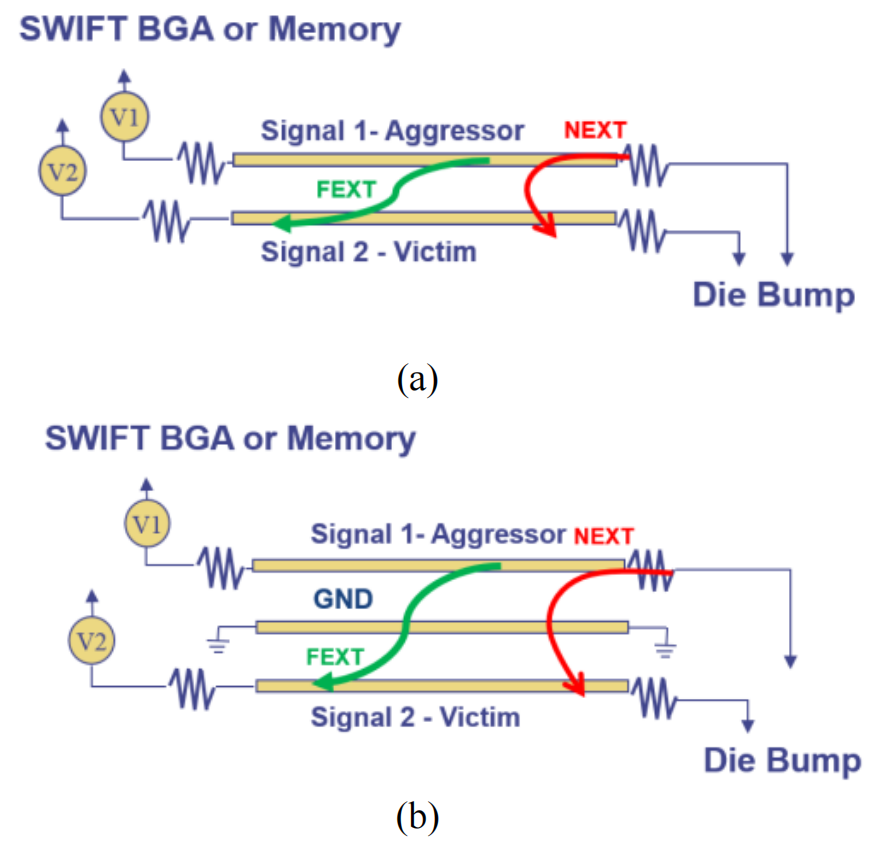

为简化分析,图2(a)展示了从芯片bump到顶部BGA或内存的两条平行微带线的电路模型;图2(b)展示了两条平行微带线之间带有接地防护走线的电路模型。在接地防护走线上添加了接地过孔,以评估接地过孔的效益。

图2. (a)从芯片bump到顶部BGA的两条耦合传输线;(b)两条信号之间带有接地防护走线的耦合传输线。

图形布局基础

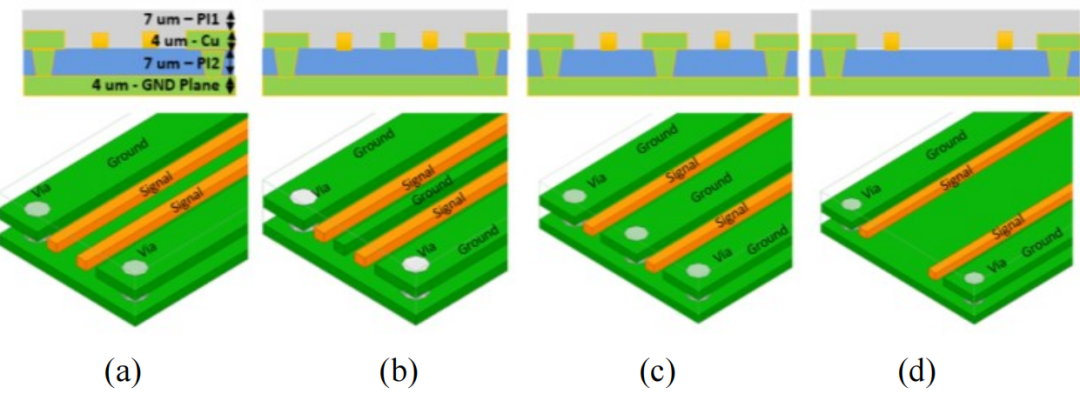

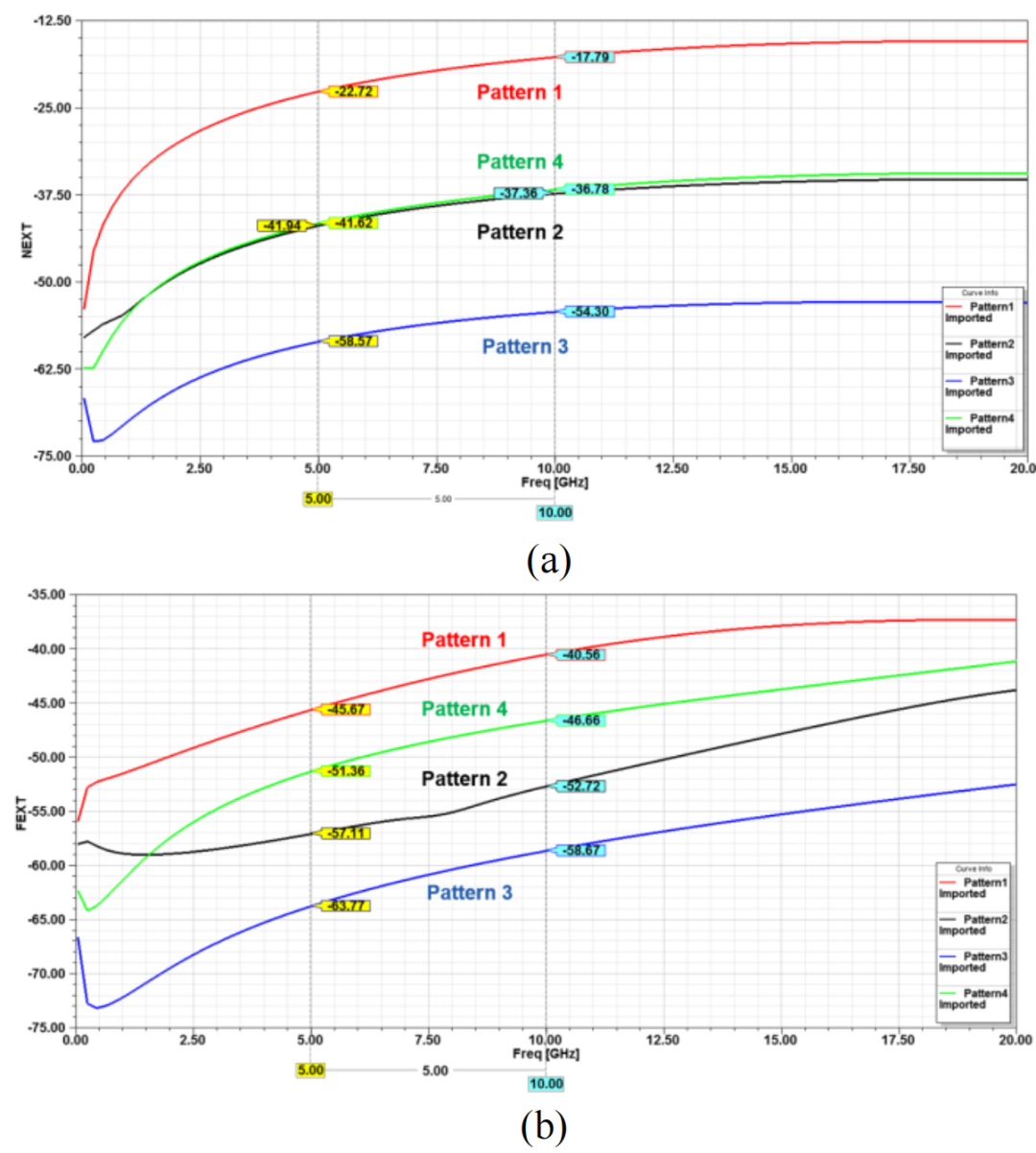

在进行实际设计分析之前,基于公式(1),选取了SWIFT封装理想环境下的简化初步布局,以验证与接地防护走线、过孔和走线间距相关的串扰性能。在理想环境中,如图4所示,信号走线间距更宽且在走线两端设置接地过孔时,近端串扰(NEXT)和远端串扰(FEXT)的串扰噪声最低,不同方案之间的结果差异在10GHz时最大可达37dB。由于图4(a)中方案2和方案4的NEXT串扰水平相近,因此接地防护走线预计将在抑制串扰方面发挥重要作用。此外,尽管图3中方案4的走线间距比方案2更宽,但图4(b)中方案2的FEXT性能优于方案4。因此,基于图4中NEXT和FEXT的结果,这些走线布局成为了实际走线图形设计的基础。

图3. 简化布局:(a)方案1、(b)方案2、(c)方案3、(d)方案4。

设计的频域分析

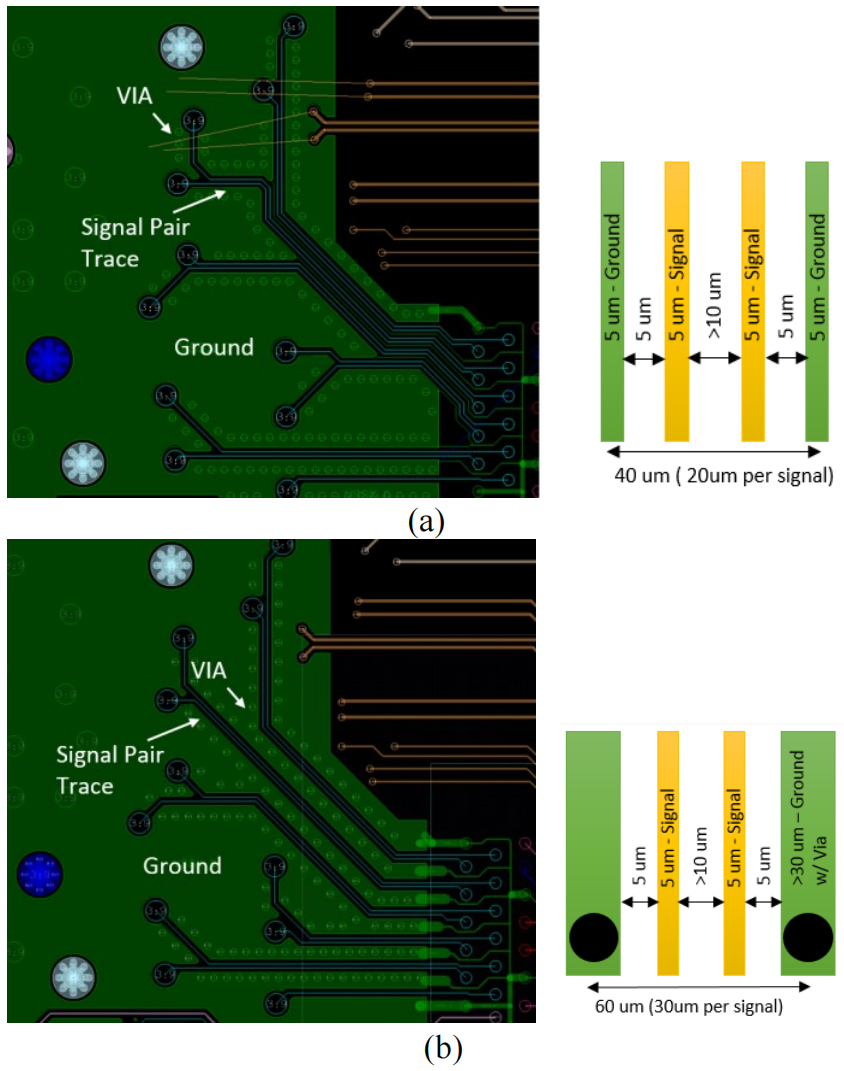

图5展示了不同的实际设计和建模配置设置,用于评估从干扰线到受害线的串扰。各种配置的关键参数是微带线结构中从芯片焊盘到顶部内存BGA的走线间距,这是图6所示PoP结构中最严苛的连接条件。

图4. 理想环境下的S参数分析:(a)NEXT、(b)FEXT。

图5. (a)方案1:带有接地防护走线的一对信号;(b)方案2:带有厚防护走线和过孔的一对信号;(c)方案3:带有防护走线和过孔的单条信号;(d)方案4:带有防护走线但无过孔的单条信号;(e)方案5:带有防护走线的单条信号。

图6. 从芯片bump到顶部内存BGA的信号走线路由。

图5(a)中的设计是在重分布层(RDL)1中,一对单端信号围绕接地防护走线布置,以容纳多个I/O;而图5(b)展示了一对单端信号,周围设有带过孔的接地(防护走线)。图5(c)中的布局是每条单条信号走线都配有接地防护走线和过孔,但I/O数量最少,预计将实现最佳的串扰抑制效果。图5(d)中的设计与图5(c)类似,但移除了信号之间的接地过孔,以测量无接地过孔时的串扰相关性。在图5(e)中,每条单条信号走线都配有接地防护走线,但无过孔。

实验结果与讨论

A. 重分布层(RDL)走线图案变化

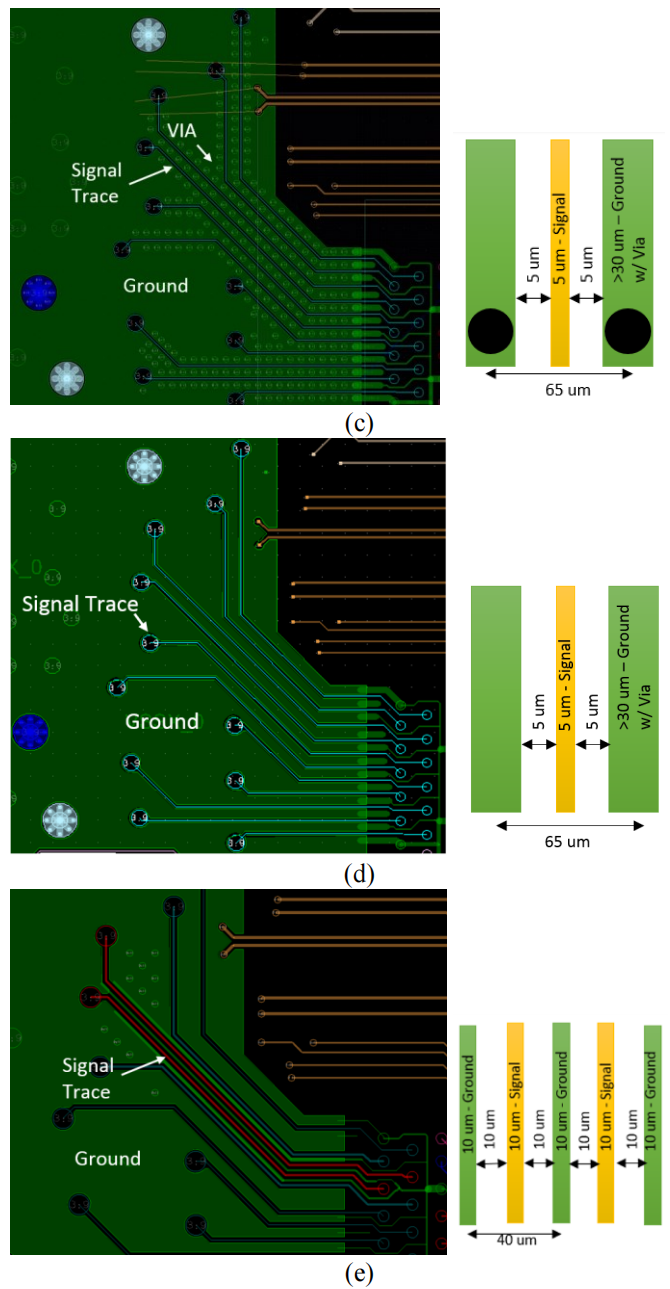

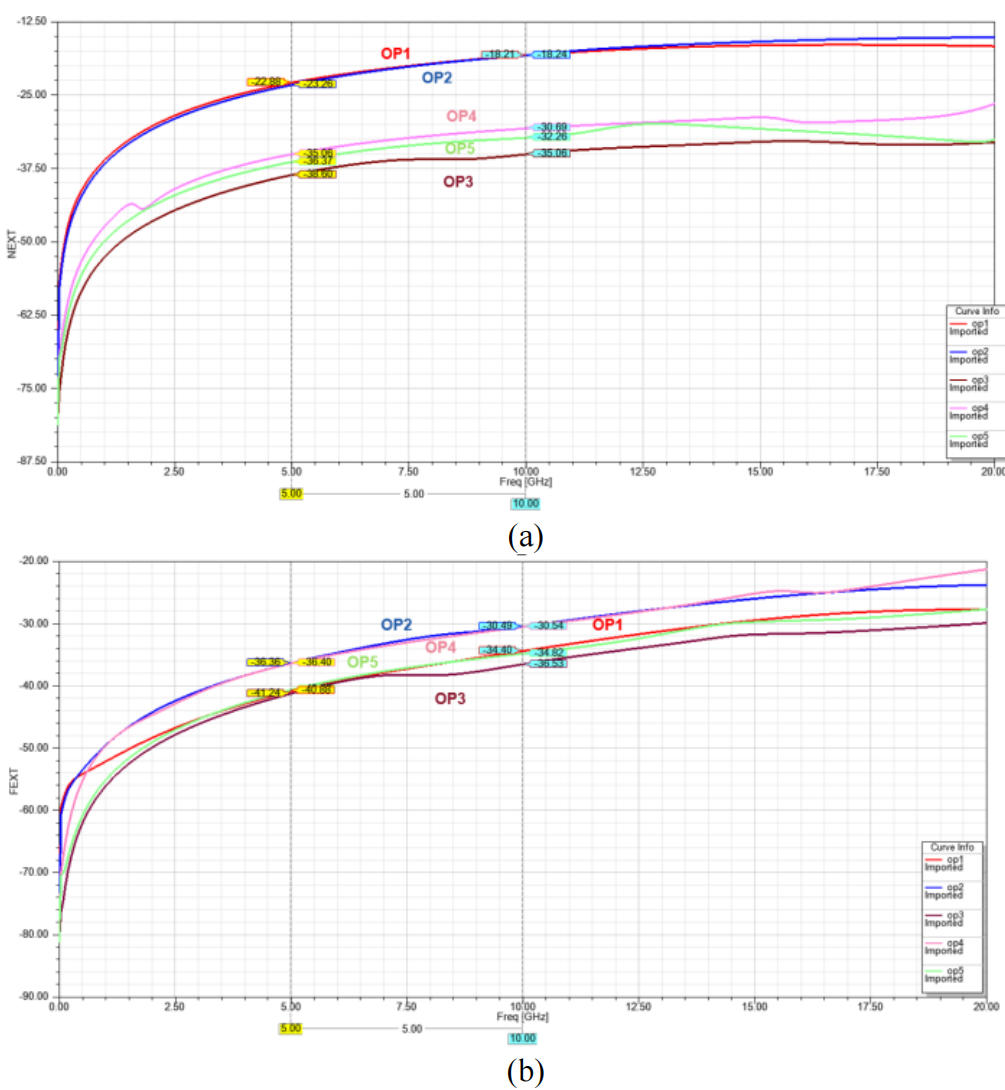

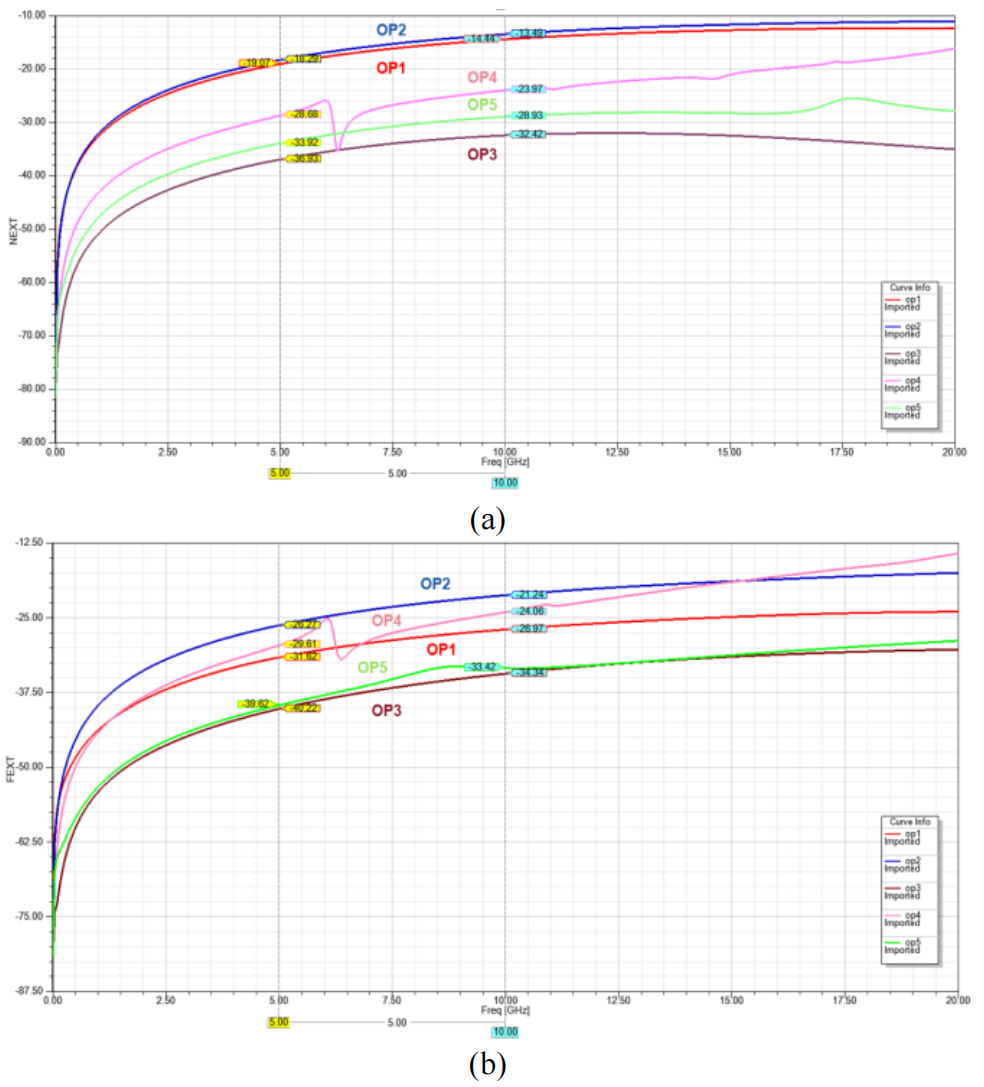

图7展示了不同走线布局和图案在不同频率下的NEXT和FEXT特性对比结果。

图7. S参数:(a)NEXT、(b)FEXT。

对比图7中五种方案的NEXT和FEXT结果可以发现,图5(c)中的方案3(带有接地防护走线和过孔的单条信号)实现了最佳的串扰改善效果,而方案1和方案2的效果最差,因为干扰信号和受害信号之间的间距最近。方案2(图5(b))与方案1(图5(a))相比未显示任何改善,这是因为该模型中由于未保持足够的信号间距,串扰本已恶化,添加接地过孔并未起到作用。然而,与方案3相比,方案4(图5(d))中移除接地过孔导致串扰恶化。方案5(图5(e))取得了与方案3相近的良好串扰结果。

接地防护走线有助于消除额外噪声耦合到受害线的可能性,将接地防护走线的末端短接到接地平面,可减少沿接地防护走线出现的NEXT噪声。此外,通过对比图7(b)中方案3和方案4的FEXT结果可以看出,添加接地过孔能够降低FEXT噪声。

如表II所示,方案3的串扰噪声水平最低,但需要较大的基板面积,这意味着由于每条信号走线和接地防护走线需要65um的间距,信号走线无法路由大量信号。因此,选择了方案5作为设计权衡方案,其串扰噪声水平与方案3相近,且能够实现更高密度的布线,是一种切实可行的布局。

表II 布局的串扰对比表

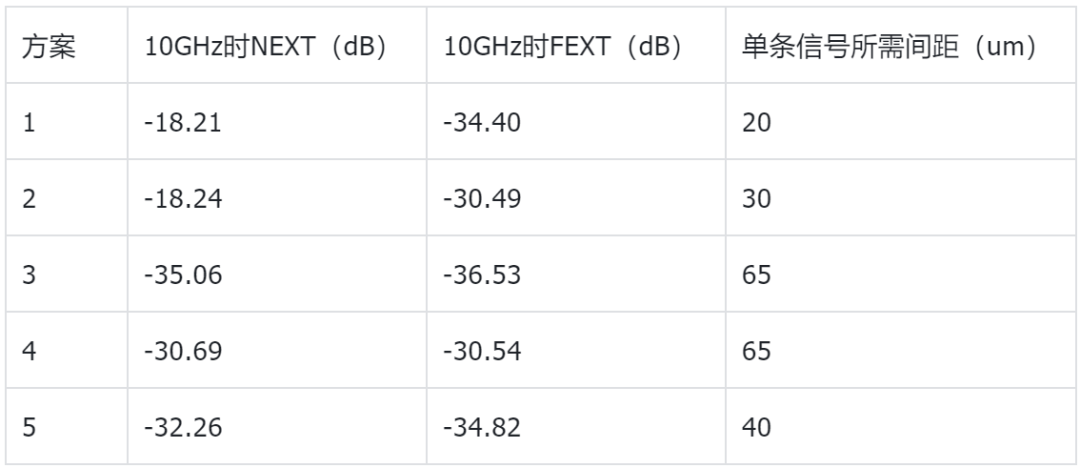

B. 聚酰亚胺(PI)厚度变化

研究了7um和35um两种介质厚度(这是该领域最常用的介质厚度)。图8展示了在10GHz下使用二维场求解器模拟的边缘场,其中厚聚酰亚胺(PI)版本增加了两条信号之间的耦合。当信号走线和bump焊盘间距固定时,使用薄PI版本能够减少信号之间的噪声耦合。

图8. (a)7umPI厚度下的电场;(b)7umPI厚度下的磁场;(c)35umPI厚度下的电场;(d)35umPI厚度下的磁场。

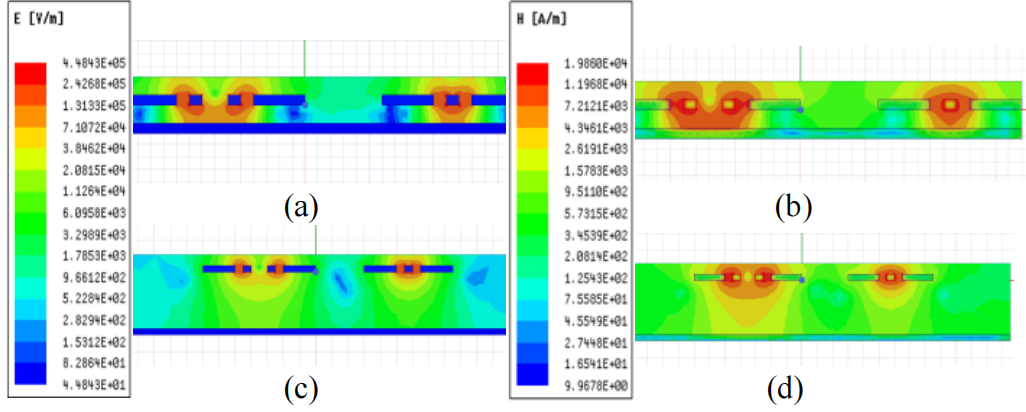

表III展示了7um和35umPI厚度的结果对比。35umPI版本的串扰结果更差,尤其是方案1和方案2(信号间距窄且无接地防护走线)的FEXT。信号之间带有接地防护走线的方案3和方案5受PI厚度变化的影响较小。

表III中"差值(Δ)"表示每种介质厚度下方案1至方案5的NEXT和FEXT的最差结果与最佳结果之间的差异。如图9所示,35um介质厚度下各方案的串扰结果偏差大于7um版本,且这种偏差也可能随介电常数的变化而变化。使用介电常数更低的介质材料,NEXT和FEXT均可降低2至3dB。薄介质版本应是抗串扰结构。

表III 10GHz下不同PI厚度的布局对比表

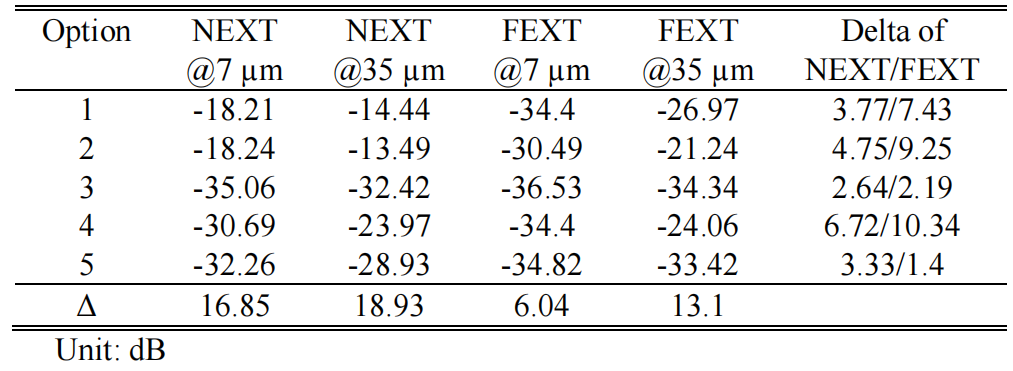

图9. 35um PI厚度下的S参数:(a)NEXT、(b)FEXT。

C. 带开路短截线的防护走线

接地防护走线有助于抑制串扰噪声,因此开展了额外研究,以探究带开路短截线的防护走线对串扰的影响------因为在SWIFT封装中,它可能会降低耦合微带线的性能。

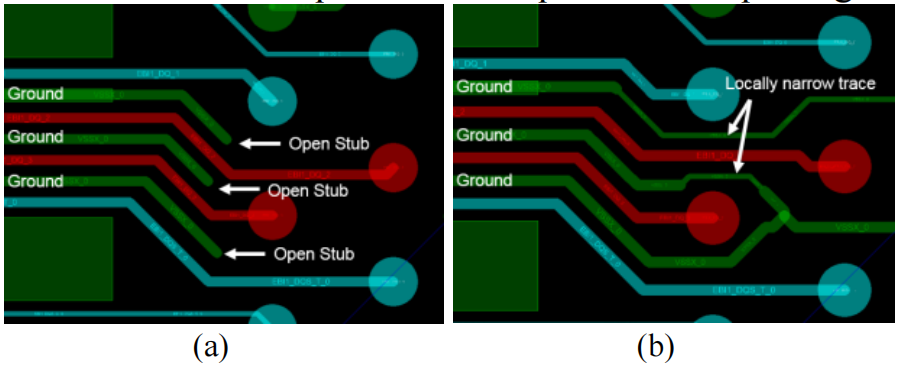

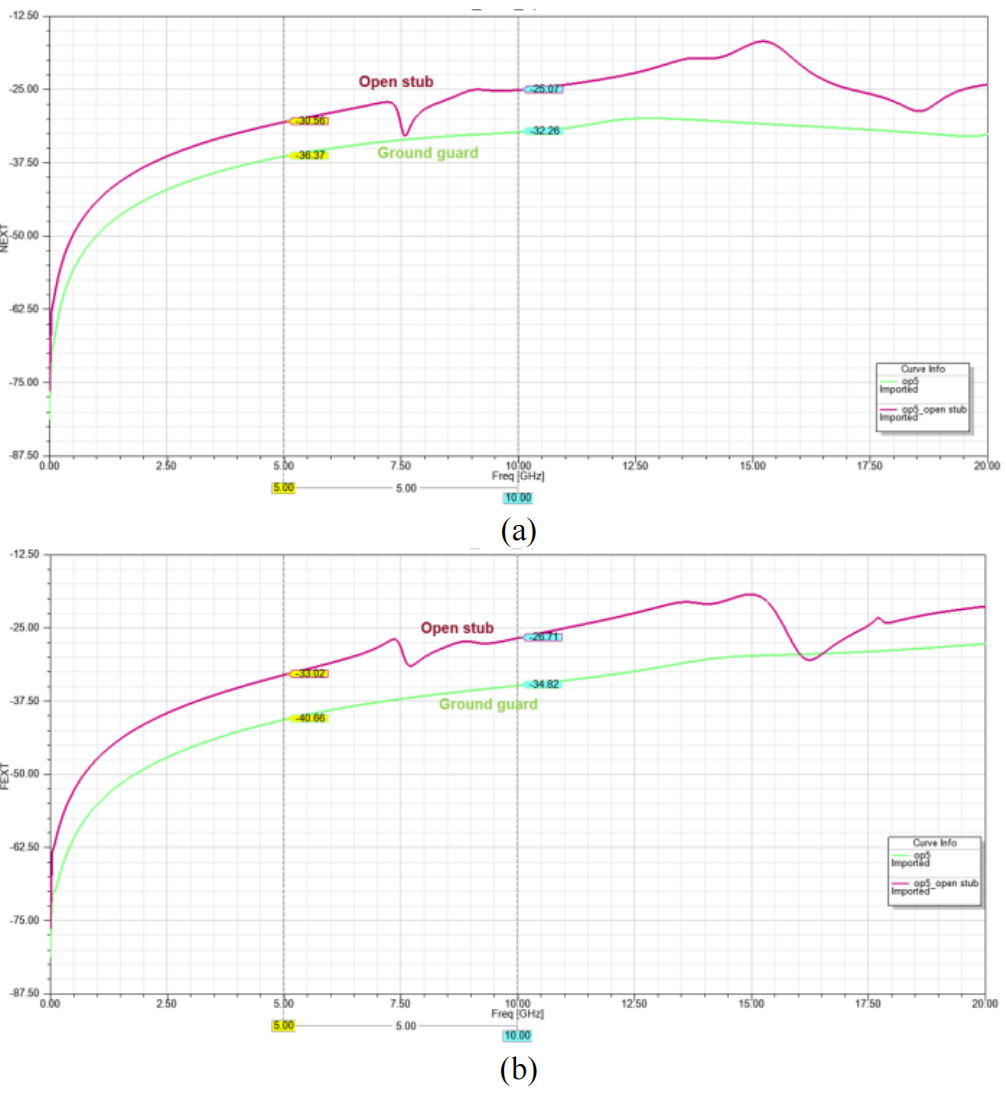

图10. (a)开路短截线接地防护;(b)全路由接地防护。

在实际SWIFT封装中,由于高I/O密度要求窄bump间距,通常会设置带开路短截线的防护走线(图10(a))。图10(b)显示,在设计权衡方案中,与图10(a)相比,采用2至5um的走线宽度/间距和10um的信号走线宽度/间距作为全局规则,对接地防护走线进行了完整路由------因为SWIFT封装能够实现精细的走线图形和过孔。图11展示了开路短截线模型与全接地防护模型的对比。这些设计几乎完全相同,唯一的区别在于图10所示的防护走线布局。图10(a)中,全接地防护模型相较于开路短截线模型实现了显著的性能提升。因此,如果实际布局条件限制只能添加防护走线,建议插入局部窄走线以避免接地短截线。

图11. 开路短截线与全防护走线模型的S参数对比:(a)NEXT、(b)FEXT测量结果。

D. bump图形

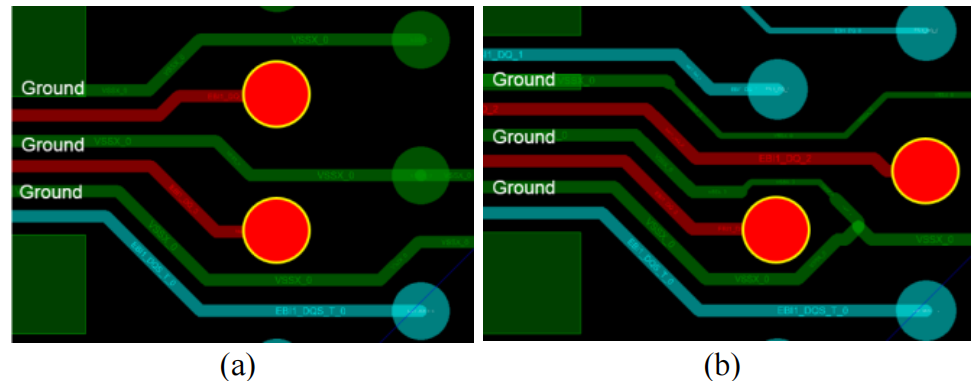

图12展示了两种不同的bump图形,用于研究信号bump焊盘分布的影响。测试结构的唯一区别在于接地bump焊盘周围的bump图形。

图12. 信号间耦合:(a)直列bump、(b)交错bump图形。

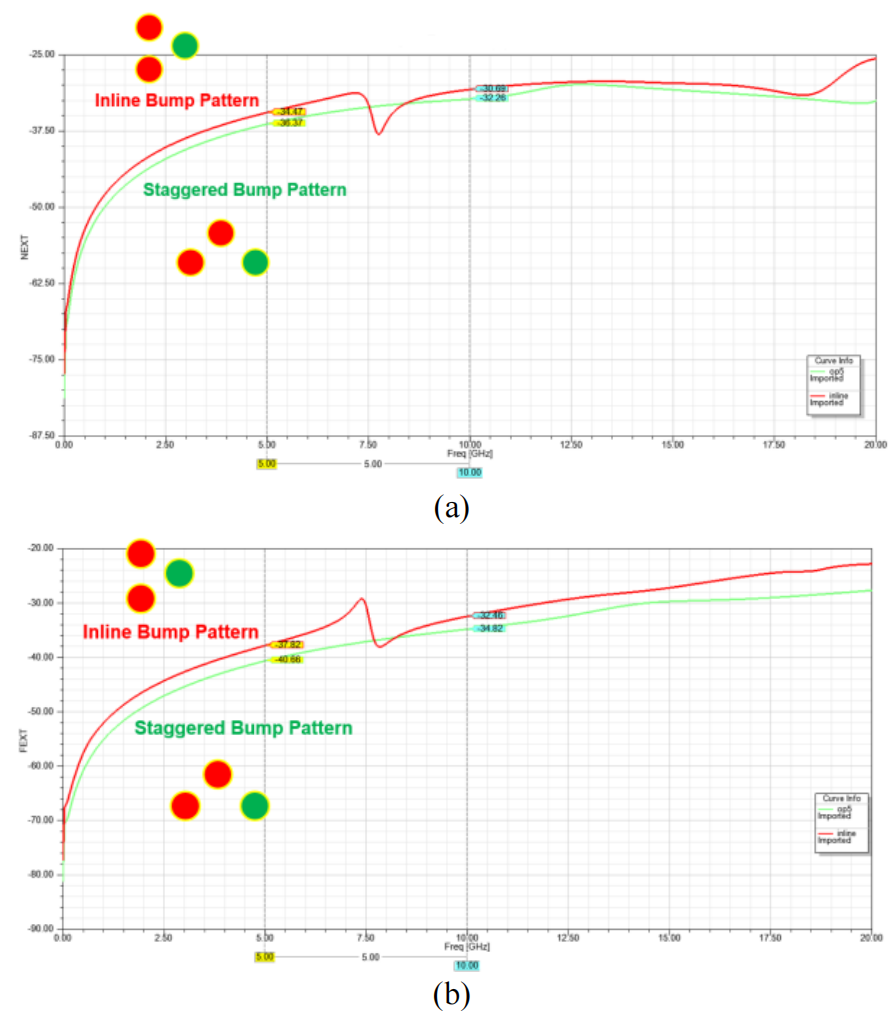

图13(a)和(b)对比了两种bump焊盘图形在不同频率下的NEXT和FEXT特性。交错bump焊盘图形在NEXT和FEXT方面均略优于直列图形。当频率超过7.5GHz时,直列bump焊盘图形的NEXT和FEXT更低,但开始出现谐振现象,随着频率的增加,两种bump焊盘图形的对比变得略微复杂。因此,根据图13中对串扰的总体观察,SWIFT封装的特性可能会因其层叠结构配置而变化,但如果信号被接地防护走线完全包围(无论接地防护走线的宽度和接地过孔如何),则受bump图形组合的影响较小。

图13. 直列和交错bump图形的S参数对比:(a)NEXT、(b)FEXT。

分析讨论

上面分析了多种SWIFT封装布局模型,旨在通过公式(1)对简单串扰进行预估,从而定义最佳无串扰设计。

对重分布层(RDL)走线图案变化进行了仿真。仿真结果表明,采用带接地过孔和防护走线的单条走线时,串扰水平最低,但由于每条信号走线都需要被接地过孔和防护走线包围,因此需要较大的面积。然而,SWIFT封装能够实现最小20um的微过孔,因此设计密度可比常规晶圆级扇出(WLFO)或有机基板高得多。另一种方案是采用带接地防护走线的单条走线,其实现了相近的串扰水平,并且与带接地过孔和防护走线的单条走线相比,能够实现更高密度的走线路由。

薄PI层能够减少微带线中两条信号的耦合,因为信号的边缘场与接地平面的相互作用更强,因此信号下方接地平面的影响变得更为重要。SWIFT封装提供了最薄的介质层、最低的介电常数和损耗角正切,从而减少了串扰问题。

无论接地过孔的数量及其位置如何,接地防护走线的开路短截线都可能导致串扰水平恶化。由于SWIFT封装能够实现最小20um的微过孔以及最小2um的窄走线宽度和间距,因此在开路短截线的末端添加接地过孔(完全或通过最小宽度的局部走线连接至接地焊盘)是可行的。

对与bump焊盘图形相关的串扰进行了研究,如果信号走线分隔良好且被接地防护走线包围,则串扰水平不依赖于bump焊盘图形配置。窄接地走线和间距在该模式下同样有效------其中接地防护走线对串扰水平起主导作用,添加接地过孔可进一步改善性能。

如果组装能力允许减小从重分布层1通过环氧模塑料(EMC)连接至顶部重分布层的模塑过孔间距,从而容纳更多接地模塑过孔,则SWIFT封装的FEXT和NEXT将得到大幅改善。

结论

通过介绍SWIFT封装中的多种走线设计图案,探讨了串扰问题。研究涵盖了bump焊盘图形、带接地防护走线和接地平面的接地过孔以及微带线中介质厚度对串扰的影响。研究发现,与有机基板类似,接地防护走线是降低串扰水平的主导因素。然而,在高密度信号布局方面,由于SWIFT封装提供了极薄的介质层、低介电常数和小型微过孔,因此不带周围接地过孔的接地防护走线也是设计权衡技术中的最佳布局方案。

往期推荐

DDR4 channel Via stubs对FEXT串扰的影响

信号在微带线/带状线中传输时影响串扰的因素分析---上升沿时间、耦合线长度、耦合线间距

以太网信号的电路建模及其在电磁兼容性与信号完整性分析中的应用

128 Gbps PCIe 7.0通道中布线区域和过孔残桩的信号完整性考量

UCIE/HBM高速信号2-μm-Pitch RDL Interposer信号完整性分析

28Gbps及以上速率接口无源互连的损耗机制及支持传输的创新型/高性价比结构