计算机体系结构及其组成

《计算机体系结构及其组成》全文大纲

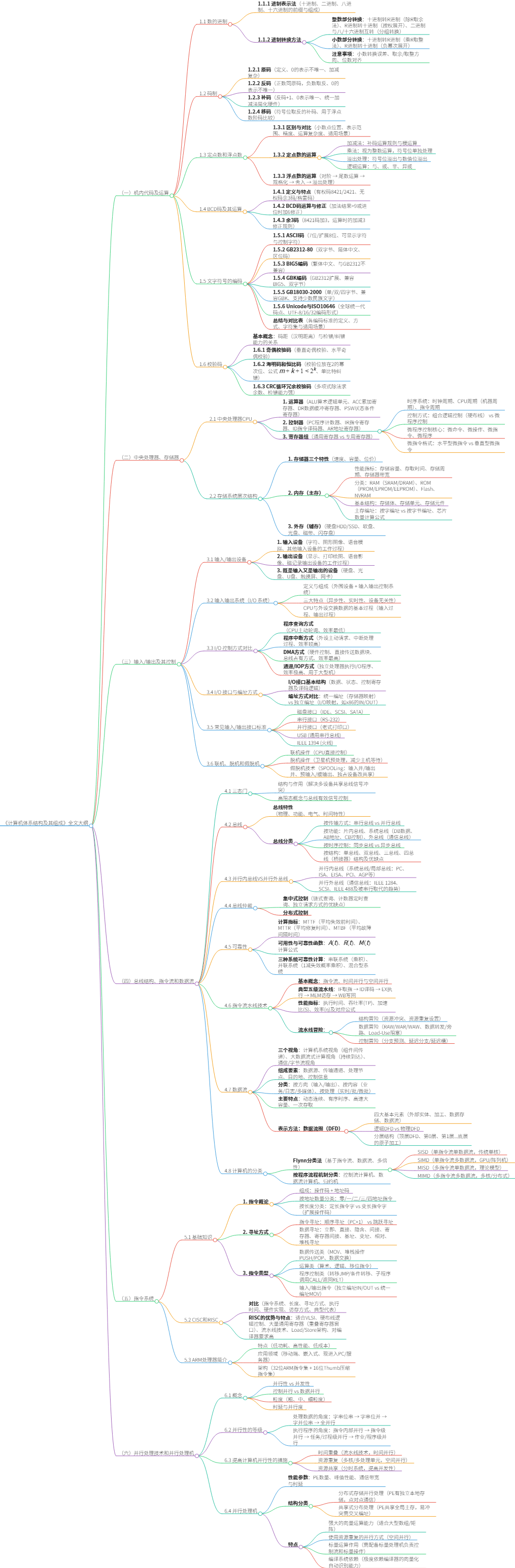

(一)机内代码及运算

1.1 数的进制

1.1.1 进制表示法(十进制、二进制、八进制、十六进制的前缀与组成)

1.1.2 进制转换方法

整数部分转换:十进制转R进制(除R取余法)、R进制转十进制(按权展开)、二进制与八/十六进制互转(分组转换)

小数部分转换:十进制转R进制(乘R取整法)、R进制转十进制(负幂次展开)

注意事项:小数转换误差、取余/取整方向、位数对齐

1.2 码制

1.2.1 原码(定义、0的表示不唯一、加减复杂)

1.2.2 反码(正数同原码,负数取反、0的表示不唯一)

1.2.3 补码(反码+1、0表示唯一、统一加减法简化硬件)

1.2.4 移码(符号位取反的补码、用于浮点数阶码比较)

1.3 定点数和浮点数

1.3.1 区别与对比(小数点位置、表示范围、精度、运算复杂度、适用场景)

1.3.2 定点数的运算

加减法:补码运算规则与模运算

乘法:视为整数运算,符号位单独处理

溢出处理:符号位溢出与数值位溢出

逻辑运算:与、或、非、异或

1.3.3 浮点数的运算(对阶 → 尾数运算 → 规格化 → 舍入 → 溢出处理)

1.4 BCD码及其运算

1.4.1 定义与特点(有权码8421/2421、无权码余3码/格雷码)

1.4.2 BCD码运算与修正(加法结果>9或进位时加6修正)

1.4.3 余3码(8421码加3,运算时的加减3修正规则)

1.5 文字符号的编码

1.5.1 ASCII码(7位/扩展8位、可显示字符与控制字符)

1.5.2 GB2312-80(双字节、简体中文、区位码)

1.5.3 BIG5编码(繁体中文、与GB2312不兼容)

1.5.4 GBK编码(GB2312扩展、兼容BIG5、双字节)

1.5.5 GB18030-2000(单/双/四字节、兼容GBK、支持少数民族文字)

1.5.6 Unicode与ISO10646(全球统一代码点、UTF-8/16/32编码形式)

总结与对比表(各编码标准的定义、方式、字符集与适用场景)

1.6 校验码

基本概念:码距(汉明距离)与检错/纠错能力的关系

1.6.1 奇偶校验码(垂直奇偶校验、水平奇偶校验)

1.6.2 海明码和恒比码(校验位放在2的幂次位、公式 m+k+1<2^k、单比特纠错)

1.6.3 CRC循环冗余校验码(多项式除法求余数、检错能力强)

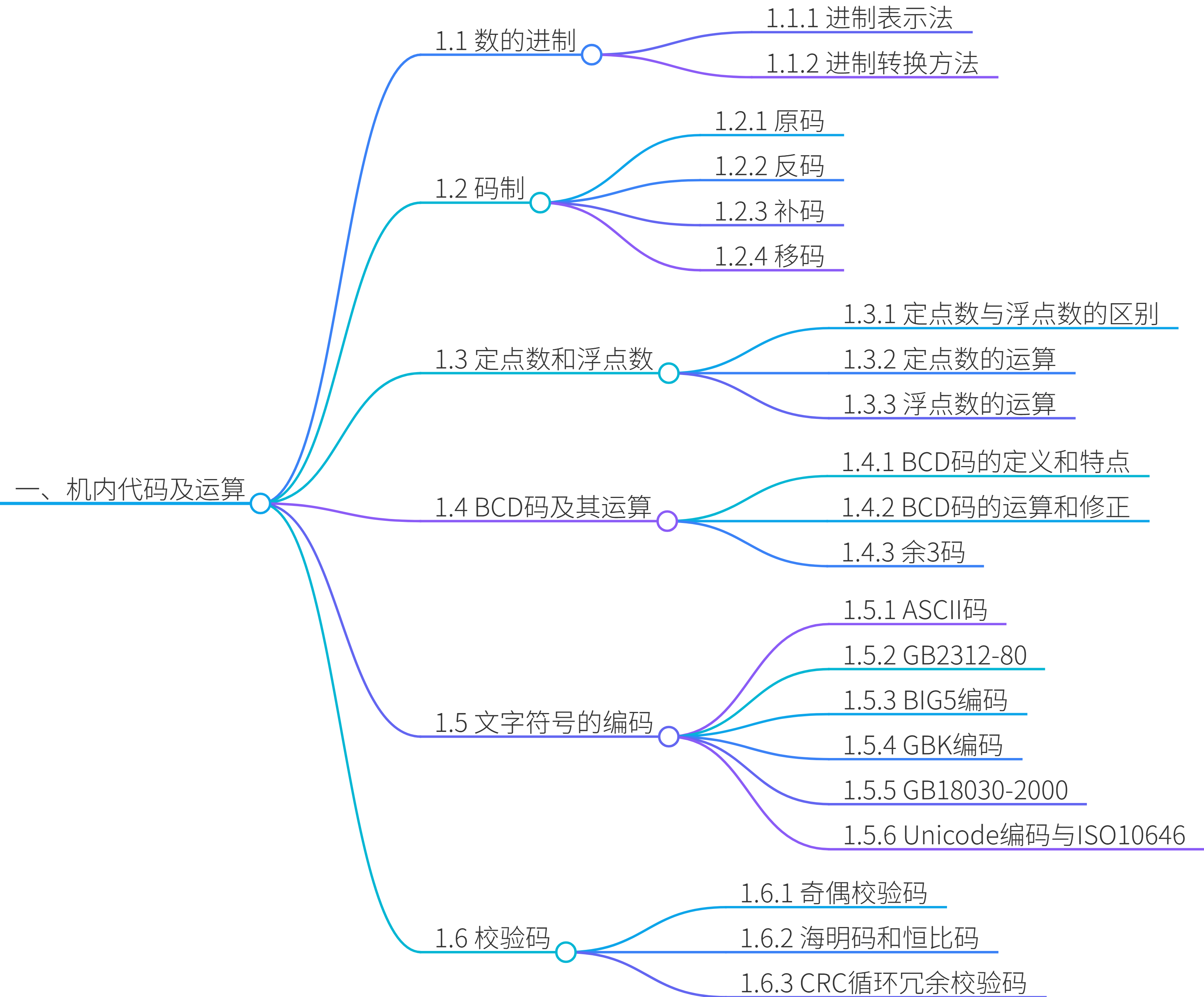

(二)中央处理器、存储器

2.1 中央处理器CPU

-

运算器(ALU算术逻辑单元、ACC累加寄存器、DR数据缓冲寄存器、PSW状态条件寄存器)

-

控制器(PC程序计数器、IR指令寄存器、ID指令译码器、AR地址寄存器)

时序系统:时钟周期、CPU周期(机器周期)、指令周期

控制方式:组合逻辑控制(硬布线) vs 微程序控制

微程序控制核心:微命令、微操作、微指令、微程序

微指令格式:水平型微指令 vs 垂直型微指令

- 寄存器组(通用寄存器 vs 专用寄存器)

2.2 存储系统层次结构

-

存储器三个特性(速度、容量、位价)

-

内存(主存)

性能指标:存储容量、存取时间、存储周期、存储器带宽

分类:RAM(SRAM/DRAM)、ROM(PROM/EPROM/EEPROM)、Flash、NVRAM

基本结构:存储体、存储单元、存储元件

主存编址:按字编址 vs 按字节编址、芯片数量计算公式

- 外存(辅存)(硬盘HDD/SSD、软盘、光盘、磁带、闪存盘)

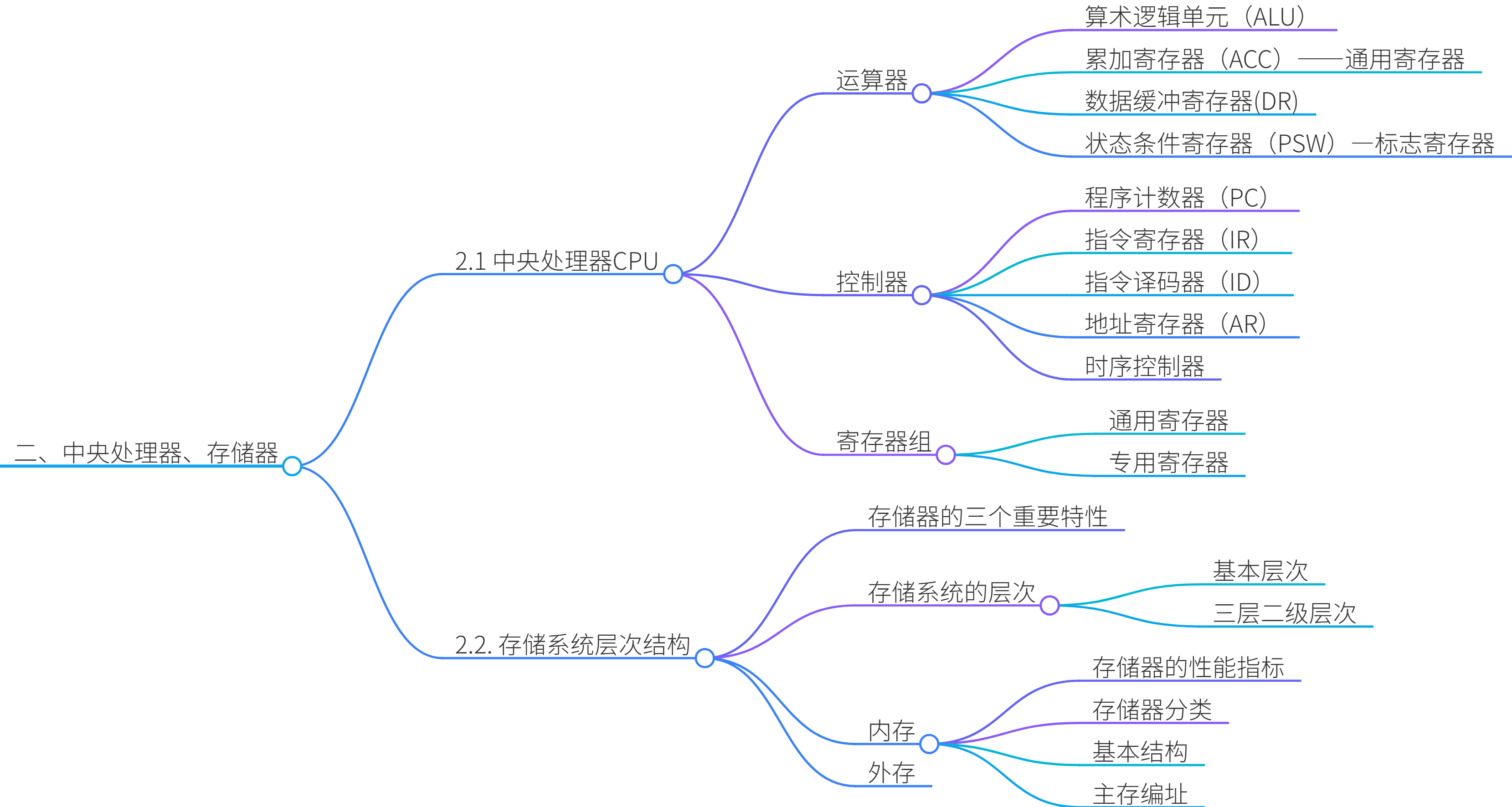

(三)输入/输出及其控制

3.1 输入/输出设备

-

输入设备(字符、图形图像、语音模拟、其他输入设备的工作过程)

-

输出设备(显示、打印绘图、语音影像、磁记录输出设备的工作过程)

-

既是输入又是输出的设备(硬盘、光盘、U盘、触摸屏、网卡)

3.2 输入输出系统(I/O 系统)

定义与组成(外围设备 + 输入输出控制系统)

三大特点(异步性、实时性、设备无关性)

CPU与外设交换数据的基本过程(输入过程、输出过程)

3.3 I/O 控制方式对比

程序查询方式(CPU主动轮询、效率最低)

程序中断方式(外设主动请求、中断处理过程、效率较高)

DMA方式(硬件控制、直接传送数据块、总线占有方式、效率最高)

通道/IOP方式(独立处理器执行I/O程序、效率极高、用于大型机)

3.4 I/O 接口与编址方式

I/O接口基本结构(数据、状态、控制寄存器及译码逻辑)

编址方式对比:统一编址(存储器映射) vs 独立编址(I/O映射,如x86的IN/OUT)

3.5 常见输入/输出接口标准

磁盘接口(IDE、SCSI、SATA)

串行接口(RS-232)

并行接口(老式打印口)

USB (通用串行总线)

IEEE 1394 (火线)

3.6 联机、脱机和假脱机

联机操作(CPU直接控制)

脱机操作(卫星机预处理,减少主机等待)

假脱机技术(SPOOLing:输入井/输出井、预输入/缓输出、独占设备改共享)

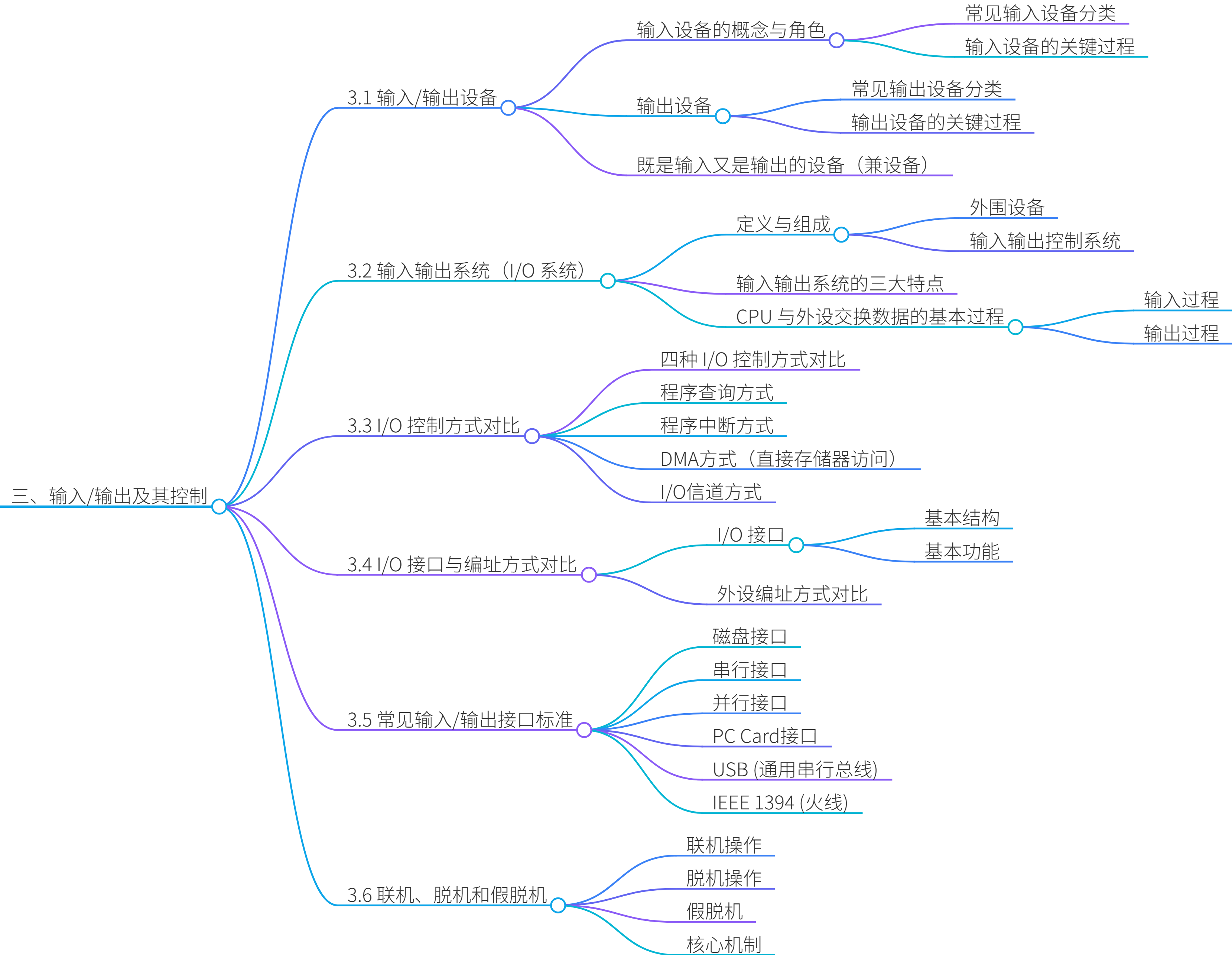

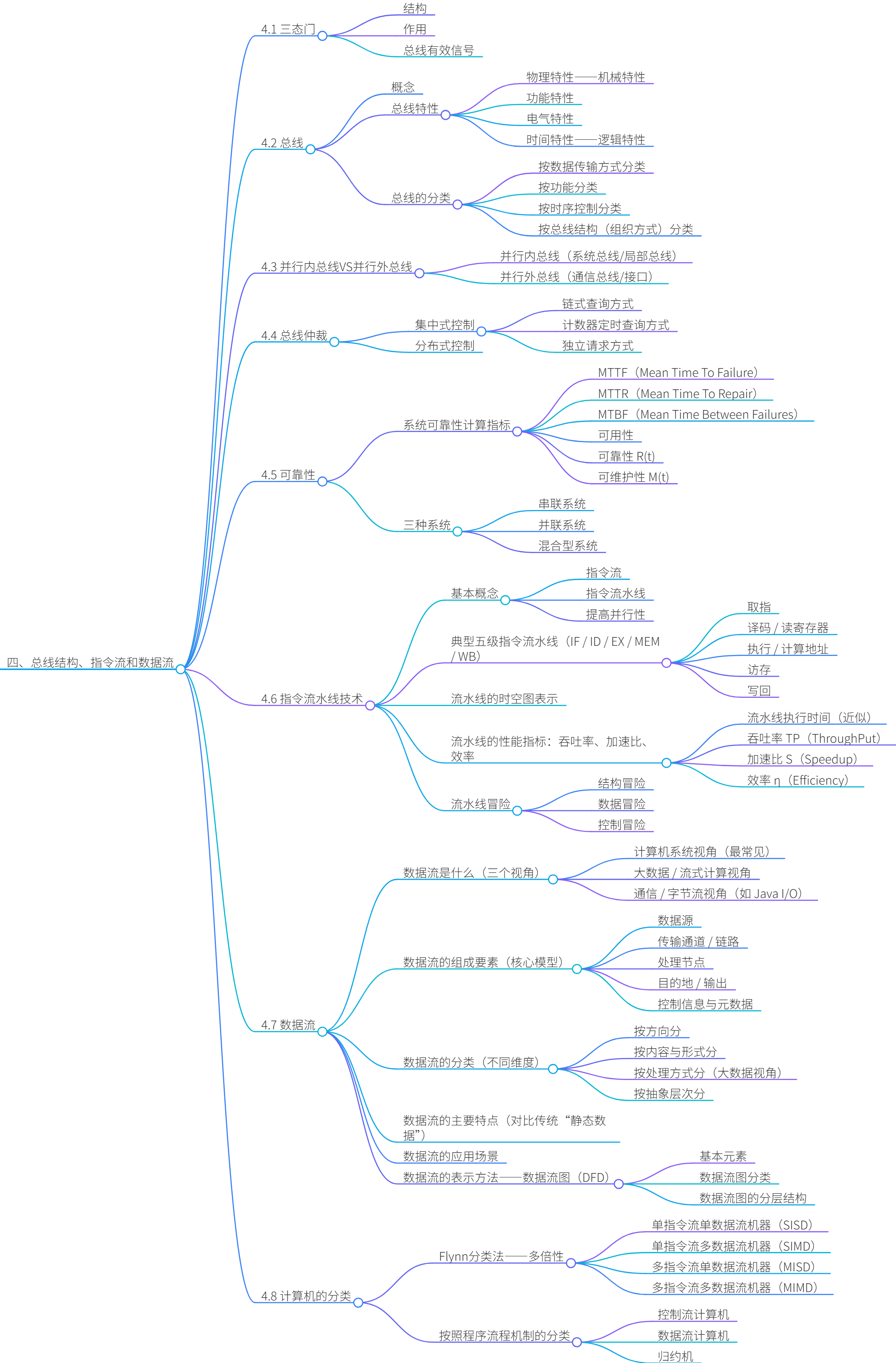

(四)总线结构、指令流和数据流

链接:总线结构、指令流和数据流 - 软考备战(六)-CSDN博客

4.4 总线仲裁

集中式控制(链式查询、计数器定时查询、独立请求方式的优缺点)

分布式控制

4.1 三态门

结构与作用(解决多设备共享总线信号冲突)

高阻态概念与总线有效信号控制

4.2 总线

总线特性(物理、功能、电气、时间特性)

总线分类

按传输方式:串行总线 vs 并行总线

按功能:片内总线、系统总线(DB数据、AB地址、CB控制)、外总线(通信总线)

按时序控制:同步总线 vs 异步总线

按结构:单总线、双总线、三总线、四总线(桥接器)结构及优缺点

4.3 并行内总线VS并行外总线

并行内总线(系统总线/局部总线:PC、ISA、EISA、PCI、AGP等)

并行外总线(通信总线:IEEE 1284、SCSI、IEEE 488及被串行取代的趋势)

4.5 可靠性

计算指标:MTTF(平均失效前时间)、MTTR(平均修复时间)、MTBF(平均故障间隔时间)

可用性与可靠性函数:A(t)、R(t)、M(t) 计算公式

三种系统可靠性计算:串联系统(乘积)、并联系统(1减失效概率乘积)、混合型系统

4.6 指令流水线技术

基本概念:指令流、时间并行与空间并行

典型五级流水线:IF取指 → ID译码 → EX执行 → MEM访存 → WB写回

性能指标:执行时间、吞吐率(TP)、加速比(S)、效率(η)及对应公式

流水线冒险:

结构冒险(资源冲突、资源重复设置)

数据冒险(RAW/WAR/WAW、数据转发/旁路、Load-Use阻塞)

控制冒险(分支预测、延迟分支/延迟槽)

4.7 数据流

三个视角:计算机系统视角(组件间传递)、大数据流式计算视角(持续到达)、通信/字节流视角

组成要素:数据源、传输通道、处理节点、目的地、控制信息

分类:按方向(输入/输出)、按内容(业务/日志/多媒体)、按处理(实时/批/微批)

主要特点:动态连续、有序时序、高速大容量、一次存取

表示方法:数据流图(DFD)

四大基本元素(外部实体、加工、数据存储、数据流)

逻辑DFD vs 物理DFD

分层结构(顶层DFD、第0层、第1层...底层的原子加工)

4.8 计算机的分类

Flynn分类法(基于指令流、数据流、多倍性)

SISD(单指令流单数据流,传统单核)

SIMD(单指令流多数据流,GPU/阵列机)

MISD(多指令流单数据流,理论模型)

MIMD(多指令流多数据流,多核/分布式)

按程序流程机制分类:控制流计算机、数据流计算机、归约机

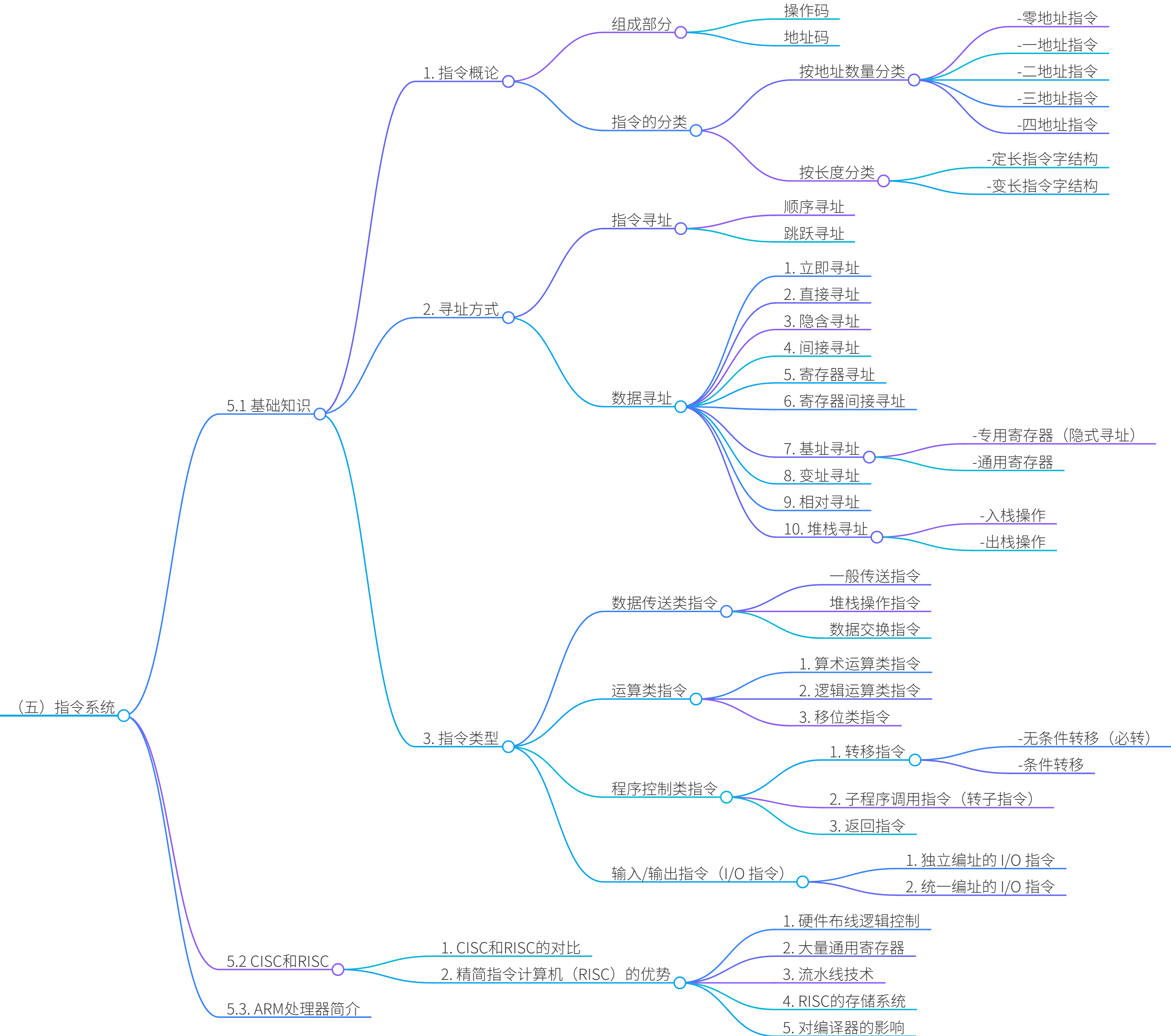

(五)指令系统

5.1 基础知识

- 指令概论

组成:操作码 + 地址码

按地址数量分类:零/一/二/三/四地址指令

按长度分类:定长指令字 vs 变长指令字(扩展操作码)

- 寻址方式

指令寻址:顺序寻址(PC+1) vs 跳跃寻址

数据寻址:立即、直接、隐含、间接、寄存器、寄存器间接、基址、变址、相对、堆栈寻址

- 指令类型

数据传送类(MOV、堆栈操作PUSH/POP、数据交换)

运算类(算术、逻辑、移位指令)

程序控制类(转移JMP/条件转移、子程序调用CALL/返回RET)

输入/输出指令(独立编址IN/OUT vs 统一编址MOV)

5.2 CISC和RISC

对比(指令系统、长度、寻址方式、执行时间、硬件实现、访存方式、典型代表)

RISC的优势与特点:适合VLSI、硬布线逻辑控制、大量通用寄存器(重叠寄存器窗口)、流水线技术、Load/Store架构、对编译器要求高

5.3 ARM处理器简介

特点(低功耗、高性能、低成本)

应用领域(移动端、嵌入式、现进入PC/服务器)

架构(32位ARM指令集 + 16位Thumb压缩指令集)

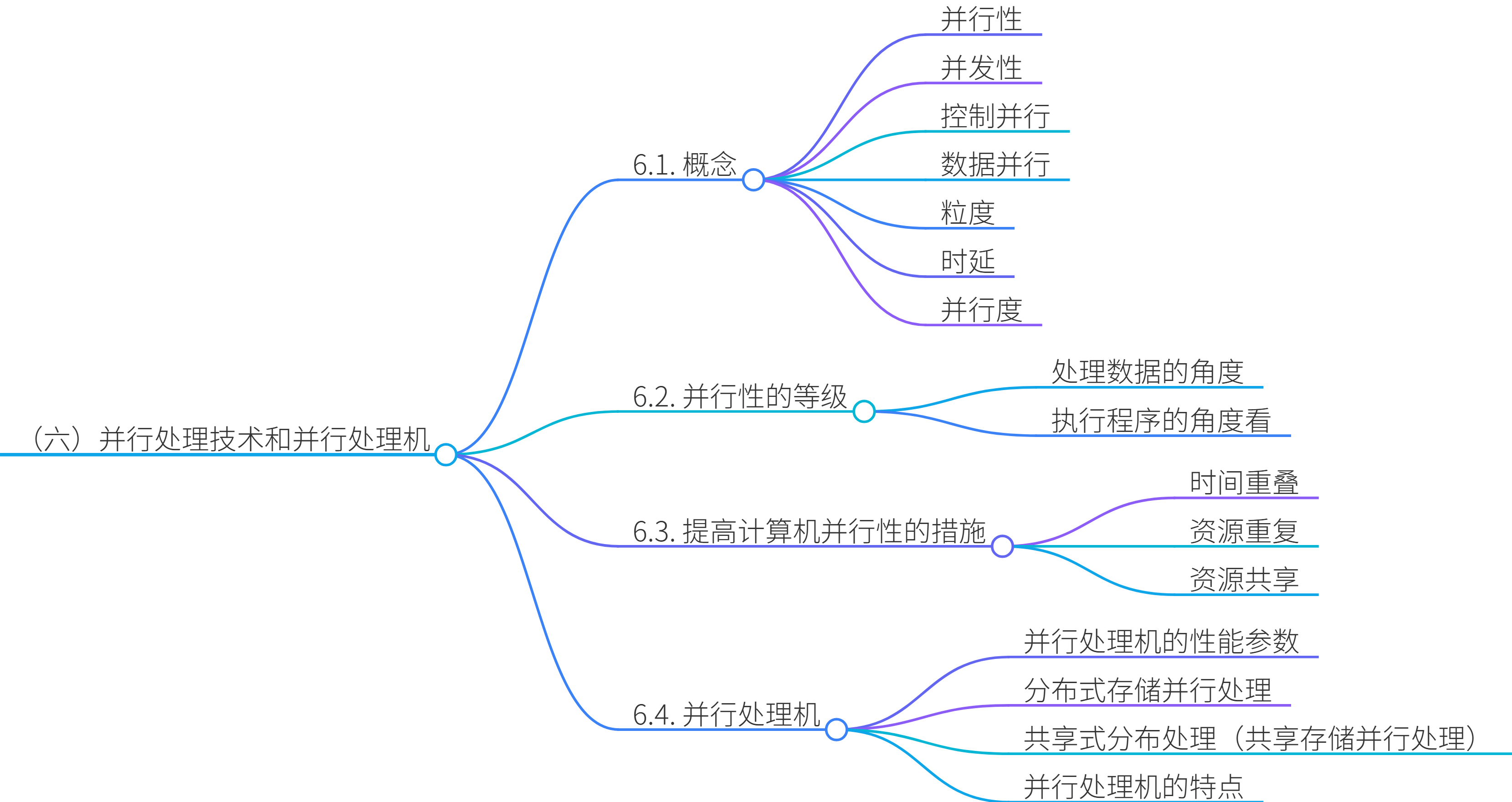

(六)并行处理技术和并行处理机

链接:并行处理技术和并行处理机 - 软考备战(八)_位串字串 位并字串-CSDN博客

6.1 概念

并行性 vs 并发性

控制并行 vs 数据并行

粒度(粗、中、细粒度)

时延与并行度

6.2 并行性的等级

处理数据的角度:字串位串 → 字串位并 → 字并位串 → 全并行

执行程序的角度:指令内部并行 → 指令级并行 → 任务/过程级并行 → 作业/程序级并行

6.3 提高计算机并行性的措施

时间重叠(流水线技术,时间并行)

资源重复(多核/多处理单元,空间并行)

资源共享(分时系统,提高并发性)

6.4 并行处理机

性能参数:PE数量、峰值性能、通信带宽与时延

结构分类

分布式存储并行处理(PE有独立本地存储,点对点通信)

共享式分布处理(PE共享全局主存,易冲突需交叉编址)

特点

强大的向量运算能力(适合大型数组/矩阵)

使用资源重复的并行方式(空间并行)

标量运算作用(需配备标量处理机负责控制流和标量操作)

编译系统依赖(极度依赖编译器的向量化自动识别能力)