一、 前言

高频时钟信号的快速跳变、不完整的回流路径、边缘走线的"天线效应"......这些设计细节稍有不慎,就会让整机变成一台"微型电台",向空间肆意发射电磁波。今天,我们将揭开时钟走线EMC整改的底层逻辑,从辐射机理到实战技巧,手把手教你驯服这些"隐形的干扰源"!

二、 案例分享

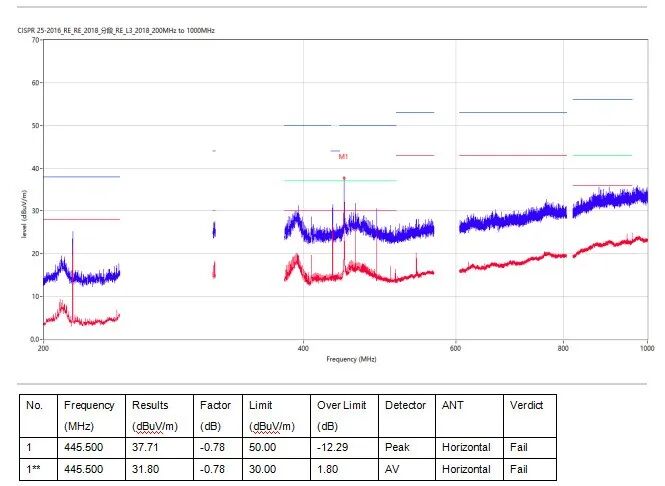

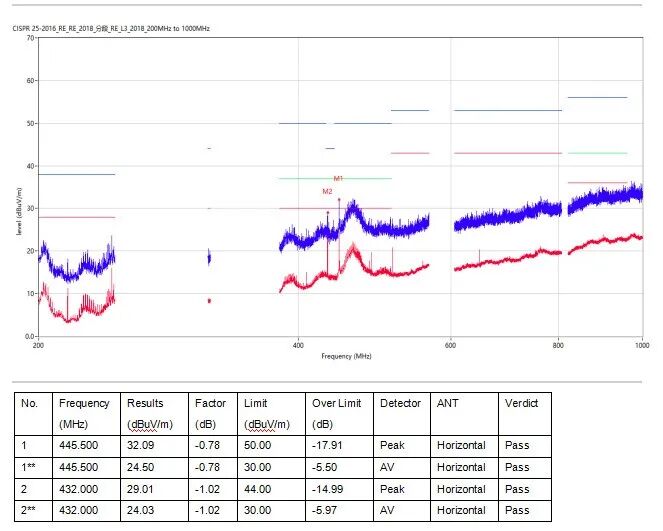

某款行车记录仪的辐射测试结果显示,445.5MHz频点存在超标现象。经分析,该问题源于视频解码芯片TP9950向主控传输的PCLK时钟信号。在整改过程中,尝试采用以下两种措施:

1.将PCLK传输线上的60Ω磁珠替换为120Ω磁珠;

2.在PCLK传输线靠近TP9950芯片端添加滤波电容。

虽然上述措施能够通过辐射测试,但后续发现会引发行车记录仪出现花屏现象。当减小这些器件的参数值时,则出现无法通过辐射测试或显示画面异常的两种情况。

经进一步检查PCB布局,发现TP9950芯片的时钟走线存在以下设计缺陷:

-

走线位于板边区域;

-

未进行包地处理。

针对此问题,我们建议客户对PCLK时钟走线进行优化改进。实施整改后,后续测试结果显示辐射问题已得到有效解决,测试结果符合要求。

【改板建议】:

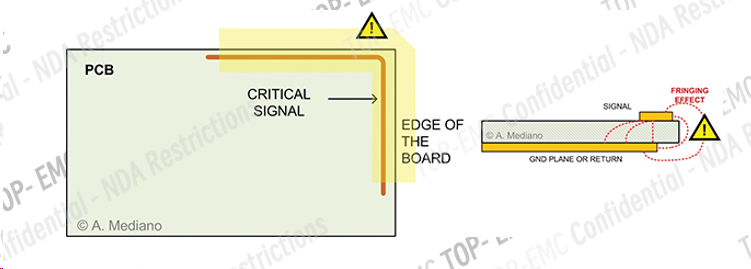

(1)时钟信号不能画在板子边缘,下方或相邻的参考地平面可能被切断或不足,迫使信号回流路径绕行较远距离,就会如下图一样产生一些空间串扰。

时钟信号距离板边的距离最好大于5mm,在时钟信号到板边之间最好多一个地走线进行隔离,如下图所示。

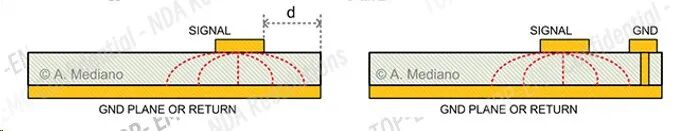

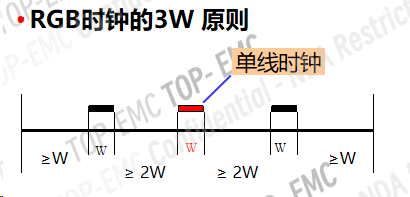

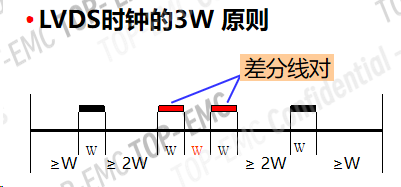

(2)画PCB板的时候我们一般会有3W原则,也就是在PCB设计中,为了减少线间串扰,应保证线间距足够大,当线中心间距不少于3倍线宽时。

例如,若线宽为5mil(0.127mm),则相邻信号线的最小间距应为15mil(0.381mm),耦合到临近走线的边缘场很少,大部分的电磁场被包围在走线和回流平面之间,可以降低70%信号线间电场和磁场的耦合效应。如果能满足10倍线宽则能减少98%信号间的串扰。单线时钟和差分时钟会有一点点区别,可以参考下图所示。

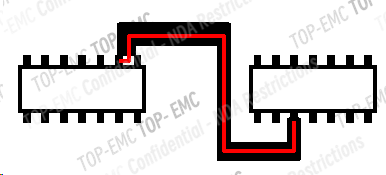

(3)在时钟线的下层,沿着信号线布一条地线,地线尽量宽一些。这样形成的回路面积等于线路板的层间厚度乘以信号线的长度,如下图所示。

三、 总结

一般情况下,时钟信号都是比较敏感的,像滤除高频噪声的电容或者共模电感,都会干扰信号的完整性,所以当我们遇到时钟噪声超标时,我们可以先看看时钟走线是否有问题,比如走线过长;走线太过靠近主板边缘;走线是否进行包地处理。因为时钟信号回流需要低阻抗路径,所以对时钟走线的整改也是辐射超标问题的重要解决手段。