在系统架构设计师考试中,计算机系统基础 是非常重要的一部分。其中,计算机体系结构是理解计算机运行机制的核心基础,也是后续学习操作系统、系统性能优化、分布式系统架构等知识的重要前提。

本文将系统讲解计算机体系结构中的核心内容,包括:

-

运算器

-

控制器

-

冯诺依曼结构

-

哈佛结构

并通过必要的结构图帮助读者理解计算机内部的工作机制。

一、计算机体系结构概述

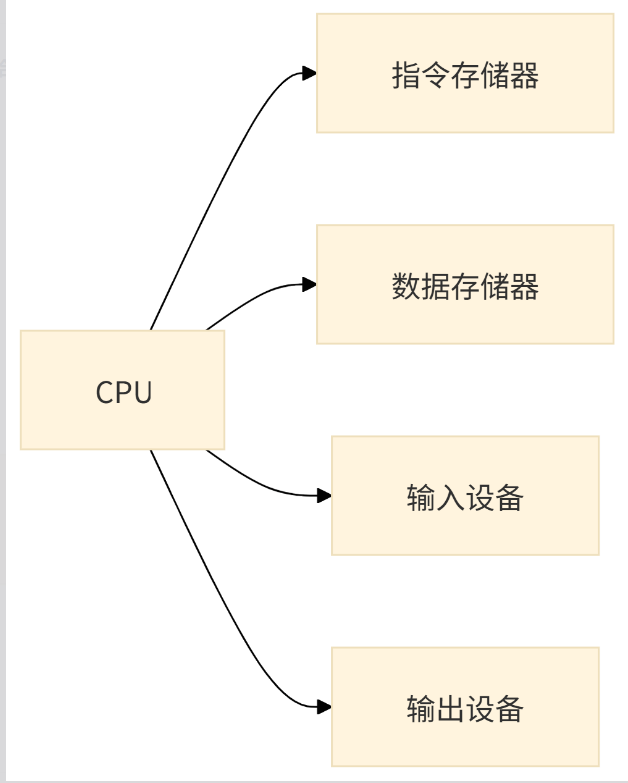

计算机体系结构主要研究计算机系统的组成结构以及各个部件之间的工作方式。从整体上看,一台计算机主要由以下几个部分组成:

-

运算器

-

控制器

-

存储器

-

输入设备

-

输出设备

其中:

-

运算器和控制器共同组成CPU

-

CPU是计算机系统的核心

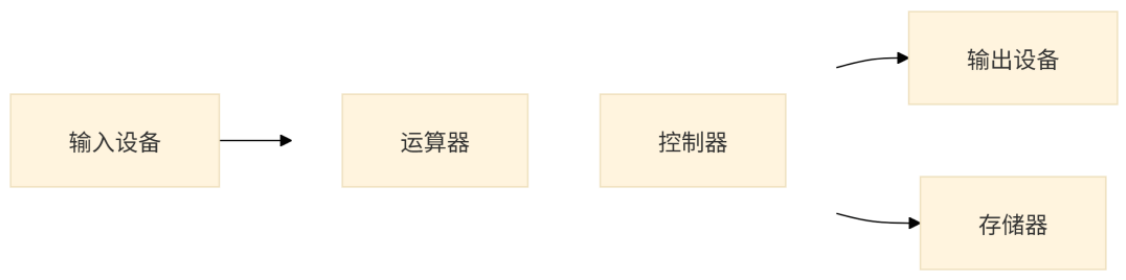

计算机系统的基本结构可以表示为:

计算机的基本工作过程为:

-

从输入设备获取数据

-

将程序和数据存储到存储器

-

CPU执行程序进行计算处理

-

将结果通过输出设备输出

二、运算器

运算器是计算机中负责数据运算处理的核心部件,其主要任务是完成各种算术运算和逻辑运算。

例如:

-

加法运算

-

减法运算

-

逻辑与

-

逻辑或

-

数据比较

运算器主要由以下几个部件组成:

-

算术逻辑单元 ALU

-

累加寄存器 AC

-

数据缓冲寄存器 DR

-

状态条件寄存器 PSW

2.1 算术逻辑单元 ALU

算术逻辑单元(Arithmetic Logic Unit,ALU)是运算器中最核心的部件。

它主要负责:

-

算术运算

-

逻辑运算

例如:

-

加法运算

-

减法运算

-

乘法运算

-

除法运算

-

逻辑与

-

逻辑或

-

比较运算

ALU根据控制器发出的控制信号执行不同类型的运算。

2.2 累加寄存器 AC

累加寄存器(Accumulator,AC)是一种通用寄存器,主要用于为ALU提供工作区。

主要作用:

-

暂存运算数据

-

存储中间结果

-

存储运算结果

例如:

在执行加法运算时:

AC = AC + 数据因此累加寄存器在运算过程中起到了非常重要的作用。

2.3 数据缓冲寄存器 DR

数据缓冲寄存器(Data Register,DR)主要用于在CPU和内存之间进行数据传输时暂存数据。

典型使用场景包括:

-

从内存读取数据

-

向内存写入数据

-

暂存指令或操作数

DR的存在可以减少CPU直接访问内存的次数,提高数据传输效率。

2.4 状态条件寄存器 PSW

状态条件寄存器(Program Status Word,PSW)用于存储程序运行过程中的各种状态信息。

常见状态标志包括:

-

零标志(Zero Flag)

-

进位标志(Carry Flag)

-

符号标志(Sign Flag)

-

溢出标志(Overflow Flag)

例如:

如果运算结果为0,则零标志会被设置。

PSW中的这些标志通常用于:

-

条件判断

-

程序跳转

-

中断处理

有些体系结构中,PSW也被归类为控制器的一部分。

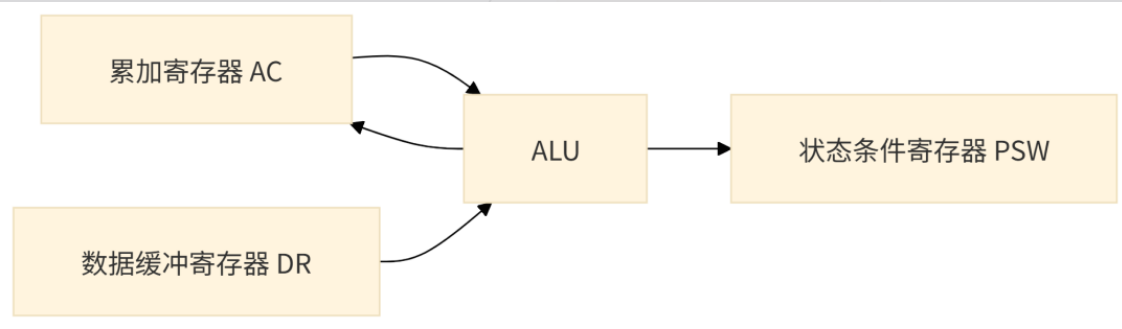

运算器结构图

运算器内部结构可以表示为:

在执行运算时:

-

数据进入ALU

-

ALU执行运算

-

运算结果写回寄存器

-

同时更新状态寄存器

三、控制器

控制器是CPU的指挥中心,负责控制整个计算机系统的运行。

控制器的主要功能包括:

-

取指令

-

分析指令

-

发出控制信号

-

协调各部件工作

控制器主要由以下几个核心部件组成:

-

程序计数器 PC

-

指令寄存器 IR

-

指令译码器 ID

-

时序控制部件

3.1 程序计数器 PC

程序计数器(Program Counter,PC)用于存储下一条即将执行的指令地址。

当一条指令执行完成后:

PC会自动更新,指向下一条指令。

例如:

PC = PC + 1如果程序执行跳转指令,则PC会被修改为新的地址。

因此PC决定了程序的执行顺序。

3.2 指令寄存器 IR

指令寄存器(Instruction Register,IR)用于存储当前正在执行的指令。

CPU从内存中取出指令后,会先将指令放入IR中,然后再进行解析和执行。

IR的主要作用:

-

保存当前指令

-

为译码器提供指令内容

3.3 指令译码器 ID

指令译码器(Instruction Decoder,ID)负责对指令中的操作码进行解析。

例如一条机器指令可能表示:

-

加法运算

-

数据传输

-

条件跳转

译码器会解析操作码,并生成对应的控制信号。

3.4 时序控制部件

计算机系统是按照时钟周期运行的。

时序控制部件负责:

-

生成时钟信号

-

控制操作执行顺序

-

保证系统同步运行

例如:

取指令 译码 执行

这些操作都需要严格的时间控制。

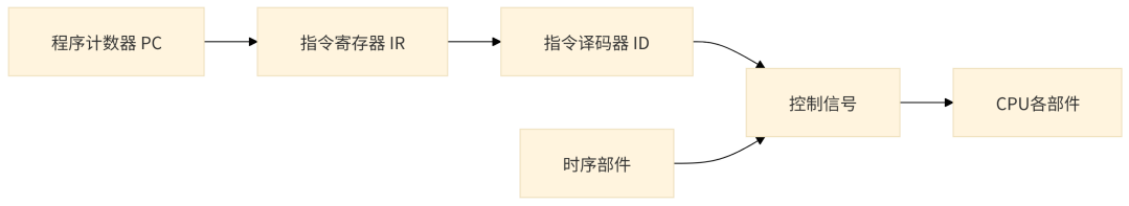

控制器结构图

控制器通过控制信号协调CPU各个部件完成指令执行。

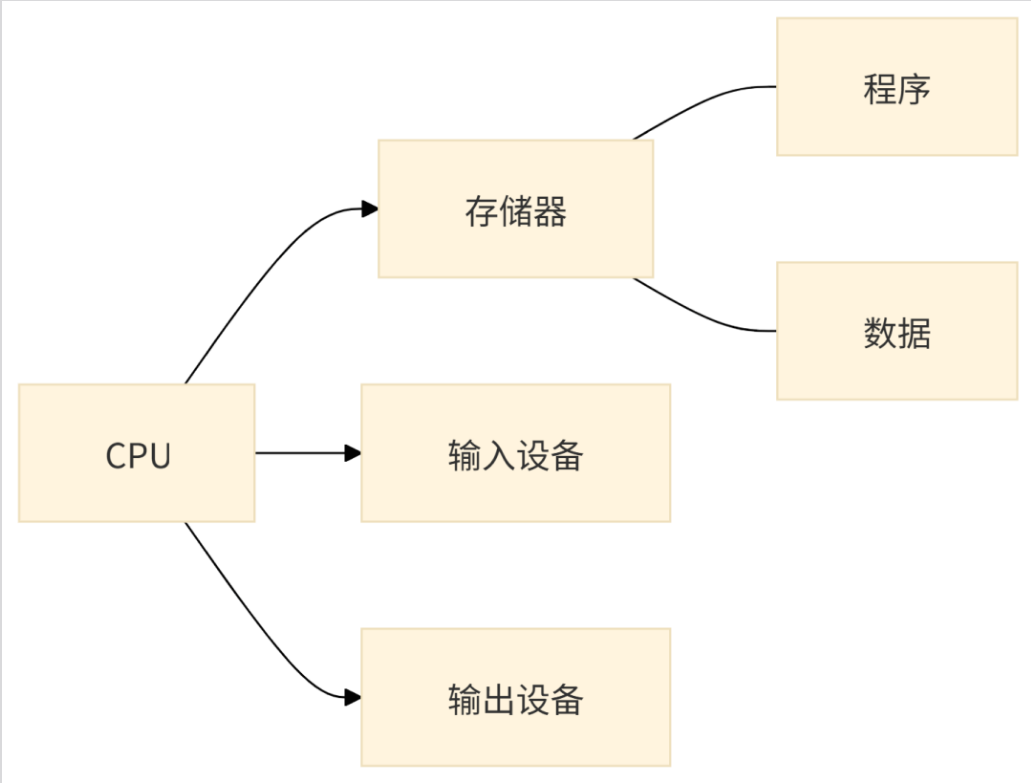

四、冯诺依曼结构

冯诺依曼结构也称为普林斯顿结构,是现代计算机最经典的一种体系结构。

其核心思想是:

程序和数据存储在同一存储器中。

冯诺依曼结构的主要特点:

-

指令与数据存储在同一个存储器中

-

指令和数据共用同一总线

-

采用顺序执行方式

这种结构广泛应用于个人计算机,例如:

-

Intel i3

-

Intel i5

-

Intel i7

冯诺依曼结构示意图:

这种结构设计简单,但存在一个经典问题:

冯诺依曼瓶颈

因为指令和数据共用一条总线,当同时访问时会产生冲突,从而影响性能。

五、哈佛结构

哈佛结构是一种将程序存储和数据存储完全分开的计算机体系结构。

与冯诺依曼结构不同,哈佛结构采用两套独立的存储空间。

主要特点:

-

程序存储器和数据存储器分离

-

可以同时读取指令和数据

-

数据吞吐率更高

哈佛结构通常用于:

-

嵌入式系统

-

DSP数字信号处理器

哈佛结构示意图

在硬件设计上,哈佛结构通常具有四条总线:

-

指令地址总线

-

指令数据总线

-

数据地址总线

-

数据数据总线

这种结构可以实现指令读取和数据访问并行执行,从而提高系统性能。

六、冯诺依曼结构与哈佛结构对比

| 对比内容 | 冯诺依曼结构 | 哈佛结构 |

|---|---|---|

| 存储方式 | 指令与数据共用存储器 | 指令与数据分开存储 |

| 总线 | 一套总线 | 两套总线 |

| 数据访问 | 顺序访问 | 并行访问 |

| 性能 | 较低 | 较高 |

| 应用场景 | PC计算机 | 嵌入式系统 |

现代CPU通常采用改进型哈佛结构,例如:

-

指令缓存(Instruction Cache)

-

数据缓存(Data Cache)

这样既保留了冯诺依曼结构的统一存储特性,又提高了系统性能。

七、总结

计算机体系结构是理解计算机系统工作原理的重要基础,其核心内容包括:

-

运算器负责数据运算

-

控制器负责指挥系统运行

-

冯诺依曼结构将程序与数据存储在同一存储器

-

哈佛结构将程序与数据存储分离

在系统架构设计师考试中,这部分知识不仅会出现在选择题中,也可能作为案例分析的基础知识。

理解计算机体系结构,有助于更深入理解后续内容,例如:

-

操作系统原理

-

存储体系结构

-

系统性能优化

-

分布式系统架构设计