|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

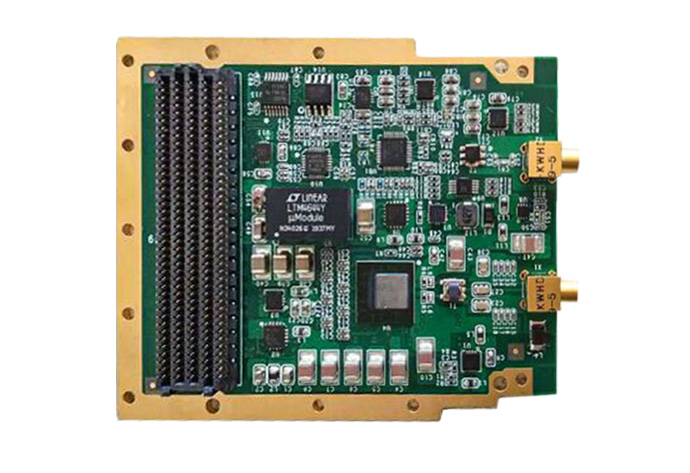

| 基于AD916X的直流至 12 GHz 矢量信号发生器 FMC子卡 |

| |-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------| |  一、DAC 性能指标: ● DAC 型号:AD9163。 ● 分辨率:16bits。 ● DAC 更新速率:12GSPS。 ● 6GSPS 直接 RF 频率合成。 ● 直流至 3GHz(不归零 NRZ 模式)。 ● 直流至 6GHz(2 倍 NRZ 模式)。 ● 1.5GHz 至 7.5GHz(混合模式)。 ● 可选插值 6X、8X、12X、16X、24X。 ● 数据传输:8 个 LANE JESD204B。 二、 时钟性能指标: ● DLCK 时钟由 ADF4355 产生。 ● 时钟芯片型号:AD9508 ● 支持板载时钟/外部时钟,可跳线选择 三、 其他: ● 连接器: MCX。 ● 标准 FMC 子卡,符合 VITA57.1 规范。 ● 典型功耗:5W。 ● 板卡尺寸:84.1mm X 69mm。 ● 工作温度:-40℃~+85℃。 | |

一、DAC 性能指标: ● DAC 型号:AD9163。 ● 分辨率:16bits。 ● DAC 更新速率:12GSPS。 ● 6GSPS 直接 RF 频率合成。 ● 直流至 3GHz(不归零 NRZ 模式)。 ● 直流至 6GHz(2 倍 NRZ 模式)。 ● 1.5GHz 至 7.5GHz(混合模式)。 ● 可选插值 6X、8X、12X、16X、24X。 ● 数据传输:8 个 LANE JESD204B。 二、 时钟性能指标: ● DLCK 时钟由 ADF4355 产生。 ● 时钟芯片型号:AD9508 ● 支持板载时钟/外部时钟,可跳线选择 三、 其他: ● 连接器: MCX。 ● 标准 FMC 子卡,符合 VITA57.1 规范。 ● 典型功耗:5W。 ● 板卡尺寸:84.1mm X 69mm。 ● 工作温度:-40℃~+85℃。 | |

太速科技-基于AD916X的直流至 12 GHz 矢量信号发生器 FMC子卡

北京太速科技股份有限公司2024-06-21 15:19

相关推荐

xyx-3v3 小时前

ZYNQ 简介xyx-3v3 小时前

Zynq-7000xyx-3v8 小时前

zynq7010和zynq7020的区别xyx-3v10 小时前

LUT(Look-Up Table,查找表)的定义与核心概念明德扬1 天前

K7+AD9144 多模式实测|8 种 JESD204B 配置全覆盖验证xyx-3v1 天前

SOC相对于版上系统的优势是什么?Aaron15882 天前

RFSOC+VU13P+GPU 在6G互联网中的技术应用stars-he2 天前

基于 Design Compiler 的 UDP Payload 追加控制模块综合与门级后仿真尤老师FPGA3 天前

HDMI数据的接收发送实验(十)逻辑诗篇3 天前

破核拆解:PCIE719——基于Xilinx Zynq UltraScale+的高性能SAS扩展卡设计