实验名称:

用V e r i l o g实现一个简单ALU。(组合逻辑)

实验目的:

学生通过用V e r i log实现简单的ALU,熟悉硬件描述语言Verilog的基本语法和ALU相关概念,为用Verilog实现CPU和计算机组成的学习打下基础。

实验描述:

输入:两个4位二进制数,代表两个操作数A,B;一个3位控制信号operation,代表ALU要进行的运算。本实验中,ALU可以实现4种运算:

输出:4位结果,1位进位

实验分析:

实现四种运算,与、或、异或、同或。

a&b a|b a^b ~(a^b)

代码如下:

`timescale 1ns / 1ps

module new(

a,

b,

c,

d,

y

);

input a;

input b;

input c;

input d;

output y;

reg y;

always@(a or b or c or d)begin

if(c==0)begin

if(d==0)begin

y<=a&b;

end

else begin

y<=a^b;

end

end

else begin

if(d==0)begin

y<=~(a^b);

end

else begin

y<=a|b;

end

end

end

endmoduletestbench代码进行仿真测试:

`timescale 1ns / 1ps

module test();

reg a,b,c,d;

wire y;

new tsh(

.a(a),

.b(b),

.c(c),

.d(d),

.y(y)

);

initial begin

a=0;b=0;c=0;d=0;

# 20;

a=0;b=0;c=0;d=1;

# 20;

a=0;b=0;c=1;d=0;

# 20;

a=0;b=0;c=1;d=1;

# 20;

a=0;b=1;c=0;d=0;

# 20;

a=0;b=1;c=0;d=1;

# 20;

a=0;b=1;c=1;d=0;

# 20;

a=0;b=1;c=1;d=1;

# 20;

a=1;b=0;c=0;d=0;

# 20;

a=1;b=0;c=0;d=1;

# 20;

a=1;b=0;c=1;d=0;

# 20;

a=1;b=0;c=1;d=1;

# 20;

a=1;b=1;c=0;d=0;

# 20;

a=1;b=1;c=0;d=1;

# 20;

a=1;b=1;c=1;d=0;

# 20;

a=1;b=1;c=1;d=1;

# 20;

$finish;

end

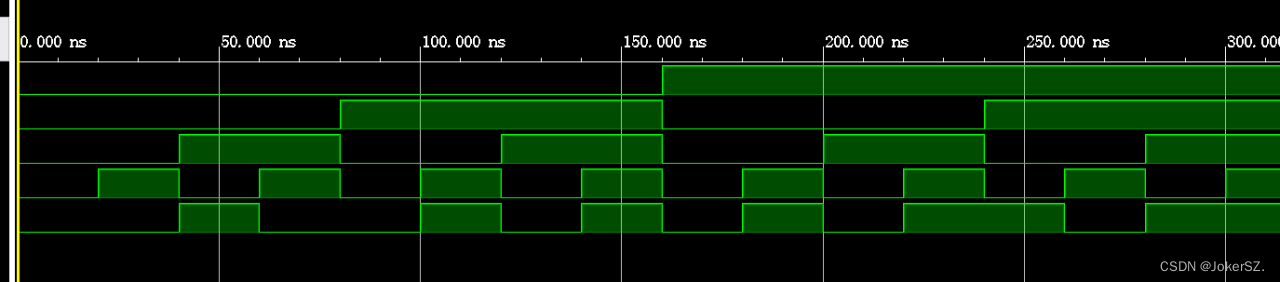

endmodule运行结果: