1.JTAG的作用

JTAG (Joint Test Action Group) 是 FPGA 开发中最重要的接口,没有之一。它的主要作用有两个:

-

下载/配置 (Configuration): 把你写好的代码(.bit 文件)烧录到 FPGA 里面去。

-

在线调试 (Debugging): 使用 Vivado 的 ILA (Logic Analyzer) 在电脑上实时抓取 FPGA 内部的波形。

2.实例

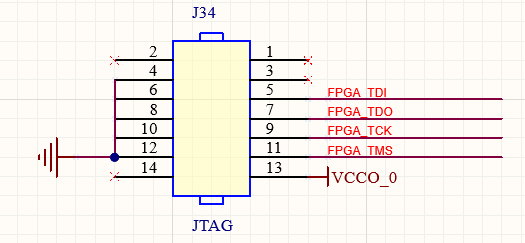

简单设计------14-pin:

这张图是 FPGA 的 JTAG 接口电路设计。以下是这个设计的详细解读:

2.1. 四大核心信号 (The Big 4)

图中的 J34 连接了 JTAG 的四个标准信号,它们构成了通信的基础:

-

TCK (Test Clock) - Pin 9:

-

时钟线。JTAG 是同步通信,所有数据的传输都跟着这个时钟的节拍走。

-

注意: TCK 信号对信号质量要求很高,如果板子上走线很长,通常建议串联一个几十欧姆(如 33Ω)的电阻来防止反射。

-

-

TMS (Test Mode Select) - Pin 11:

- 模式选择。它控制 JTAG 内部的一个"状态机"。简单说,它告诉 FPGA:"我现在是准备传指令呢,还是准备传数据呢?"

-

TDI (Test Data In) - Pin 5:

- 数据输入。电脑发出的数据(比如代码)通过这根线进入 FPGA。

-

TDO (Test Data Out) - Pin 7:

- 数据输出。FPGA 返回的数据(比如调试时的波形数据,或者读取芯片 ID)通过这根线传回电脑。

2.2. 电源 VCCO_0 (Pin 13) 的作用

你会发现 Pin 13 接了 VCCO_0(也就是 FPGA Bank 0 的供电电压,通常是 3.3V)。

-

目的: 这不是给下载器供电,而是提供 参考电压 (Reference Voltage, Vref)。

-

原理: 下载器(如 Platform Cable USB)需要知道 FPGA 的电平标准是多少(是 3.3V, 2.5V 还是 1.8V?),然后它会自动调整自己输出信号的电压,确保不会烧坏 FPGA 引脚。

2.3. 接地设计的玄机 (GNDs)

图中 Pin 2, 4, 6, 8, 10, 12, 14 全部连接到了地 (GND)。这种设计叫 "信号-地-信号" (Signal-Ground-Signal) 布局。

-

抗干扰: 在排线中,每一根信号线旁边都夹着一根地线。地线像"护盾"一样,吸收信号线之间的电磁干扰(串扰 Crosstalk)。

-

高速稳定性: 保证 TCK 这种高速时钟信号在传输时有良好的回流路径,防止下载失败。

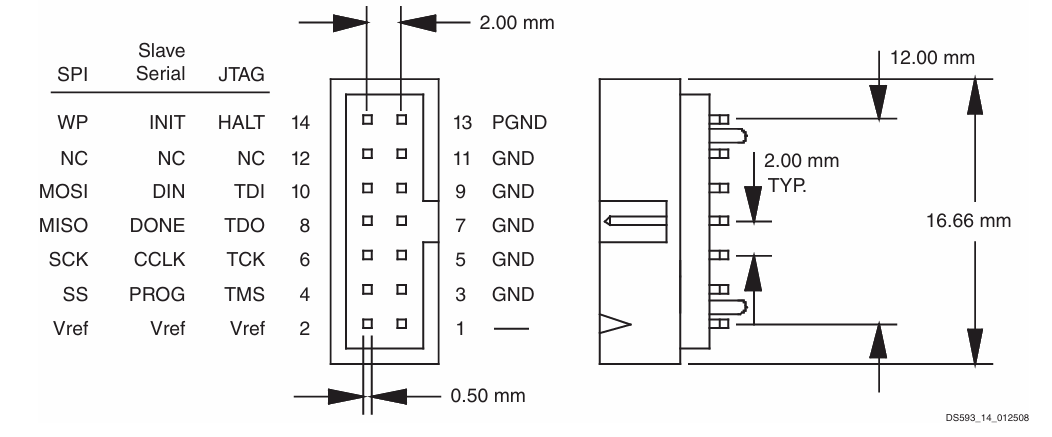

⚠️ 重要提示:线序匹配

这张图的线序(Pinout)看起来比较特殊。

标准的 Xilinx 14-pin 2.0mm 接口定义(参考 Platform Cable USB II Data Sheet (DS593) • 查看器 • AMD 技术信息门户网站)通常是:

-

Pin 2 = Vref

-

Pin 4 = TMS

-

Pin 6 = TCK

-

...

而你这张图中:

-

Pin 13 = Vref

-

Pin 11 = TMS

-

Pin 9 = TCK

所以看起来不一样,但实际上是一样的,只是引脚的命名不太一样。但感觉还是按官方的设计会好一些。

总结

这是一个标准的 JTAG 物理连接设计,采用了多地线隔离的方式来增强信号稳定性。

下一步建议: 在画 PCB 时,这四根线(TCK, TMS, TDI, TDO)尽量走短一点,并且在 TCK 线上预留一个串联电阻的位置(哪怕贴 0Ω),以防万一信号不好时可以调整。

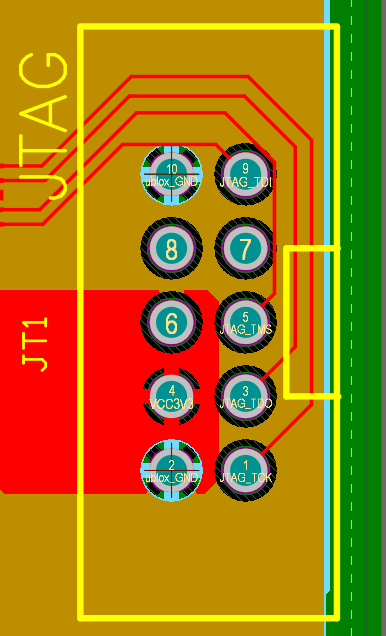

实例二------10-pin:

如果使用的是 Xilinx FPGA(如 Spartan-6, 7-Series, Zynq 等),官方工具链(Vivado/ISE Hardware Manager)和下载器(Platform Cable USB II, SmartLynq)默认不支持 10-pin。10-pin常用于嵌入式的设备。如果在 Xilinx FPGA 上使用 10-pin 接口,需要:

- 使用转接头: 购买 "Xilinx 14-pin to ARM 10-pin adapter",这一般的下载器上会有这个接口。如下图所示:

- 自定义线序: 如果您自己做转接线,必须确保 VCC (Pin 1) 和 GND 的位置与标准一致,否则极易烧毁调试器。

这张图中多加的 U31 (RCLAMP0524P) 是为了 ESD 静电保护。

这是一个非常专业且必要的"保险设计"。JTAG 接口通常暴露在电路板边缘,工程师经常需要用手插拔下载器,极易引入静电。以下是为什么要加这个芯片的 3 个核心原因:

2.1. 核心作用:充当"防静电盾牌" (ESD Protection)

-

危险源: JTAG 接口(JT1)是直接对外的连接器。人体带有几千伏的静电,当你用手拿着 JTAG 下载线插向接口的那一瞬间,高压静电很容易通过

TCK,TMS等引脚直接打入 FPGA。 -

脆弱的 FPGA: FPGA 的 IO 引脚非常脆弱,内部的栅极氧化层很薄,扛不住这种瞬间高压。如果没有保护,FPGA 可能会瞬间报废(击穿)。

-

U31 的工作原理: RCLAMP0524P 是一种 TVS 二极管阵列。

-

它安装在"连接器"和"FPGA"之间。

-

当正常的 3.3V 信号通过时,它假装自己不存在(高阻态)。

-

当几千伏的静电尖峰打进来时,它会在纳秒级的时间内导通,把高压直接泄放到地 (GND),从而确保传到后面 FPGA 的电压被限制在安全范围内(比如 5V 以内)。

-

2.2. 为什么选 "RCLAMP0524P" 这种型号?(关键在于"低电容")

你可能会问:"为什么不随便并联几个普通稳压二极管?"

这就涉及到了 信号完整性。

-

JTAG 也是高速信号:

TCK(时钟线) 的频率通常在 6MHz 到 30MHz 甚至更高,边缘很陡峭。 -

普通二极管的问题: 普通的 TVS 管或稳压管,寄生电容很大(几十 pF)。如果接在 TCK 线上,会把方波信号的棱角磨平(由于 RC 滤波效应),导致下载失败或不稳定。

-

RCLAMP0524P 的特技:

-

超低电容: 它的电容通常只有 0.3pF ~ 0.8pF。

-

效果: 它可以"隐身"。加了它之后,几乎不会影响 JTAG 信号的传输速度和波形质量。它是专门为 HDMI、USB、JTAG 这类高速接口设计的。

-

2.3. "Flow-Through" 走线设计

注意看原理图中的 U31 引脚分布:

-

左边是

1, 2, 4, 5,右边是10, 9, 7, 6。 -

这种封装设计允许你在画 PCB 时,让 JTAG 信号线直接从芯片下方**"穿过" (Flow-through)**。信号从左边进,右边出,直接通向排针。

-

好处: 这样走线最顺畅,不会产生多余的线头(Stub),进一步保证了信号质量。

总结

这个设计不是为了功能(没有它 FPGA 也能下载),而是为了可靠性。

-

没有它: 你的板子可能在干燥的冬天,被手摸一下就坏了。

-

有了它: 它就是 FPGA 的"防弹衣",抗静电能力大大增强,是非常规范的工业级设计。