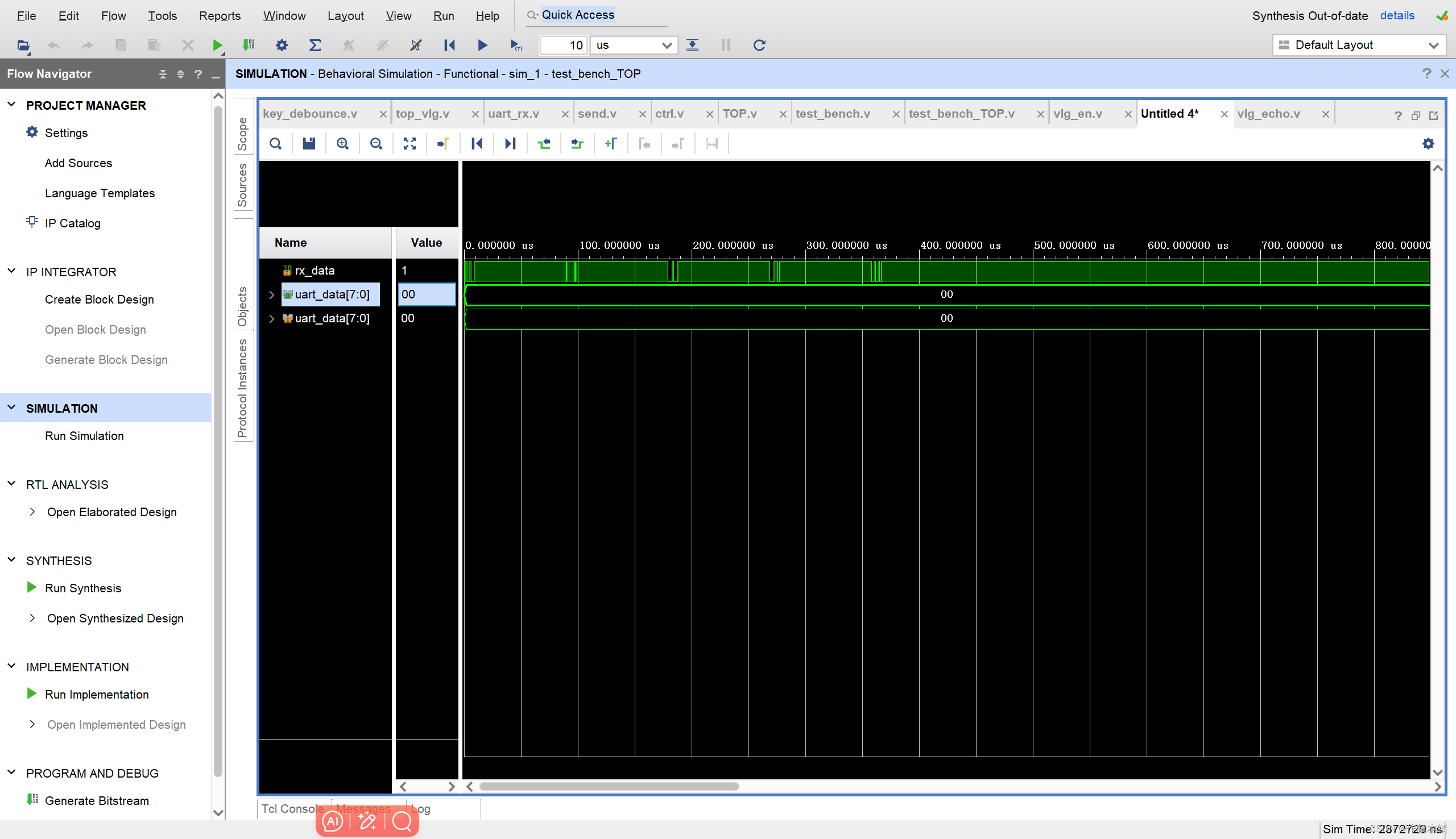

问题描述:uart_data从rx模块输入到ctrl模块后就没有值了。

问题一:首先我仿真例化了两个模块,并且,我选取了单独例化的rx模块中的uart_data 的值,所以在仿真中它是有值的。

Matlab

`timescale 1ns / 1ps

module test_bench_TOP( );

reg sys_clk ;

reg rst_n ;

reg key ;

reg echo ;

wire trig ;

wire tx_data ;

reg rx_data ;

wire[7:0] uart_data ;

wire rx_done ;

parameter SYSCLK = 50_000_000 ;

parameter Baud = 115200 ;

parameter COUNT = SYSCLK/Baud ;//434 传输1比特所需要的时钟周期

parameter MID = COUNT/2 ;

initial

begin

sys_clk = 0 ;

rst_n = 0 ;

key = 1 ;

#10

rst_n = 1 ;

#50000

key = 0 ;

#50000

key = 1 ;

#50000

key = 0 ;

#50000

key = 1 ;

#50000

key = 0 ;

#50000

key = 1 ;

end

always #1 sys_clk = ~sys_clk ; //2ns

initial

begin

uart_out (8'h33); //0011_0011

uart_out (8'hff); //1111_1111

uart_out (8'h18); //0001_1000

uart_out (8'h78);

uart_out (8'h66);

end

//任务函数

task uart_out ;

input [7:0] DATA ;

begin

rx_data = 1 ;///空闲位初始

#20

rx_data = 0 ;///起始位

///传输1bit的计时次数*1周期时间=总时间

#(COUNT*2) rx_data = DATA[0] ;///数据位第一位

#(COUNT*2) rx_data = DATA[1] ;///数据位第二位

#(COUNT*2) rx_data = DATA[2] ;

#(COUNT*2) rx_data = DATA[3] ;

#(COUNT*2) rx_data = DATA[4] ;

#(COUNT*2) rx_data = DATA[5] ;

#(COUNT*2) rx_data = DATA[6] ;

#(COUNT*2) rx_data = DATA[7] ;

#(COUNT*2) rx_data = 0 ;

/*这一步相当于代替了串口调试工具,串口调试工具根据选择的"偶校验"

自动在数据位后面生成"0"或者"1",我们这边只能赋值一个数"0"或者"1"。

我选择赋值为0,所以注定了"8'h31""8'hef""8'h10"是通不过的。

*/

#(COUNT*2) rx_data = 1 ;

#(COUNT*2) ;//停止位也需要时间

# 80000 ;

end

endtask

TOP TOP_1(

. sys_clk ( sys_clk) ,

. rst_n ( rst_n ) ,

. key ( key ) ,

// . rx_data (rx_data ) , //输入串行数据distance

. echo ( echo ) ,

. trig ( trig ) ,

. tx_data ( tx_data)

);

uart_rx uart_rx_1(

. sys_clk (sys_clk ) ,

. rst_n (rst_n ) ,

. rx_data (rx_data ) , //输入串行数据distance

. uart_data(uart_data) , // 输出并行数据

. rx_done (rx_done ) //数据传输完成结束信号

);

endmodule

如果选取TOP模块中的uart_data,它同样是没有值的:

问题二:TOP模块中没有uart_data输入进来,我们仿真的是TOP模块,uart_data都没有输入进来,肯定是没有值的。

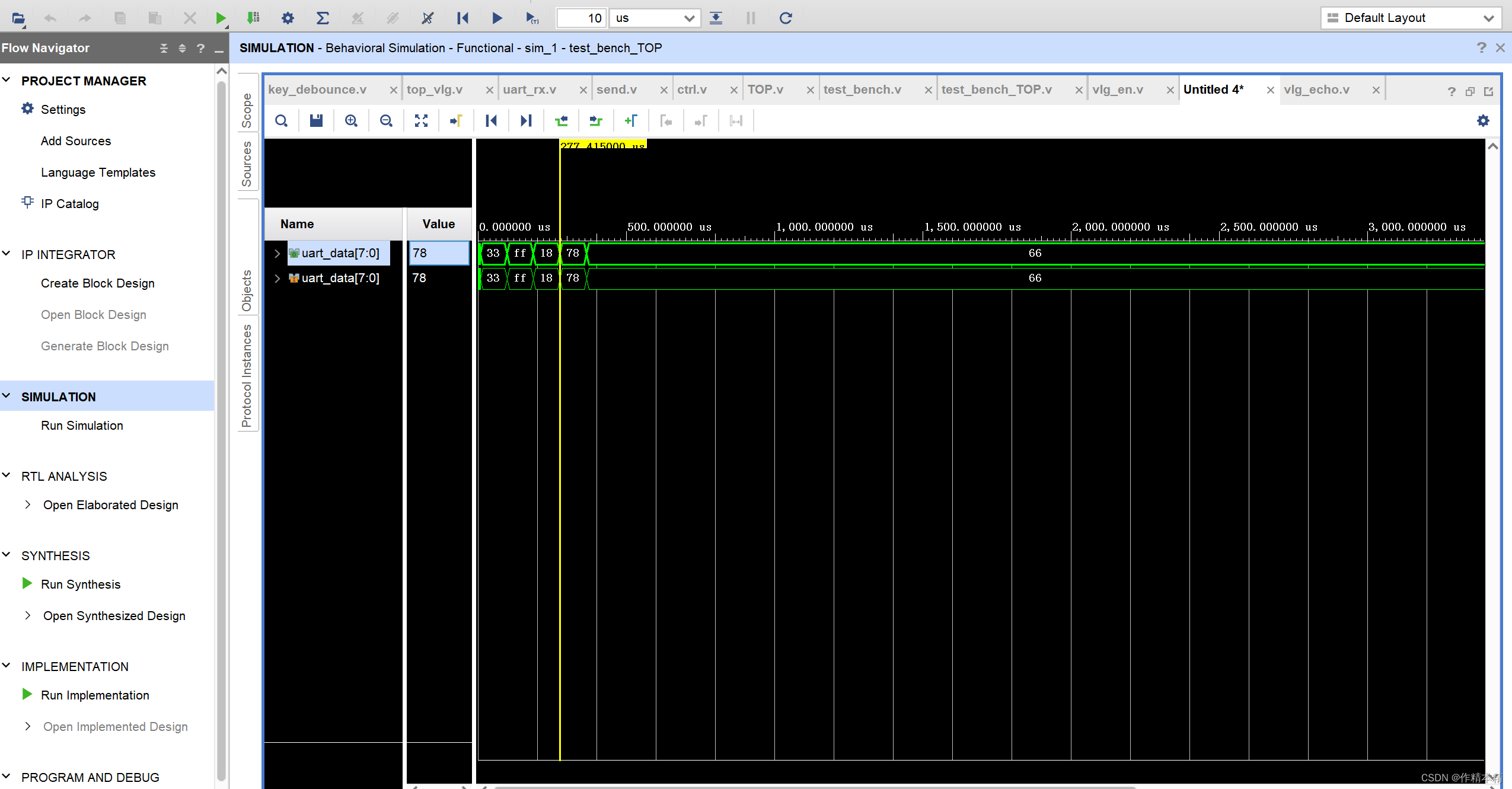

改正后:

Matlab

`timescale 1ns / 1ps

module test_bench_TOP( );

reg sys_clk ;

reg rst_n ;

reg key ;

reg echo ;

wire trig ;

wire tx_data ;

reg rx_data ;

parameter SYSCLK = 50_000_000 ;

parameter Baud = 115200 ;

parameter COUNT = SYSCLK/Baud ;//434 传输1比特所需要的时钟周期

parameter MID = COUNT/2 ;

initial

begin

sys_clk = 0 ;

rst_n = 0 ;

key = 1 ;

#10

rst_n = 1 ;

#50000

key = 0 ;

#50000

key = 1 ;

#50000

key = 0 ;

#50000

key = 1 ;

#50000

key = 0 ;

#50000

key = 1 ;

end

always #1 sys_clk = ~sys_clk ; //2ns

initial

begin

uart_out (8'h33); //0011_0011

uart_out (8'hff); //1111_1111

uart_out (8'h18); //0001_1000

uart_out (8'h78);

uart_out (8'h66);

end

//任务函数

task uart_out ;

input [7:0] DATA ;

begin

rx_data = 1 ;///空闲位初始

#20

rx_data = 0 ;///起始位

///传输1bit的计时次数*1周期时间=总时间

#(COUNT*2) rx_data = DATA[0] ;///数据位第一位

#(COUNT*2) rx_data = DATA[1] ;///数据位第二位

#(COUNT*2) rx_data = DATA[2] ;

#(COUNT*2) rx_data = DATA[3] ;

#(COUNT*2) rx_data = DATA[4] ;

#(COUNT*2) rx_data = DATA[5] ;

#(COUNT*2) rx_data = DATA[6] ;

#(COUNT*2) rx_data = DATA[7] ;

#(COUNT*2) rx_data = 0 ;

/*这一步相当于代替了串口调试工具,串口调试工具根据选择的"偶校验"

自动在数据位后面生成"0"或者"1",我们这边只能赋值一个数"0"或者"1"。

我选择赋值为0,所以注定了"8'h31""8'hef""8'h10"是通不过的。

*/

#(COUNT*2) rx_data = 1 ;

#(COUNT*2) ;//停止位也需要时间

# 80000 ;

end

endtask

TOP TOP_1(

. sys_clk ( sys_clk) ,

. rst_n ( rst_n ) ,

. key ( key ) ,

. rx_data (rx_data ) , //输入串行数据distance

. echo ( echo ) ,

. trig ( trig ) ,

. tx_data ( tx_data)

);

//uart_rx uart_rx_1(

// . sys_clk (sys_clk ) ,

// . rst_n (rst_n ) ,

// . rx_data (rx_data ) , //输入串行数据distance

// . uart_data(uart_data) , // 输出并行数据

// . rx_done (rx_done ) //数据传输完成结束信号

// );

endmodule

问题背景:

我没有认识到rx_data信号只能由电脑产生发送给卡发版,我以为由超声波返回的echo信号计算出的distance也可以作为输入信号让rx接收。