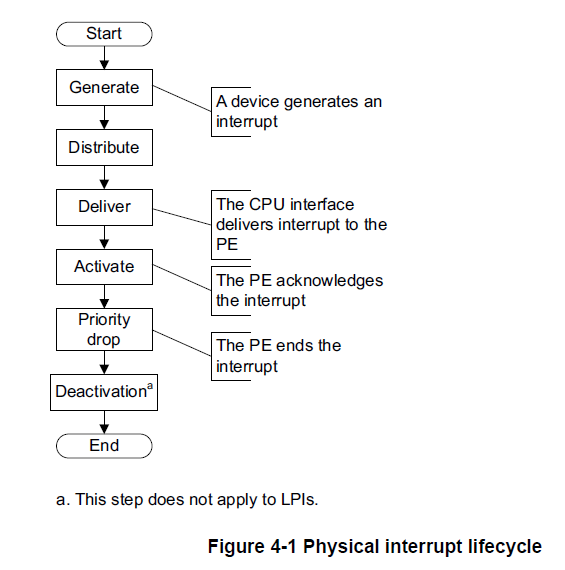

中断生命周期

- 外设通过中断信号线生成中断,或者软件生成中断(SGI)。

- Distributor 和 ReDistributor 配合按照中断分组和中断优先级仲裁后将最高优先级的中断分发到 CPU interface。

- cpu interface 向中断发送到 PE

- PE 读取 IAR 寄存器,中断变为 active 状态,并将中断优先级提升至最高,被称为运行优先级。

- 中断处理完之后,PE 写 EOI 寄存器,中断优先级降低为 active 前的优先级。

- deactivate 中断,使中断在下一次 pending 时,能够再次被 PE take。

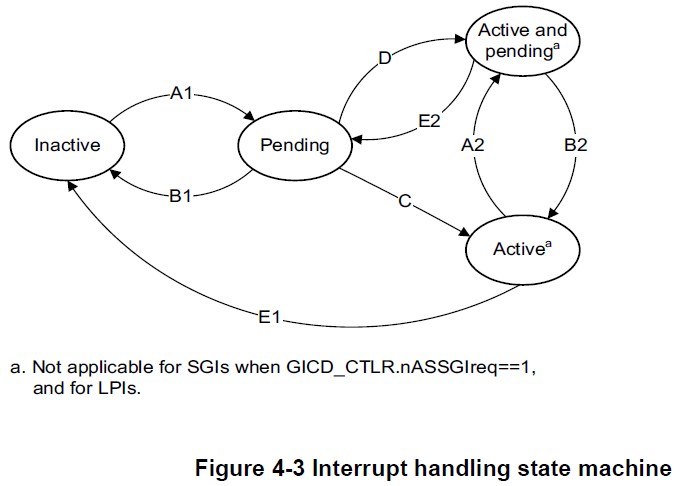

中断状态转换状态机

电平触发

电平触发的状态机变化:A1->D->B2->E1

关键步骤

pending to Active & pending

当 PE 通过读取 CPU 接口中的 IAR(中断应答寄存器)之一来ack中断时,中断从pending转换为Active & pending。 此读取通常是在发生中断异常后执行的中断处理例程的一部分。 然而,软件也可以轮询 IAR。

此时,GIC deassert给PE的中断信号。

Active & pending to active

当外设取消置位中断信号时,中断从Active & pending 转换为active状态。 通常发生在PE写外设的清除中断寄存器。

边沿触发

状态机变化:A1->C->A2->E2

关键步骤

Active to Active & Pending

如果外设重新发出中断信号,则中断将从Active 变为Active & Pending。

Active & Pending to Pending

当 PE 写CPU interface中的 EOIR 时,中断从Active & Pending 状态变为Pending状态。 这表明 PE 已完成对第一个中断实例的处理。此时GIC重新向PE发出中断信号。

中断类型

PPI

PPI 是针对单个特定 PE 的中断,不同的 PE 可以使用相同的 INTID 来指示不同的事件。 PPI 可以是组 0 中断、安全组 1 中断或非安全组 1 中断。 它们可以支持边缘触发或电平触发。

SGI

SGI 通常用于核间通信 ,并通过写入 GIC 中的 SGI 寄存器来生成。 SGI 可以是组 0 或组 1 中断,并且它们仅支持边沿触发。

SPI

SPI 是外设中断,也就是什么DMA,UART,SPI中断之类的。分发器可以将其路由到可以处理中断的指定 PE,或者路由到系统中已配置为接受此类中断的一组 PE 之一的 PE。 SPI 可以是组 0 或组 1 中断 ,并且它们可以支持边沿触发或电平触发。

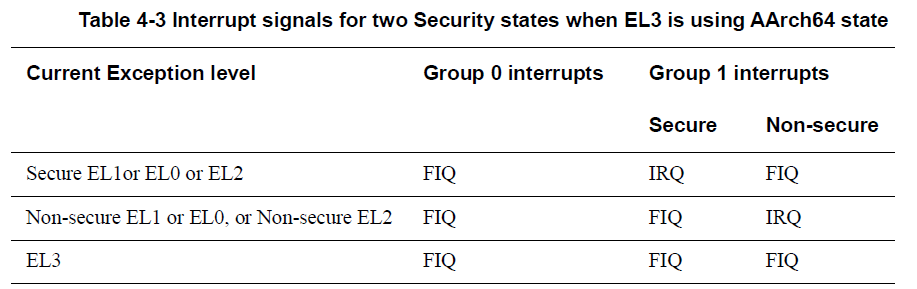

中断分组

GIC 支持三个中断组,每一个中断都需要指定属于某一个中断分组。

- GROUP 0

- Secure GROUP 1

- Non-Secure Group 1

- Group 0中断在任何时候都触发FIQ

- Secure group 1中断发生在PE处于secure状态时触发IRQ

- Non-Secure group 1中断发生在PE处于non-secure状态时触发IRQ

- Secure group 1中断发生在PE处于non-secure状态时触发FIQ

- Non-Secure group 1中断发生在PE处于ecure状态时触发FIQ

- Secure group 1中断发生在PE处于EL3时触发FIQ。

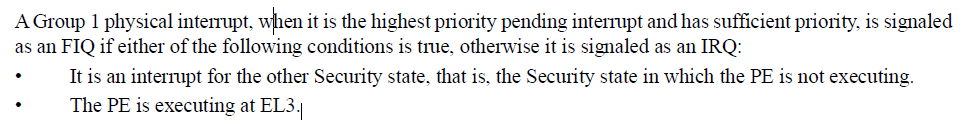

总结下来就是:

当Group 1物理中断是最高优先级的待处理中断并且具有足够的优先级时,就会发出信号。如果下列条件之一为真,则作为FIQ,否则作为IRQ发出信号:

- 是另一个安全状态的中断, 即非PE此时的安全状态的中断。

- PE在EL3执行。

中断路由举例

在一个大系统中,非安全侧运行着诸如Linux的操作系统,安全侧运行如optee的Trust OS为整个系统提供安全服务。CPU分时复用在安全操作系统和非安全操作系统之间切换。

通过将中断分组和配置ARMv8相关寄存器,可以将本该属于安全侧的中断路由到Trust OS中进行处理,本该属于LInux中处理的非安全中断路由到LInux中处理,如图:

这里的SCR_EL3.FIQ和SCR_EL3.IRQ含义为: