文章目录

Bankgroup

Bankgroup是DDR4及后续标准(DDR5)中引入的一个更高层次的组织结构。它将多个Bank组合在一起形成一个Bankgroup,目的是为了进一步提高内存访问的并行性和带宽。

我们每次发送的读写命令都是操作的各个颗粒里面同一个位置的bank。比如chip0的bank3,chip1的bank3,chip2的bank3...

DDR的bankgroup可以理解为是将颗粒分成了group进行操作,也可以抽象成是把黑色颗粒chip内又独立成了各个单独的小颗粒,即各个bankgroup。

Bankgroup 与 Bank 的关系

层级关系:Bankgroup包含多个Bank,可以理解为Bank的上一级组织结构

- 内存芯片 → Bankgroups → Banks → 行/列

访问特性:

- 同一Bankgroup内的Bank共享某些资源

- 不同Bankgroup之间的操作可以更高程度地并行

- 访问不同Bankgroup的延迟小于访问同一Bankgroup内不同Bank的延迟

设目的:

- 减少Bank冲突

- 提高命令总线利用率

- 增加并行数据访问能力

DDR4 中的 Bankgroup

典型配置: 4个Bankgroup,每个Bankgroup 包含 4个Bank (标记为BG0-BG3)

不同 Bankgroup 可以同时激活不同的行

同一Bankgroup内的Bank共享行激活资源

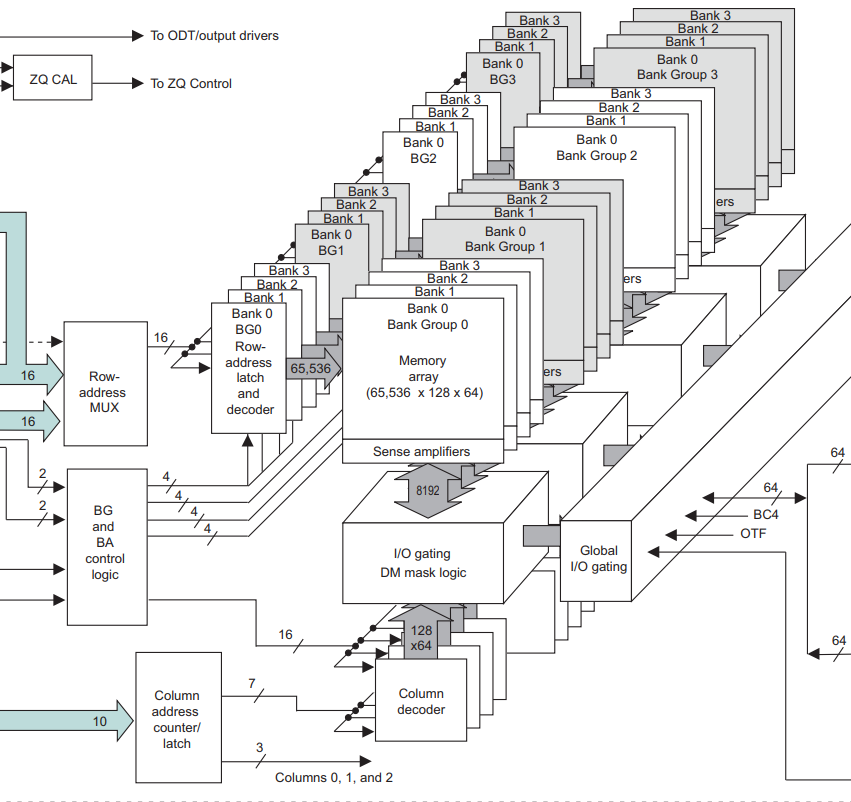

DDR4-3200 8Gb芯片为例

组织结构

如上图所示:

- 4个Bankgroup(BG0-BG3)

- 每个Bankgroup包含4个Bank

- 共16个Bank(4BG×4B)

访问场景

场景1:连续访问BG0-Bank0和BG1-Bank0

- 可以快速连续执行,因为属于不同Bankgroup

- 几乎无额外延迟

场景2:连续访问BG0-Bank0和BG0-Bank1

- 需要额外延迟(tCCD_L)

- 因为属于同一Bankgroup,共享资源

性能影响 :

优化内存访问模式应尽量跨Bankgroup访问

操作系统和内存控制器会尽量将数据分布在不同的Bankgroup

实际应用示例

当CPU需要读取大量连续数据时,内存控制器会将数据分布到不同的Bankgroup中。例如:

- 地址A: BG0-Bank2

- 地址A+64B: BG1-Bank3

- 地址A+128B: BG2-Bank1

- 地址A+192B: BG3-Bank0

这样安排可以实现几乎并行的数据读取,大大提高内存带宽利用率。

推荐阅读 :