在FPGA中使用FIFO时,如果使用FPGA厂商提供的FIFO IP,一般都会有First Word Fall Through FIFO和Standard FIFO类型选项,那么这两种FIFO有什么差异么。两种FIFO的端口是一样的,看不出区别,只有通过仿真,才能看到实际运行时的差别。仿真工程可以从以下地址下载。https://download.csdn.net/download/cjie221/90684941

1.仿真平台

下载仿真工程解压后,在sim文件夹下,可以直接双击tb_top.bat脚本运行,或者打开Modelsim,Change Directory到sim文件夹,执行脚本do tb_top.do来运行。

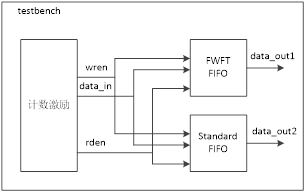

测试平台tb_top.v框图如下图所示,测试源是计数器数值,在计数值为100 ~ 170之间,产生FIFO写使能,FIFO的写数据就是计数值。在计数值为400 ~ 470之间,产生FIFO读使能,FIFO输出数据。

被测试单元分别是两种FIFO。fwft_fifo就是First Word Fall Through FIFO,另一个standard_fifo就是Standard FIFO。FIFO利用网上的开源代码来实现,便于有兴趣的同学进一步查看模块内部信号。FIFO的数据位宽用参数DW来表示,这里取32,另一个参数L表示的是FIFO内地址计数器的位宽,所以实际FIFO深度为2L,这里L取6。不过fwft_fifo代码有点特殊,实际深度为2L+2=66,而standard_fifo实际深度就是2L=64。

2.仿真波形

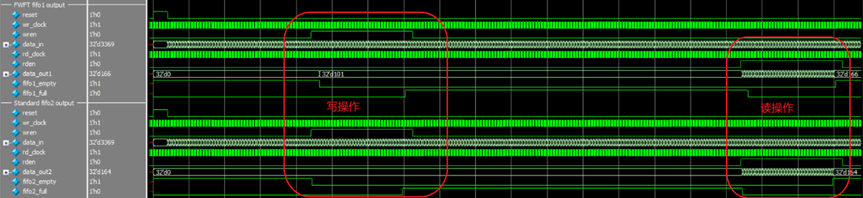

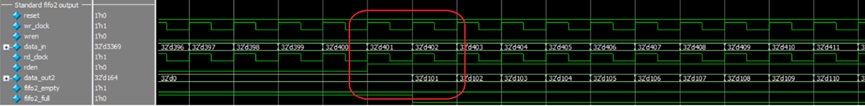

仿真波形如下图所示,同时驱动fwft_fifo和standard_fifo。先进行写操作,执行71次写操作,实际最多只能写入最大深度个数。然后再进行读操作,执行71次读操作。

(1)fwft_fifo

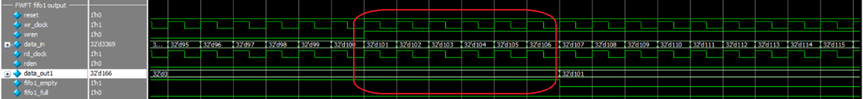

上半部分是fwft_fifo仿真波形,先看写数据波形,当wren为1时,写入数据,可以看到写入6个数据后,empty信号才拉低。相比Standard FIFO,empty信号拉低的时间要更长。在empty信号拉低后,fwft_fifo输出端口data_out1就保持为第1个写入的数据。这个与Standard FIFO也是不同的。

接下来我们再看读数据波形,First Word Fall Through FIFO最大的特点就在于此,当rden为1时,输出端口data_out1立刻就是FIFO输出值。而不像Standard FIFO输出端口有输出至少要延后1个时钟周期。

(2)standard_fifo

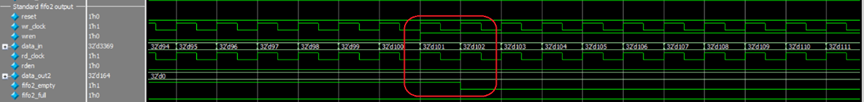

下半部分是standard_fifo仿真波形,先看写数据波形,当wren为1时,写入数据,可以看到只写入1个数据后,empty信号就拉低了,同时输出端口data_out2并没有任何变化。

然后再看读数据波形,当rden为1时,输出端口data_out2不是立刻就有输出值,而是延时1个时钟周期才有输出。当然有些FIFO IP也会提供pipeline out选项允许延时多个时钟周期输出。

3. First Word Fall Through FIFO应用

在哪些场合会用到First Word Fall Through FIFO呢,一般是要求读使能rden信号既作为FIFO的读使能信号,又是其他的模块的控制信号,同时要求数据必须与这个控制信号同步,不能有延时。例如以下这种情况。

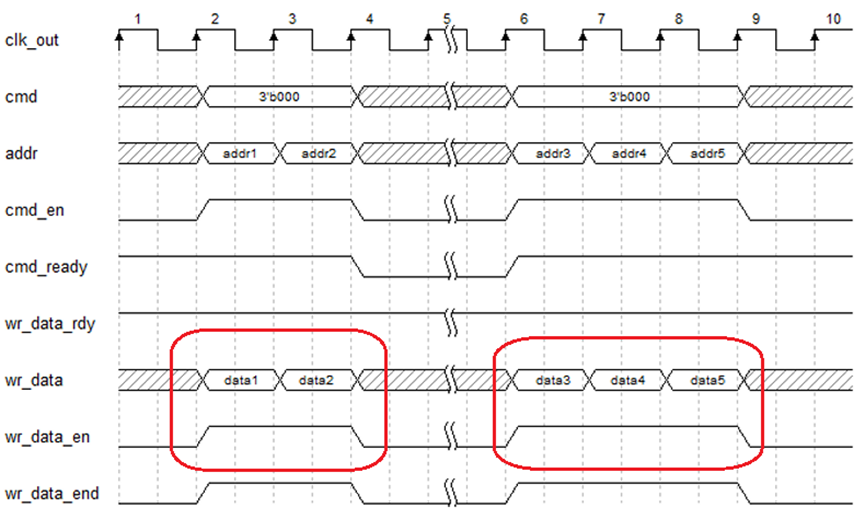

有数据需要写入DDR3控制器,但数据必须要先经FIFO缓存,然后在写入时直接从FIFO搬运。我们看一个DDR3控制器的写操作时序图,写使能信号wr_data_en和写数据wr_data必须是同步的,而如果用wr_data_en作为FIFO的读使能,那么这时采用First Word Fall Through FIFO的话,FIFO的输出数据就可以直接对接写数据端口了。

不过实际应用中大多使用Standard FIFO就可以,First Word Fall Through FIFO使用场合相对较少,并且使用的资源也多一些。