一、MicroBlaze 介绍

MicroBlaze 是由 Xilinx 开发的一种可配置的 32 位 RISC 软处理器内核。它作为 FPGA 设计中的 IP 核,通过 Vivado 工具进行配置和集成。MicroBlaze 提供了高度的灵活性,允许开发人员根据应用需求调整处理器的功能、性能和资源占用。它是 Xilinx FPGA 嵌入式系统设计的重要组成部分,尤其适用于需要定制化硬件加速或复杂控制逻辑的应用场景。

二、MicroBlaze 的特点

- 软核架构

MicroBlaze 是一种软核(soft-core),意味着它完全通过 FPGA 的可编程逻辑实现,而不是像 Zynq 中的 ARM 处理器那样以硬核(hard-core)形式固定在芯片上。

这种软核的设计方式使得 MicroBlaze 可以灵活地适配不同的 FPGA 系列和型号。

- 32 位 RISC 架构

MicroBlaze 遵循精简指令集计算(RISC)原则,具有高效的指令执行能力和较低的功耗。

支持标准的 32 位数据路径和地址空间,能够满足大多数嵌入式系统的需求。

- 可配置性

开发者可以根据具体应用需求对 MicroBlaze 进行配置,例如选择是否启用硬件乘法器、浮点单元(FPU)、缓存(Cache)、调试接口等。

这种可配置性使得 MicroBlaze 能够在性能与资源消耗之间取得平衡。

- 丰富的外设支持

MicroBlaze 可以通过 AXI 总线与其他 IP 核(如 UART、GPIO、SPI、I2C 等)连接,从而构建完整的嵌入式系统。

它支持多种总线协议(如 AXI4、AXI-Lite 和 PLB),便于与外部设备通信。

- 多语言开发支持

MicroBlaze 支持使用 C/C++、汇编语言或 RTL(寄存器传输级)设计语言进行开发。

使用 C/C++ 编程时,可以借助 Xilinx 提供的 SDK(Software Development Kit)或 Vitis 工具链进行软件开发。

- 硬件加速能力

在 FPGA 上,MicroBlaze 可以与硬件加速模块协同工作,将计算密集型任务卸载到专用硬件中,从而提高整体系统的性能。

|--------|-----------------------------|--------------------------------|

| 特性 | MicroBlaze | Zynq |

| 处理器类型 | 软核(Soft-Core) | 硬核(Hard-Core) |

| 灵活性 | 高度可配置,适合定制化设计 | 固定架构,但支持强大的 ARM 生态 |

| 性能 | 受 FPGA 资源限制,性能相对较低 | 高性能,适合复杂计算任务 |

| 开发工具 | Vivado + SDK/Vitis | Vivado + PetaLinux/Vitis |

| 适用场景 | 嵌入式控制、小型系统 | 高性能嵌入式系统、复杂应用 |

| 硬件资源占用 | 依赖 FPGA 的逻辑资源, 占用较少或较多取决于配置 | 固定占用 FPGA 的硬核资源, 额外的 PL 资源可用 |

| 实时性 | 适合简单的实时任务 | 支持复杂的实时操作系统 (如 Linux、FreeRTOS) |

| 外设支持 | 通过 AXI 总线连接外设,灵活配置 | 内置丰富的外设接口 (如 DDR 控制器、千兆以太网) |

| 功耗 | 功耗较低,适合资源受限的场景 | 功耗较高,适合高性能需求的应用 |

| 典型应用 | 工业控制、传感器管理、简单通信协议处理 | 视频处理、机器学习、复杂嵌入式系统 |

**三、**开发流程

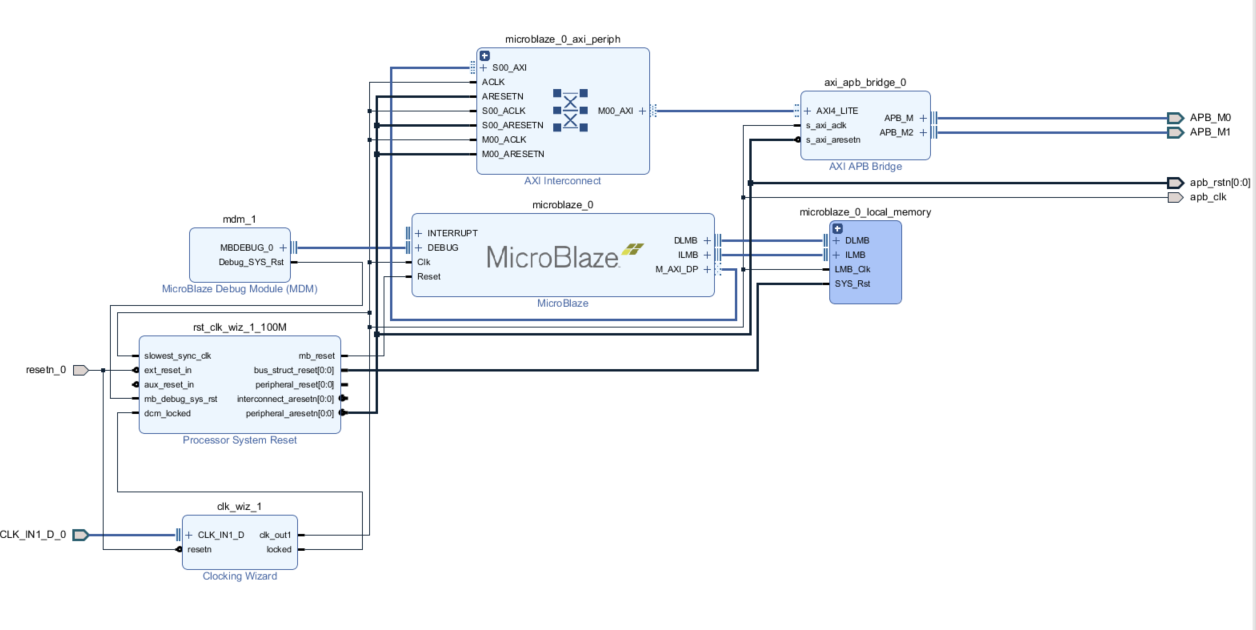

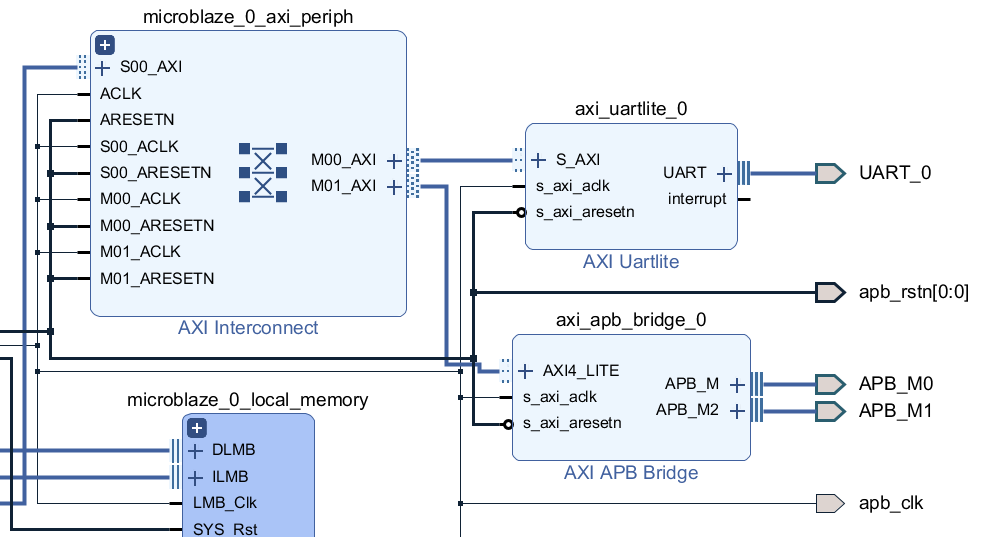

最终搭建的工程如上图所示。可输出两路apb信号

1. 硬件设计阶段

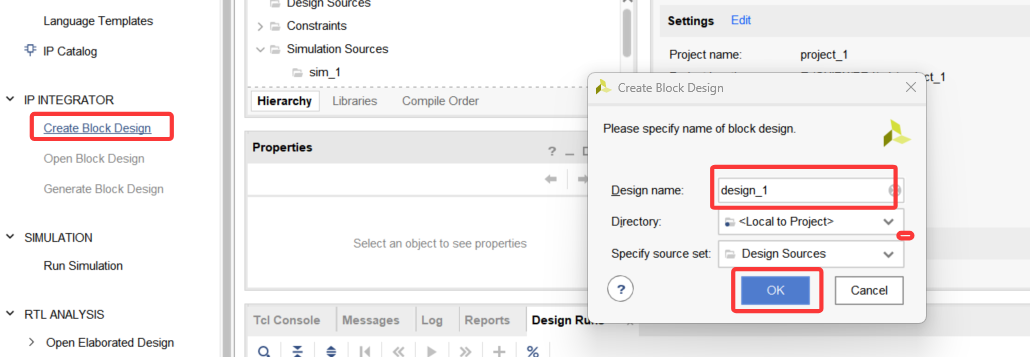

01.使用 Vivado 创建 FPGA 工程

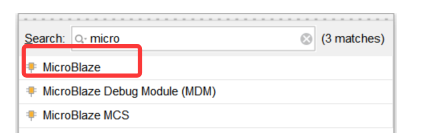

02.添加 MicroBlaze IP 核

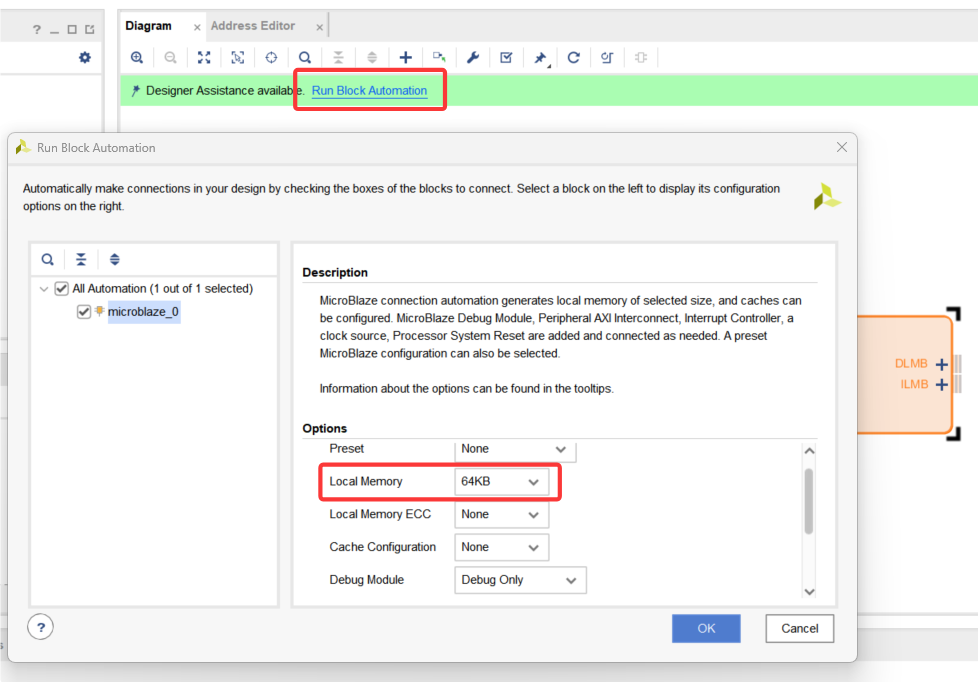

03.配置 MicroBlaze 的参数(如缓存大小、总线类型、外设接口等)

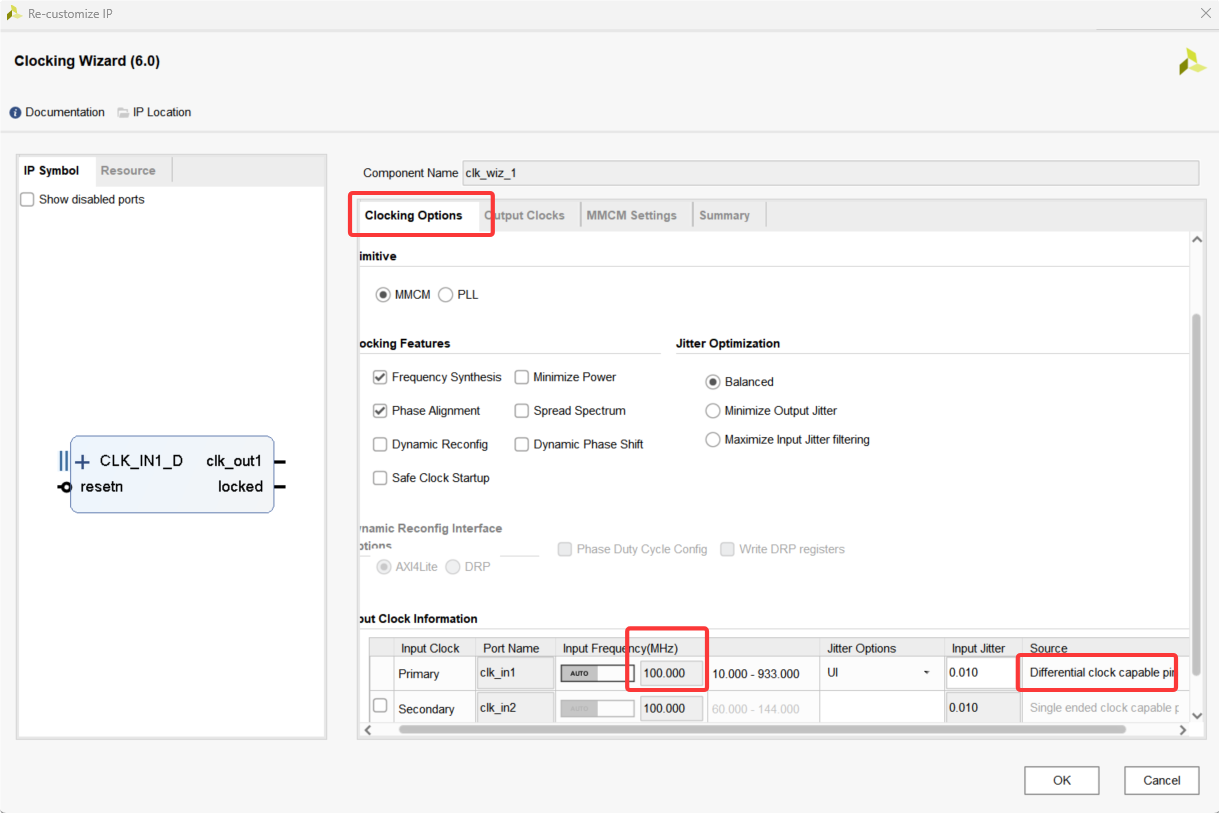

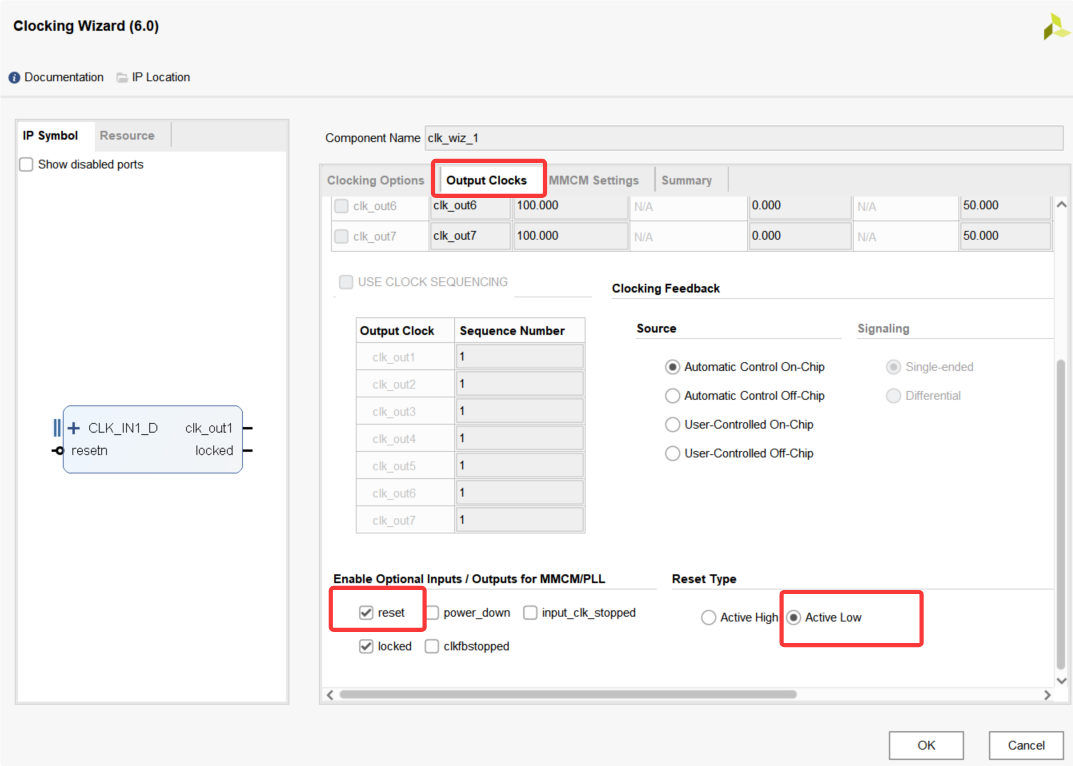

04.时钟配置(可以选择差分时钟或单端时钟输入)

时钟复位设置:低有效复位

05.存储器或外设连接

将 MicroBlaze 与其他 IP 核(如存储器、外设)连接,我的工程需要两路apb信号,因此我使用了AXI Interconnect 和axi_apb_bridge桥进行数据的转换。

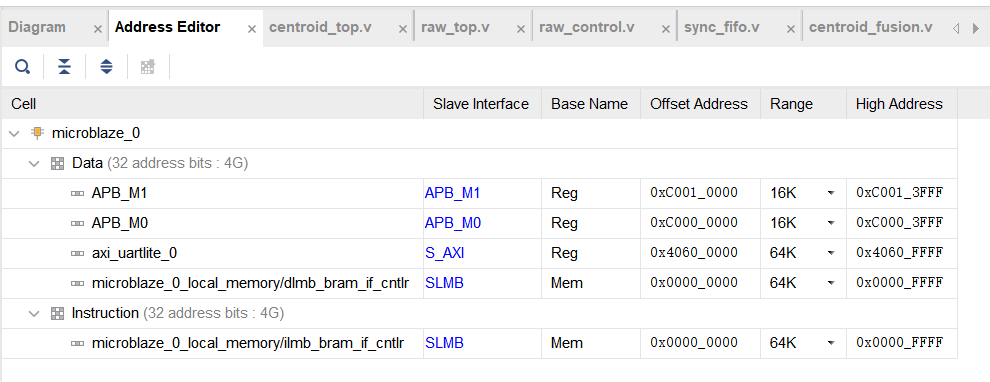

06.地址设置

2. 软件开发阶段

01.导出硬件设计文件到 SDK 或 Vitis 工具链。

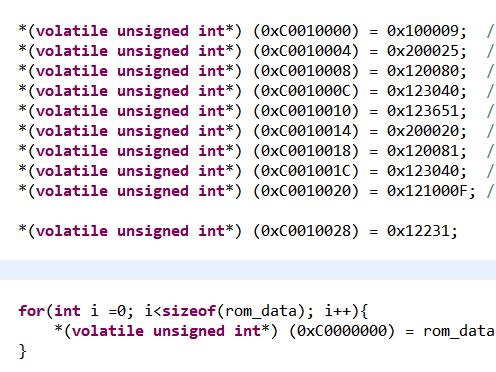

02.编写 C/C++ 程序来实现系统功能。

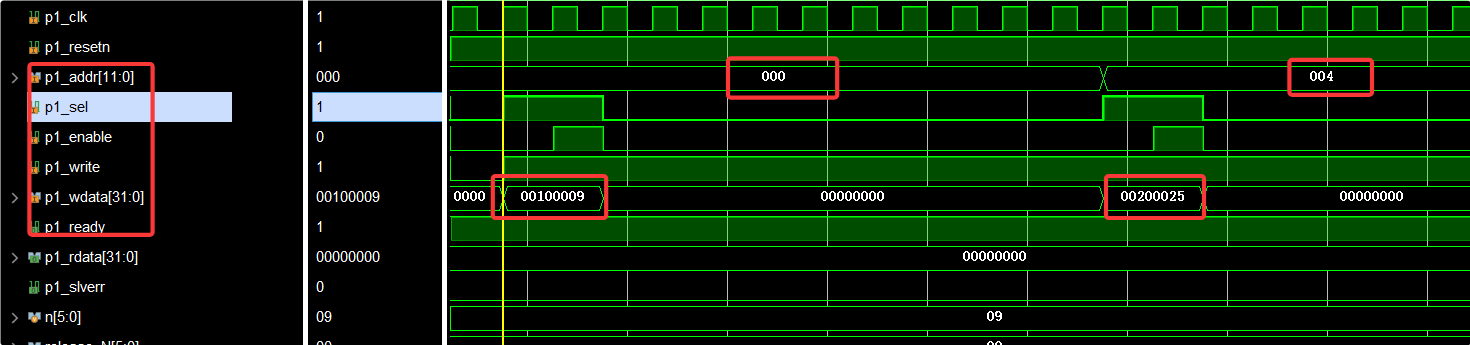

由下图仿真波形可见,使用MicroBlaze 实现了正确的数据写入

03.使用调试工具(如 JTAG 接口)进行代码调试和优化。