注:本文为 "Xilinx FPGA | 管脚约束 / 时序约束 / 问题解析" 相关文章合辑。

略作重排,未整理去重。

如有内容异常,请看原文。

Xilinx FPGA 管脚 XDC 约束之:物理约束

FPGA技术实战 于 2020-02-04 17:14:53 发布

说明:本文简单介绍 Xilinx FPGA 管脚物理约束,包括位置(管脚)约束和电气约束。

1. 普通 I/O 约束

管脚位置约束 :set_property PACKAGE_PIN "管脚编号" [get_ports "端口名称"]

管脚电平约束 :set_property IOSTANDARD "电压" [get_ports "端口名称"]

举例:

tcl

set_property IOSTANDARD LVCMOS33 [get_ports sys_clk]

set_property IOSTANDARD LVCMOS33 [get_ports {led[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[1]}]

set_property PACKAGE_PIN U18 [get_ports sys_clk]

set_property PACKAGE_PIN M14 [get_ports {led[0]}]

set_property PACKAGE_PIN M15 [get_ports {led[1]}]注意:

- 以上语法对大小写敏感。

- 端口名称为数组时,需要用

{}括起来,端口名不能为关键字。

2. 差分信号约束

2.1 普通差分约束

差分信号约束语法与第 1 节相同,此处仅举例。

1)HR I/O Bank,VCCO = 3.3V,HDMI 接口约束

tcl

set_property PACKAGE_PIN N18 [get_ports TMDS_clk_p]

set_property PACKAGE_PIN V20 [get_ports {TMDS_data_p[0]}]

set_property IOSTANDARD TMDS_33 [get_ports TMDS_clk_p]

set_property IOSTANDARD TMDS_33 [get_ports {TMDS_data_p[0]}]2)HP I/O Bank,VCCO = 1.8V,HDMI 接口约束

tcl

set_property PACKAGE_PIN N18 [get_ports TMDS_clk_p]

set_property PACKAGE_PIN V20 [get_ports {TMDS_data_p[0]}]

set_property IOSTANDARD LVDS [get_ports TMDS_clk_p]

set_property IOSTANDARD LVDS [get_ports {TMDS_data_p[0]}]注意:

- 差分信号约束,只约束 P 管脚即可,系统自动匹配 N 管脚约束,当然

_P和_N管脚都约束也没有问题。 - 差分信号电平要根据 VCCO Bank 电压进行相应的约束。

2.2 收发器差分信号约束

1)收发器 MGTREFCLK 时钟约束

管脚位置约束 :set_property LOC "管脚编号" [get_ports "端口名称"]

举例:

tcl

set_property LOC G7 [get_ports Q2_CLK0_GTREFCLK_PAD_N_IN]

set_property LOC G8 [get_ports Q2_CLK0_GTREFCLK_PAD_P_IN]2)收发器 MGT 通道约束

对于 GTXE2_CHANNEL 通道约束:一种方法是利用 7 系列 FPGA 收发器向导,在配置好收发器配置参数后,自动生成 XDC 模板,然后将该模板应用到自己的设计中;另一种方法是自己编写 XDC 约束文件,其位约束位置要参照具体原理图信号管脚来进行编写约束文件。

举例:对于图 1 中四通道收发器对 GTXE2_CHANNEL 约束。

图 1:四通道 GTX 收发器框图

收发器通道位置约束 :set_property LOC "GTXE2_CHANNEL_X* Y*" [get_cells "gtxe_2例化路径"]

tcl

##---------- Set placement for gt0_gtx_wrapper_i/GTXE2_CHANNEL ------

set_property LOC GTXE2_CHANNEL_X0Y8 [get_cells gtx_support_i/gtx_init_i/inst/gtx_i/gt0_gtx_i/gtxe2_i]

##---------- Set placement for gt1_gtx_wrapper_i/GTXE2_CHANNEL ------

set_property LOC GTXE2_CHANNEL_X0Y9 [get_cells gtx_support_i/gtx_init_i/inst/gtx_i/gt1_gtx_i/gtxe2_i]

##---------- Set placement for gt2_gtx_wrapper_i/GTXE2_CHANNEL ------

set_property LOC GTXE2_CHANNEL_X0Y10 [get_cells gtx_support_i/gtx_init_i/inst/gtx_i/gt2_gtx_i/gtxe2_i]

##---------- Set placement for gt3_gtx_wrapper_i/GTXE2_CHANNEL ------

set_property LOC GTXE2_CHANNEL_X0Y11 [get_cells gtx_support_i/gtx_init_i/inst/gtx_i/gt3_gtx_i/gtxe2_i]注意 :

gtxe_2 例化路径参照图 2 所示,路径名称依据具体工程实现进行修改。

图 2:收发器通道约束路径分析

Vivado:解读 XDC 约束文件

崽崽今天要早睡 已于 2022-07-12 14:36:46 修改

代码:

tcl

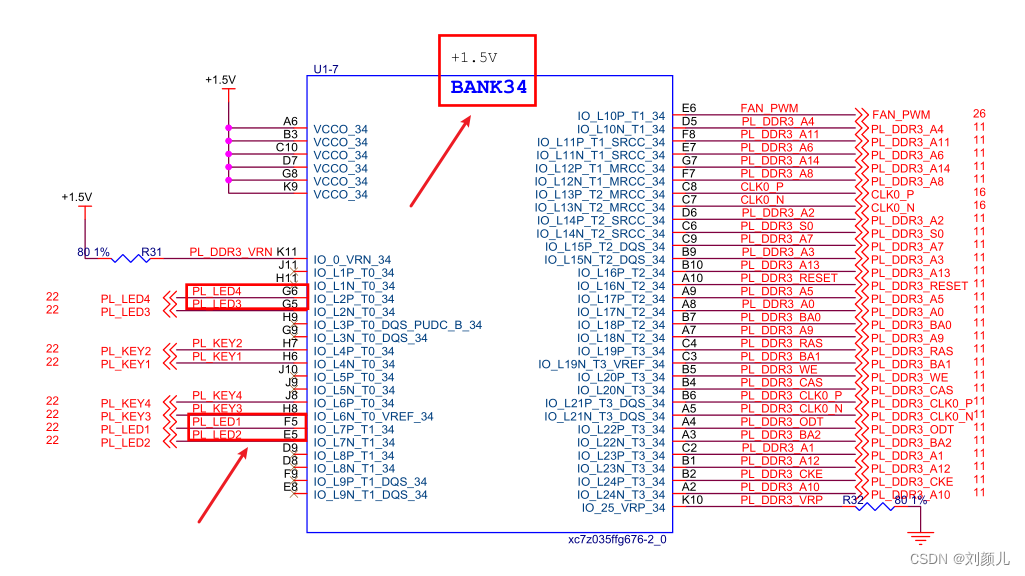

// 约束引脚号

set_property PACKAGE_PIN F5 [get_ports {led_tri_o[0]}]

set_property PACKAGE_PIN E5 [get_ports {led_tri_o[1]}]

set_property PACKAGE_PIN G5 [get_ports {led_tri_o[2]}]

set_property PACKAGE_PIN G6 [get_ports {led_tri_o[3]}]

// 约束电压

set_property IOSTANDARD LVCMOS15 [get_ports {led_tri_o[3]}]

set_property IOSTANDARD LVCMOS15 [get_ports {led_tri_o[2]}]

set_property IOSTANDARD LVCMOS15 [get_ports {led_tri_o[1]}]

set_property IOSTANDARD LVCMOS15 [get_ports {led_tri_o[0]}]XDC 编写的语法

约束引脚号:set_property PACKAGE_PIN "引脚编号" [get_ports "端口名称"]

约束电压:set_property IOSTANDARD "电平标准" [get_ports "端口名称"]

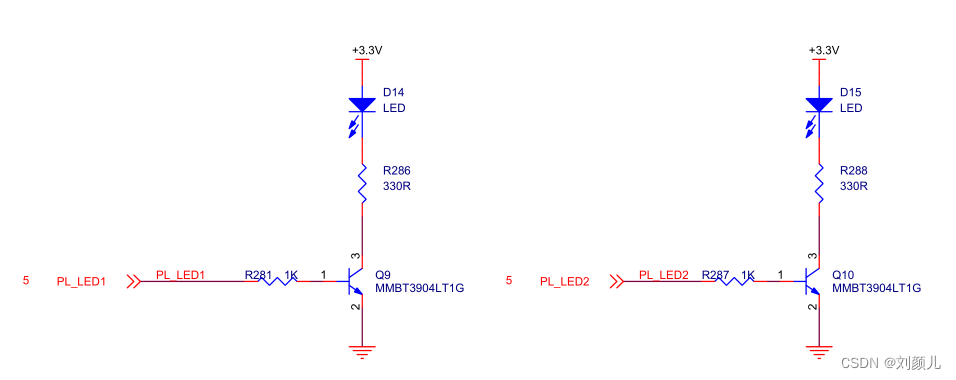

重点

通过原理图,查看 LED 与 FPGA 中实际引脚相连位置,然后查看驱动该 FPGA 的 Bank 是多大的电压。如果是 1.5V 电压驱动,那就是 LVCMOS15,如果是 1.8V 驱动,那就是 LVCMOS18。

解读

set_property:设置属性IOSTANDARD:IO 标准LVCMOS15:1.5Vget_ports:获取端口led_tri_o[3]:第 3 个 LED 端口PACKAGE_PIN:引脚F5:引脚约束到 F5

通俗理解

set_property IOSTANDARD LVCMOS15 [get_ports {led_tri_o[3]}]:将led_tri_o[3]的 IO 标准修改为 1.5V。set_property PACKAGE_PIN G6 [get_ports {led_tri_o[3]}]:将led_tri_o[3]约束到 G6 引脚。

Vivado 进行管脚约束(详细教程)

千寻xun 已于 2023-08-16 09:10:11 修改

1. 图形化界面

工程编译通过后,点击

打开后长这样:

点击 layout 选择 IO planning:

点击 IO port 进行管脚定义:

说明:

设置好保存。

2. 直接使用代码定义

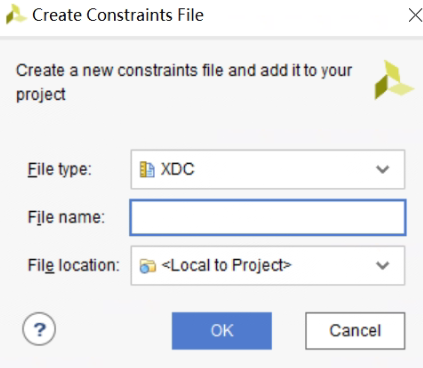

添加约束文件:

新建 XDC 文件:

新建好后打开,添加以下代码:

tcl

set_property PACKAGE_PIN AF25 [get_ports rst]

set_property IOSTANDARD LVCMOS33 [get_ports rst]

set_property PULLDOWN true [get_ports rst]将信号名 rst 绑定到 AF25 引脚,其他信号同理。将信号名 rst 电平定义为 LVCMOS33,即 3.3V 电平。set_property PULLDOWN true [get_ports rst] 是将信号名 rst 下拉,非必须,也可使用上拉 PULLUP。

约束好保存编译即可。

FPGA 管脚约束之电平标准

横二彪 于 2024-02-26 17:33:41 修改

在对 FPGA 的管脚进行约束时,常常会看到诸如 LVCMOS18、LVCMOS25、LVDS、LVDS25 等电平标准,这些都是一系列的电平标准。

对于数字电路而言,数字电路表示电平的状态只有 1 和 0。在实际电路中,需要约定何种电压为 1,何种电压为 0。数字电路中的双阈值定义如下:例如 TTL 接口电平标准,对于输出端,状态 1 的电压要求为大于等于 2.4V,状态 0 的电压要求为小于等于 0.5V;对于输入端,状态 1 的判定要求为大于等于 2.0V,状态 0 的判定要求为小于等于 0.8V。即需要大于某一个阈值表示电平 1,小于某一个阈值表示电平 0。

电平标准的分类

常见的 IO 接口可分为单端 IO 接口和差分 IO 接口,详细的 IO 标准参见下图。单端 IO 接口和差分 IO 接口均满足高速接口传输,区别在于应用场合不同。

TTL

TTL(Transistor-Transistor Logic)是基于三极管结构的数字系统接口电平标准。工作于 TTL 接口标准下的数字电路,其内部有源器件的标准电源供给为 5V,输出、输入情况如下:

- 输出端:

- 状态 1:电压大于等于 2.4V

- 状态 0:电压小于等于 0.5V

- 输入端:

- 状态 1:电压大于等于 2.0V

- 状态 0:电压小于等于 0.8V

LVTTL

由于 TTL 的电压范围较大,对改善噪声干扰并无明显好处,且会增加系统功耗,还会影响数字电路的响应速度。因此,后来形成了 LVTTL(Low Voltage Transistor-Transistor Logic,低压 TTL 电平标准)。

LVTTL3V3

LVTTL3V3 的内部有源器件标准电源供给为 3.3V,输出、输入情况如下:

- 输出端:

- 状态 1:电压大于等于 2.4V

- 状态 0:电压小于等于 0.4V

- 输入端:

- 状态 1:电压大于等于 2.0V

- 状态 0:电压小于等于 0.8V

LVTTL2V5

LVTTL2V5 的内部有源器件标准电源供给为 2.5V,输出、输入情况如下:

- 输出端:

- 状态 1:电压大于等于 2.0V

- 状态 0:电压小于等于 0.2V

- 输入端:

- 状态 1:电压大于等于 1.7V

- 状态 0:电压小于等于 0.7V

CMOS

CMOS(Complementary Metal Oxide Semiconductor)是基于 NMOS 和 PMOS 组成的 MOS 管结构的数字系统接口电平标准。工作于 CMOS 接口标准下的数字电路,其内部有源器件的标准电源供给为 5V,输出、输入情况如下:

- 输出端:

- 状态 1:电压大于等于 4.45V

- 状态 0:电压小于等于 0.5V

- 输入端:

- 状态 1:电压大于等于 3.5V

- 状态 0:电压小于等于 1.5V

CMOS 与 TTL 接口相比,具有更大的噪声容限,且输入阻抗远大于 TTL 输入阻抗。

LVCMOS

鉴于功耗和响应速度的考虑,CMOS 也衍生出了 LVCMOS 接口标准。由于 MOS 管的导通门限较低,因此 LVCMOS 更容易使用较低的电压进行通信。

LVCMOS3V3

LVCMOS3V3 的内部有源器件标准电源供给为 3.3V,输出、输入情况如下:

- 输出端:

- 状态 1:电压大于等于 3.2V

- 状态 0:电压小于等于 0.4V

- 输入端:

- 状态 1:电压大于等于 2.0V

- 状态 0:电压小于等于 0.7V

LVCMOS2V5

LVCMOS2V5 的内部有源器件标准电源供给为 2.5V,输出、输入情况如下:

- 输出端:

- 状态 1:电压大于等于 2.0V

- 状态 0:电压小于等于 0.4V

- 输入端:

- 状态 1:电压大于等于 1.7V

- 状态 0:电压小于等于 0.7V

LVCMOS1V8

LVCMOS1V8 的内部有源器件标准电源供给为 VCC=1.8V,其容忍度会影响输出、输入情况如下:

- 输出端:

- 状态 1:电压大于等于 VCC-0.45V(若 VCC 精确等于 1.8V,则为 1.35V)

- 状态 0:电压小于等于 0.45V

- 输入端:

- 状态 1:电压大于等于 0.65 倍的 VCC(若 VCC 精确等于 1.8V,则为 1.17V)

- 状态 0:电压小于等于 0.35 倍的 VCC(若 VCC 精确等于 1.8V,则为 0.63V)

LVCMOS1V5

LVCMOS1V5 的内部有源器件标准电源供给为 VCC=1.5V,其容忍度会影响输出、输入情况如下:

- 输出端:状态 1 越接近 VCC 越好,状态 0 越接近 0V 越好

- 输入端:

- 状态 1:电压大于等于 0.65 倍的 VCC(若 VCC 精确等于 1.5V,则为 0.975V)

- 状态 0:电压小于等于 0.35 倍的 VCC(若 VCC 精确等于 1.5V,则为 0.525V)

LVCMOS1V2

LVCMOS1V2 的内部有源器件标准电源供给为 VCC=1.2V,其容忍度会影响输出、输入情况如下:

- 输出端:状态 1 越接近 VCC 越好,状态 0 越接近 0V 越好

- 输入端:

- 状态 1:电压大于等于 0.65 倍的 VCC(若 VCC 精确等于 1.2V,则为 0.78V)

- 状态 0:电压小于等于 0.35 倍的 VCC(若 VCC 精确等于 1.2V,则为 0.42V)

LVDS

LVDS(低电压差分信号)的特性如下:LVDS 的电压摆幅仅有 350mV 左右,电流也仅有 3.5mA 左右,且采用差分传输,因此具有高速、超低功耗、低噪声和低成本等优良特性。

RS232

RS232 是美国电子工业协会(EIA)制定的一种串行物理接口标准。RS232 的标准电源供给为 ±12V 或 ±15V,状态 1 的电压要求为 -15V 到 -3V 之间,状态 0 的电压要求为 3V 到 15V 之间。

RS485

RS485 是 RS232 的升级版,采用差分形式传递信息,抗干扰性优于 RS232。RS485 的状态 1 要求两线之间的电压差为 2V 到 6V 之间,状态 0 要求两线之间的电压差为 -6V 到 -2V 之间。

不同标准之间能否混连?

受限于配置情况,有时无法找到统一的电平标准进行通信。单端和差分接口无法兼容,因为它们的物理连线不同。但对于同种类接口,如果 A 电平标准的输出符合 B 电平标准的输入,则称 A 的输出可驱动 B 的输入;反之亦然,则称 A、B 两种电平标准可相互驱动。例如,CMOS 的输出可以驱动 TTL 输入,但 TTL 的输出无法驱动 CMOS 输入,因为 TTL 的状态 1 输出电压(大于等于 2.4V)无法达到 CMOS 判决状态 1 所需的电压(大于等于 3.5V)。然而,LVTTL3V3 和 LVCMOS3V3 可以相互驱动,因为它们的输出都能满足彼此的输入判定要求。

如何得知 FPGA 上的引脚支持何种标准?

电平标准分为内部和外部扩展。对于芯片内部引脚,通常使用 Vivado 的 TCL 命令 get_io_standards -of 查询。对于外部扩展引脚,则需查询外部扩展的电平手册。

以 BANK117 为例,其支持的电平标准如下:

Xilinx FPGA 未使用管脚的默认电平设置方法

qsj_csdn 于 2021-03-31 17:17:02 发布

方法一:直接在约束文件中写入 tcl 命令

tcl

set_property BITSTREAM.CONFIG.UNUSEDPIN PULLUP [current_design]可选参数有:PULLUP、PULLDOWN、PULLNONE。

方法二:在软件中设置

-

在运行实现(run implementation)后,点击"open implementation design"。

-

打开后,右键点击"Generate Bitstream",然后点击"bitstream setting"。

-

点击"Configure additional bitstream settings"。

-

点击"configuration"。

-

向下拉动右边的滚动条到指定位置,即可看到设置的复选框,并可设置为期望的输出电平状态。

Vivado Error 问题之 [DRC NSTD-1] 问题解决

虚怀若水 于 2021-10-30 19:24:32 发布

1. 问题描述

Vivado Error 问题警告如下所示:

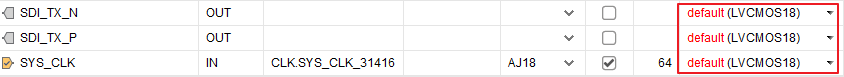

[DRC NSTD-1] Unspecified I/O Standard: 1 out of 9 logical ports use I/O standard (IOSTANDARD) value 'DEFAULT', instead of a user assigned specific value.

This may cause I/O contention or incompatibility with the board power or connectivity affecting performance, signal integrity or in extreme cases cause damage to the device or the components to which it is connected. To correct this violation, specify all I/O standards. This design will fail to generate a bitstream unless all logical ports have a user specified I/O standard value defined. To allow bitstream creation with unspecified I/O standard values (not recommended), use this command: set_property SEVERITY {Warning} [get_drc_checks NSTD-1]. NOTE: When using the Vivado Runs infrastructure (e.g. launch_runs Tcl command), add this command to a .tcl file and add that file as a pre-hook for write_bitstream step for the implementation run. Problem ports: SYS_CLK.在 IO 设置界面如下所示:

由于 IO 工作电压未明确定义,因此需要进行以下操作。

2. 解决方法

新建一个 .tcl 文件,写入以下内容:

bash

set_property SEVERITY {Warning} [get_drc_checks NSTD-1]

set_property SEVERITY {Warning} [get_drc_checks UCIO-1]

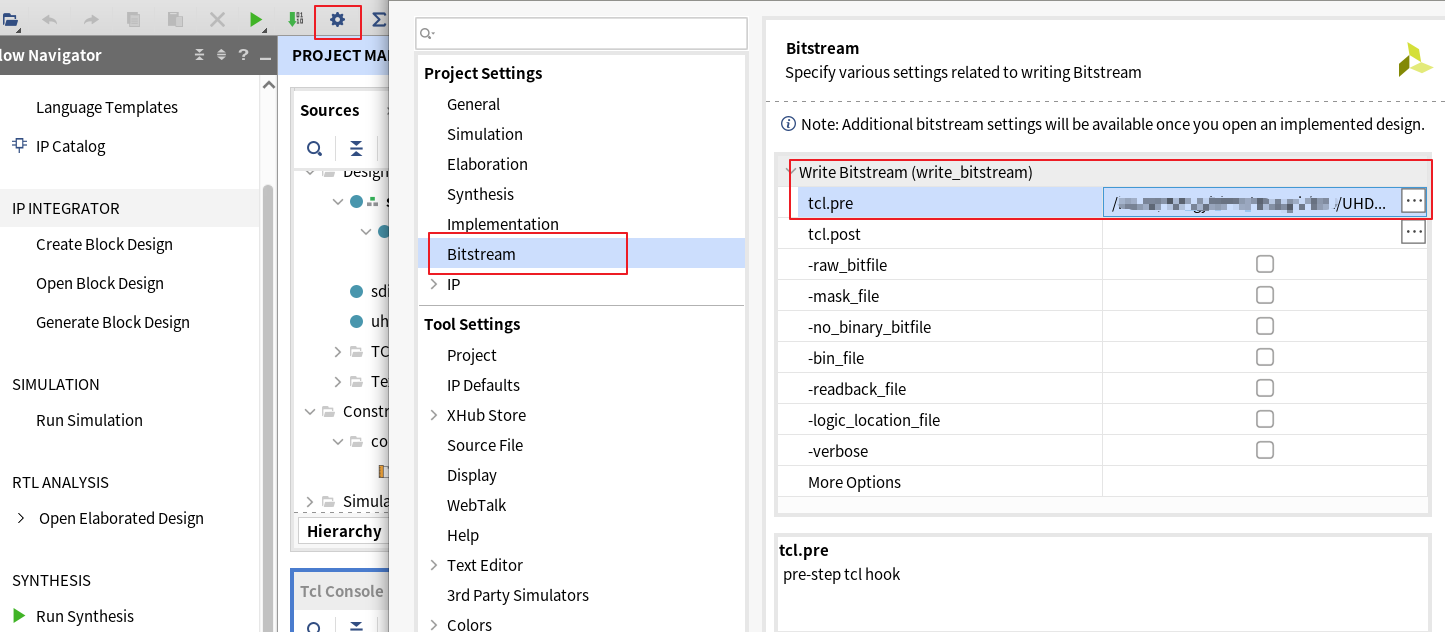

set_property SEVERITY {Warning} [get_drc_checks RTSTAT-1]在 Vivado 设置中加入该文件:

重新编译后,错误警告消失。

Vivado 约束未使用引脚

mail-mail 于 2022-06-10 15:06:03 修改

有两种方法:

方法一:在约束文件中进行设置

tcl

set_property BITSTREAM.CONFIG.UNUSEDPIN Pulldown [current_design]

set_property BITSTREAM.CONFIG.UNUSEDPIN Pullup [current_design]

set_property BITSTREAM.CONFIG.UNUSEDPIN Pullnone [current_design]以上语句三选一,具体选择取决于实际需求。通常选择最后一条,使未使用引脚悬空。

方法二:在 Vivado 软件中进行设置

具体方法可参考以下链接:

- Xilinx FPGA未使用管脚的默认电平设置方法_vivado不用的引脚 默认电平-CSDN博客(上文)

https://blog.csdn.net/qsj_csdn/article/details/115354286

以上方法未经验证,但可以尝试使用以下方式:

- Vivado Error问题之[DRC NSTD-1] 问题解决-CSDN博客(上文)

https://blog.csdn.net/m0_37779673/article/details/121054991

Vivado 中关于管脚约束错误的一种解决方法

csdnqiang 于 2020-04-27 11:27:39 发布

在 Vivado 中,有的 IP 核已经包含了模块的引脚配置,这样在约束文件中就不用写相应的约束设置。然而在生成位码流的时候可能会出现如下错误提示:

[DRC UCIO-1] Unconstrained Logical Port:

未约束的逻辑端口:16 out of 22 logical ports have no user-assigned specific location constraint (LOC).

22 个逻辑端口中有 16 个没有用户指定的具体位置约束(LOC)。

This may cause I/O contention or incompatibility with the board power or connectivity affecting performance, signal integrity or, in extreme cases, cause damage to the device or the components to which it is connected.

这可能导致 IO 竞争、板卡电源或连接不兼容,从而影响性能、信号完整性,或者在极端情况下损坏设备或与其连接的组件。

To correct this violation, specify all pin locations.

为修正此违规,请指定所有引脚的位置。

This design will fail to generate a bitstream unless all logical ports have a user-specified site LOC constraint defined.

除非为所有逻辑端口定义了用户指定的站点位置约束,否则此设计将无法生成比特流文件。

To allow bitstream creation with unspecified pin locations (not recommended), use this command:

若要允许在未指定引脚位置的情况下生成比特流文件(不推荐),可以使用以下命令:

tclset_property SEVERITY {Warning} [get_drc_checks UCIO-1]NOTE:

注意:When using the Vivado Runs infrastructure (e.g., launch_runs Tcl command), add this command to a .tcl file and add that file as a pre-hook for the write_bitstream step for the implementation run.

当使用 Vivado 的运行基础架构(例如,

launch_runsTcl 命令)时,需将此命令添加到一个.tcl文件中,并将该文件作为实现运行的write_bitstream步骤的前置钩子。Problem ports:

有问题的端口:RXN_IN[3:0], RXP_IN[3:0], TXN_OUT[3:0], and TXP_OUT[3:0].

换句话说,有问题的引脚有 16 个,分别为:

RXN_IN0、RXN_IN1、RXN_IN2、RXN_IN3

RXP_IN0、RXP_IN1、RXP_IN2、RXP_IN3

TXN_OUT0、TXN_OUT1、TXN_OUT2、TXN_OUT3

TXP_OUT0、TXP_OUT1、TXP_OUT2、TXP_OUT3

解决方法:

- 将需要的相关命令保存到一个新的 Tcl 文件中。

- 将新生成的 Tcl 文件路径添加到

tcl.pre下。

具体操作:

打开新的 txt 文件,输入以下命令:

tcl

set_property SEVERITY {Warning} [get_drc_checks NSTD-1]

set_property SEVERITY {Warning} [get_drc_checks UCIO-1]

set_property SEVERITY {Warning} [get_drc_checks RTSTAT-1]注意:

可以根据提示写相应的命令,也可以将以上三条命令都写上。然后将此 txt 文件另存为 Tcl 文件,如命名为 test.tcl。

在 Vivado 界面中,点击 PROJECT MANAGER 下的 setting:

在弹出的界面中,找到 "project settings" 目录下的 "Bitstream",将相关路径下的新建 "test.tcl" 文件添加到 tcl.pre 参数下,然后点击 "OK" 按钮即可:

重新编译即可生成位码流。

Xilinx FPGA 相关约束,原语,函数使用及问题记录

yxiune 已于 2023-05-18 10:55:25 修改

管脚约束(Pin Constraints)

-

I/O 引脚分配

set_property PACKAGE_PIN <pi_name> [get_ports <port>] -

I/O 引脚驱动能力设置

set_property DRIVE <2 4 6 8 12 16 24> [get_ports <ports>] -

I/O 引脚电器标准设置

set_property IOSTANDARD <io standard> [get_ports <ports>] -

I/O 引脚抖动设置

set_property SLEW <SLOW|FAST> [get_ports <ports>] -

I/O 引脚上拉设置

set_property PULLUP true [get_ports <ports>] -

I/O 引脚下拉设置

set_property PULLDOWN true [get_ports <ports>] -

I/O 引脚差分设置

set_property DIFF_TERM <true> [get_ports <ports>]

时序约束(Timing Constraints)

-

时钟生成

create_clock -name <clock_name> -period <period> [get_ports <clock port>] -

输入延时

tclset_input_delay <max delay> -max -clock [get_clocks <clock>] [get_ports <ports>] set_input_delay <min delay> -min -clock [get_clocks <clock>] [get_ports <ports>] -

输出延时

set_output_delay <delay> -clock [get_clocks <clock>] [get_ports <ports>]

消除端口到寄存器之间的路径延时 :

set_property IOB TRUE [get_ports ***] // 将端口 *** 前的寄存器放在 I/O bank 内的寄存器中。

设置不相关时钟即路径 :

set_false_path -from <startpoints> -to <endpoints>

设置多周期约束 :

set_multicycle_path -from [get_pins <startpoints>] -to [get_pins <endpoints>] 2>

位置约束 :

// PLL

set_property LOC PLLE2_ADV_X*Y* [get_cells PLL路径及例化名]

// MMCM

set_property LOC MMCME2_ADV_X*Y* [get_cells MMCM路径及例化名]

// BUFG

set_property LOC BUFGCTRL_X*Y* [get_cells BUFG路径及例化名]

// BUFH

set_property LOC BUFHCE_X*Y* [get_cells BUFH路径及例化名]

// FIFO

tcl

set_property LOC OUT_FIFO_X*Y* [get_cells out_fifo路径及例化名]

set_property LOC IN_FIFO_X*Y* [get_cells in_fifo路径及例化名]防止综合后被优化 :

(* DowngradeIPIdentifiedWarnings="yes" *) 加在 module 之前。

BUFG、BUFH、BUFR、BUFIO 区别及使用:

BUFG:全局时钟网络,可以到达整个芯片的任意位置;一般芯片有 16 或 32 个。BUFH:水平区域时钟网络,可以给水平方向的相邻时钟网络使用;每个 Bank 有 12 个。BUFR:区域时钟网络,给本 IO Bank 时钟网络使用,每个 IO Bank 有 4 个。BUFIO:IO 时钟网络,一般作用于 MRCC、SRCC;专用时钟引脚;每个 IO Bank 有 4 个。

原语:

使用操作内部信号:

verilog

STARTUPE2 #(

.PROG_USR ("FALSE"), // Activate program event security feature. Requires encrypted bitstreams.

.SIM_CCLK_FREQ (0 ) // Set the Configuration Clock Frequency(ns) for simulation

) STARTUPE2_inst(

.CFGCLK (), // 1-bit output: Configuration main clock output

.CFGMCLK (), // 1-bit output: Configuration internal oscillator clock output

.EOS (), // 1-bit output: Active high output signal indicating the End Of Startup.

.PREQ (), // 1-bit output: PROGRAM request to fabric output

.CLK (0), // 1-bit input: User start-up clock input

.GSR (0), // 1-bit input: Global Set/Reset input (GSR cannot be used for the port name)

.GTS (0), // 1-bit input: Global 3-state input (GTS cannot be used for the port name)

.KEYCLEARB (1), // 1-bit input: Clear AES Decrypter Key input from Battery-Backed RAM (BBRAM)

.PACK (1), // 1-bit input: PROGRAM acknowledge input

.USRCCLKO (flash_clk), // 1-bit input: User CCLK input

.USRCCLKTS (0), // 1-bit input: User CCLK 3-state enable input

.USRDONEO (1), // 1-bit input: User DONE pin output control

.USRDONETS (1) // 1-bit input: User DONE 3-state enable output

);

跨时钟域原语:

verilog

xpm_cdc_array_single #(

.DEST_SYNC_FF(4),

.INIT_SYNC_FF(0),

.SIM_ASSERT_CHK(0),

.SRC_INPUT_REG(1),

.WIDTH(16)

) xpm_cdc_array_single_inst (

.dest_out(),

.dest_clk(),

.src_clk(),

.src_in()

);

函数:

$fopen:打开文件$fclose:关闭文件$display:打印$fdisplay、$fwrite:写文件$fgetc、$fgets、$fscanf、$fread:读文件$fseek、$ftell:文件定位$readmemh、$readmemb:存储器加载

实例:

verilog

integer fd; // 文件描述符定义

fd = $fopen("filename", mode); // fd 为返回值,是一个 32 位的文件描述符;mode: w, a, rb, wb, ab, r+, w+, a+, rb+, wb+, ab+

$fclose(fd); // 关闭 fd 描述的文件

$display("hello this is file %d", fd); // 打印文件名为 filename 的文件描述符

$fdisplay(fd, "xxxxxxxxxxx"); // 往 fd 文件中写内容,自动换行

$fwrite(fd, "xxxxxxxxxxx"); // 往 fd 文件中写内容,不自动换行

c = $fgetc(fd); // 按字符格式将 fd 输出给 c

code = $fgets(str, fd); // 按字符连续读,放到 str,直到 str 满或一行读完

code = $fscanf(fd, format, args); // 按格式 format 将文件 fd 中数据读到 args

code = $fread(store, fd, start, count); // 按二进制数据流格式将数据从文件读到 store;start 为文件起始位置,count 为读取长度

op = $ftell(fd); // 返回当前文件指针位置

op = $fseek(fd, offset, type); // 配置指针位置;offset 为偏移量;type 为偏移类型 (0: 设置到偏移位置;1: 当前位置加偏移;2: 文件尾加偏移)

$readmemh("filename", mem, start_addr, finish_addr); // 按 mem 变量读文件从 start 地址到 finish 地址问题记录:

1. 约束问题

问题分析:

该项目中使用了两片 DDR,3 个 4X 的 SRIO 和 1 个 1X 的 SRIO;另外有 8 路 X1 的 SATA。其中 DDR 分别在 BANK13 和 BANK16,即图中的 X0Y2 和 X0Y5;SRIO 分别位于 BANK111、BANK112、BANK113、BANK114,即图中的 X1Y0、X1Y1、X1Y2、X1Y3。

DDR 控制器 MIG 需要一个 MMCM 和一个 PLL 进行时钟管理;SRIO 核需要一个 MMCM 进行时钟管理。该芯片只有 8 个 MMCM 和 32 个 BUFG。由于 BUFG 资源不足,因此 SRIO 核的部分局部时钟使用了 BUFH 资源。因此在布局时,MMCM 要使用就近的 MMCM 资源。

由于 X0Y2 上的 MMCM 被 DDR 占用,因此 X1Y2 上的 SRIO 只能使用远端 X0Y4 上的 MMCM。而在使用 BUFH 资源时,就会出错。

解决方法:

- 将 DDR 需要的 MMCM 和 PLL 放到 X0Y4 上。

- 将 MMCM 和 PLL 中间的 BUFH 资源也放到 X0Y4 附近。

- 将 SRIO 需要的 MMCM 资源依次分布在 X0Y0、X0Y1、X0Y2、X0Y3。

- 将 BUFH 放在对应的 X1Y0、X1Y1、X1Y2、X1Y3 处。

具体修改约束:

DDR 相关约束:

tcl

set_property LOC PLLE2_ADV_X0Y2 [get_cells -hier -filter {NAME =~ */u_ddr3_infrastructure/plle2_i}]

set_property LOC MMCME2_ADV_X0Y2 [get_cells -hier -filter {NAME =~ */u_ddr3_infrastructure/gen_mmcm.mmcm_i}]

set_property LOC BUFHCE_X0Y59 [get_cells -hier -filter {NAME =~ */u_ddr3_infrastructure//u_bufh_pll_clk3}]SRIO 相关约束:

tcl

set_property LOC MMCME2_ADV_X0Y0 [get_cells srio_ctrl_inst/u_srio_1x/SRIO_CORE_INST/srio_x1_clk_inst/srio_mmcm_inst]

set_property LOC MMCME2_ADV_X0Y1 [get_cells srio_ctrl_inst/u_srio_4x/u1_srio_4x_ctrl_1/SRIO_INST_4x/srio_clk_inst/srio_mmcm_inst]

set_property LOC MMCME2_ADV_X0Y2 [get_cells srio_ctrl_inst/u_srio_4x/u2_srio_4x_ctrl_1/SRIO_INST_4x/srio_clk_inst/srio_mmcm_inst]

set_property LOC MMCME2_ADV_X0Y3 [get_cells srio_ctrl_inst/u_srio_4x/u3_srio_4x_ctrl_1/SRIO_INST_4x/srio_clk_inst/srio_mmcm_inst]

set_property LOC BUFHCE_X1Y0 [get_cells srio_ctrl_inst/u_srio_1x/SRIO_CORE_INST/srio_x1_clk_inst/gt_clk_bufh_inst]

set_property LOC BUFHCE_X1Y1 [get_cells srio_ctrl_inst/u_srio_1x/SRIO_CORE_INST/srio_x1_clk_inst/phy_clk_bufh_inst]

set_property LOC BUFHCE_X1Y2 [get_cells srio_ctrl_inst/u_srio_1x/SRIO_CORE_INST/srio_x1_clk_inst/drpclk_bufh_inst]

set_property LOC BUFHCE_X1Y3 [get_cells srio_ctrl_inst/u_srio_1x/SRIO_CORE_INST/srio_x1_clk_inst/gt_pcs_clk_bufh_inst]

set_property LOC BUFHCE_X1Y12 [get_cells srio_ctrl_inst/u_srio_4x/u1_srio_4x_ctrl_1/SRIO_INST_4x/srio_clk_inst/BUFH_gt_clk_inst]

set_property LOC BUFHCE_X1Y13 [get_cells srio_ctrl_inst/u_srio_4x/u1_srio_4x_ctrl_1/SRIO_INST_4x/srio_clk_inst/phy_clk_bufh_inst]

set_property LOC BUFHCE_X1Y14 [get_cells srio_ctrl_inst/u_srio_4x/u1_srio_4x_ctrl_1/SRIO_INST_4x/srio_clk_inst/BUFH_drpclk_inst]

set_property LOC BUFHCE_X1Y15 [get_cells srio_ctrl_inst/u_srio_4x/u1_srio_4x_ctrl_1/SRIO_INST_4x/srio_clk_inst/BUFH_gt_pcs_clk_inst]

set_property LOC BUFHCE_X1Y24 [get_cells srio_ctrl_inst/u_srio_4x/u2_srio_4x_ctrl_1/SRIO_INST_4x/srio_clk_inst/BUFH_gt_clk_inst]

set_property LOC BUFHCE_X1Y25 [get_cells srio_ctrl_inst/u_srio_4x/u2_srio_4x_ctrl_1/SRIO_INST_4x/srio_clk_inst/phy_clk_bufh_inst]

set_property LOC BUFHCE_X1Y26 [get_cells srio_ctrl_inst/u_srio_4x/u2_srio_4x_ctrl_1/SRIO_INST_4x/srio_clk_inst/BUFH_drpclk_inst]

set_property LOC BUFHCE_X1Y27 [get_cells srio_ctrl_inst/u_srio_4x/u2_srio_4x_ctrl_1/SRIO_INST_4x/srio_clk_inst/BUFH_gt_pcs_clk_inst]

set_property LOC BUFHCE_X1Y36 [get_cells srio_ctrl_inst/u_srio_4x/u3_srio_4x_ctrl_1/SRIO_INST_4x/srio_clk_inst/BUFH_gt_clk_inst]

set_property LOC BUFHCE_X1Y37 [get_cells srio_ctrl_inst/u_srio_4x/u3_srio_4x_ctrl_1/SRIO_INST_4x/srio_clk_inst/phy_clk_bufh_inst]

set_property LOC BUFHCE_X1Y38 [get_cells srio_ctrl_inst/u_srio_4x/u3_srio_4x_ctrl_1/SRIO_INST_4x/srio_clk_inst/BUFH_drpclk_inst]

set_property LOC BUFHCE_X1Y39 [get_cells srio_ctrl_inst/u_srio_4x/u3_srio_4x_ctrl_1/SRIO_INST_4x/srio_clk_inst/BUFH_gt_pcs_clk_inst]2. ADV7931 SDI 芯片 IIC 配置时序

发现问题 :IIC 读寄存器数据时,一次对一次错。

排查问题 :用 ILA 抓取 IIC 时序,发现有时 ACK 不能正确响应。

解决问题:该芯片时序要求比较严格。读取最后一个数据之后到读取停止之间必须为一个 No ACK,否则会导致下一次读取数据出错。

3. AD LTC2141 接口逻辑问题

发现问题 :图像采集后噪点很多。

排查问题 :用示波器在板上测试,波形良好;用 ILA 发现采集到的数据毛刺很多,且存在明显的时钟与数据不对齐现象。

解决问题:硬件上没有为 LVDS 信号的时钟和数据做终端匹配电阻,逻辑代码中增加终端匹配电阻。

读懂用好 Timing Constraints 窗口

judy 在 周五, 09/16/2022 - 11:15

作者:Grace Sun,赛灵思工程师

随着设计复杂度和调用 IP 丰富度的增加,在调试时序约束的过程中,用户常常会对除顶层约束外所涉及的繁杂的时序约束感到困惑,不知如何下手。例如,XDC 文件中未指定 set_false_path,但某些路径在分析时却被忽略,如何定位这些约束的设定位置?

事实上,Vivado 集成设计环境提供了许多辅助工具来协助用户完成时序约束的分析。本文阐述了如何结合 Timing Constraints 窗口对设计中的约束进行查看及分析,希望为读者的设计调试提供一些思路和方向。

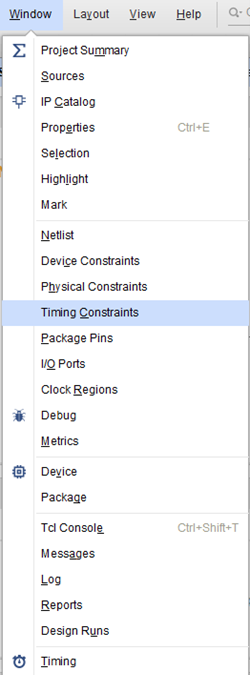

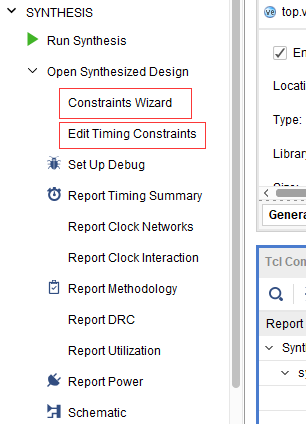

Timing Constraints 窗口的开启

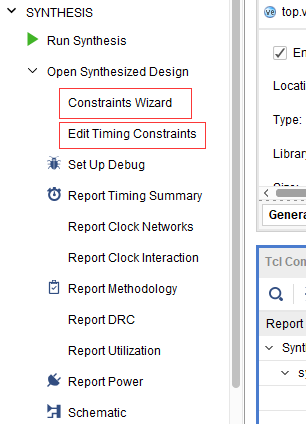

Timing Constraints 窗口仅适用于 Synthesized Design 或 Implemented Design。可通过以下三种方式之一找到其入口:

-

Open Synthesized/Implemented Design,选择菜单

Windows > Timing Constraints。

-

Open Synthesized Design,选择 Flow Navigator 中 Synthesized Design 部分的

Edit Timing Constraints。

-

Open Implemented Design,选择 Flow Navigator 中 Implemented Design 部分的

Edit Timing Constraints。

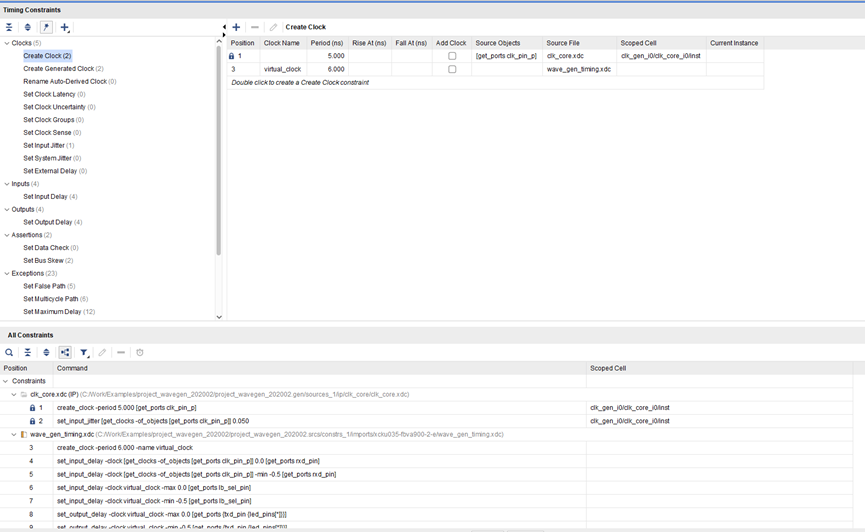

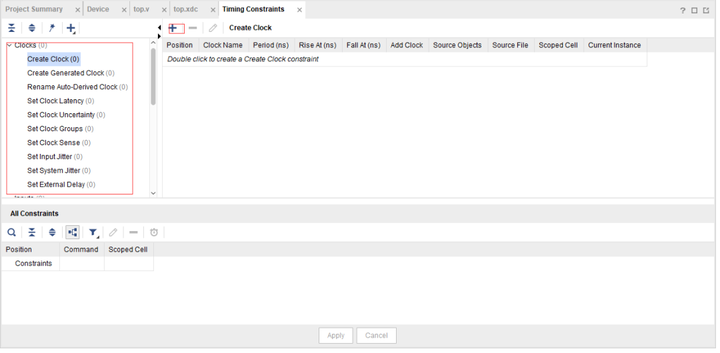

Timing Constraints 窗口一览

Timing Constraints 窗口可以以图示的方式直观显示当前导入的设计中所存储的时序约束,并以分类组织的架构呈现,用户可以方便地定位约束的创建顺序及来源。

打开后的窗口整体如下图所示:

左上部分子窗口将约束进行了分类,括号内显示的是每一类约束的数量。

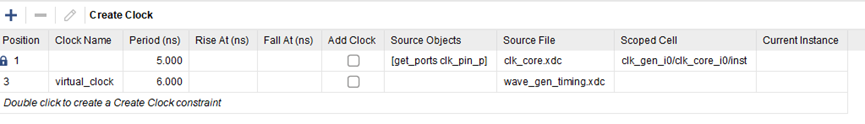

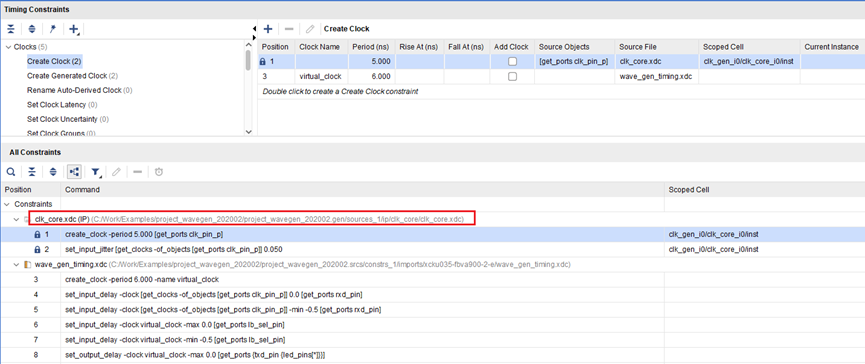

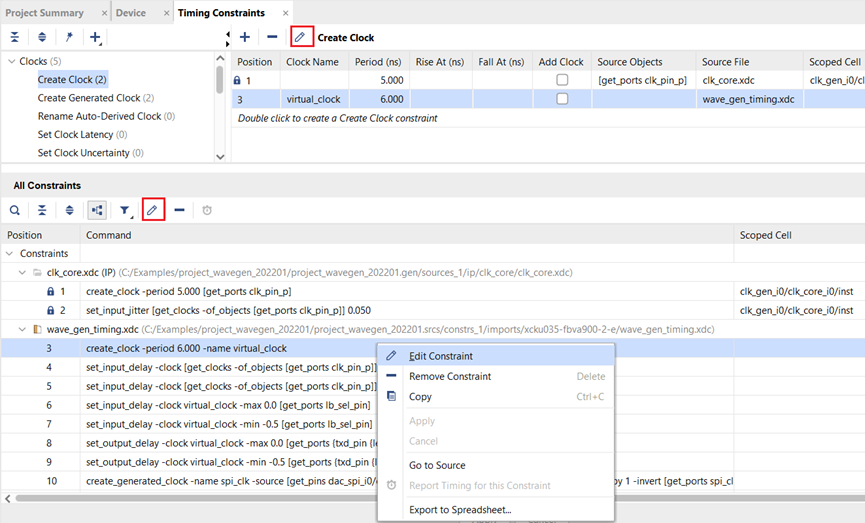

当选定某一类约束后,设计中所有这类约束信息会以电子表格的形式显示在右上部分子窗口。以 Create Clock 约束为例:

- Position 列:显示约束的位置信息,与约束的读入顺序对应。前面带锁图标表明此约束无法在表格上直接编辑,通常是 IP 自带的约束。

- Source File 列:显示约束来源于哪个 XDC 文件或 Tcl 文件。

- Scoped Cell 列:显示约束的作用范围,是全局还是某一个实例,通常此列显示的名称对应于自带特定约束的 IP 实例名。

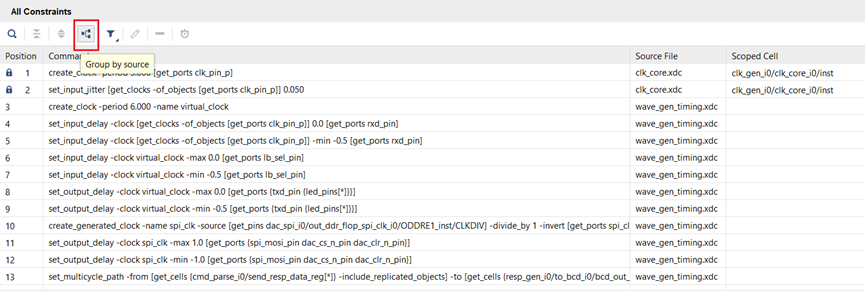

当点击某一行选中约束后,同时在下方的 All Constraints 子窗口会高亮此约束语句:

用户可以快速看到原始约束语句以及其来源 XDC 的具体文件位置。All Constraints 子窗口显示加载到内存中的约束的完整列表,其顺序与应用它们的顺序相同。约束根据它们所源自的 XDC 文件或 Tcl 脚本进行分组,根据查看需要可切换多种视图。

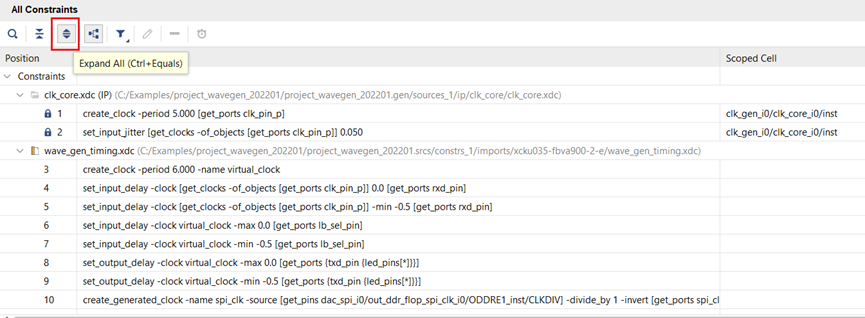

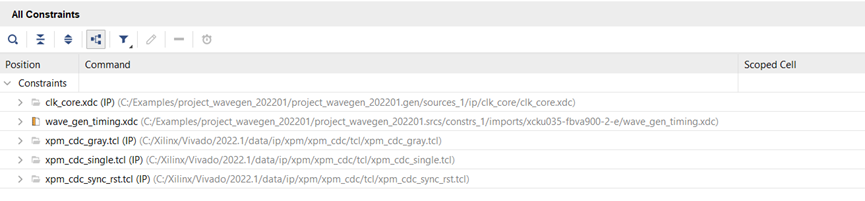

用户可以点击 expand 或 collapse 图标展开或折叠每个约束文件的约束,如下图所示:

-

展开约束:

-

折叠约束:

此时点击 Constraints 旁的箭头可以看到所有关联的约束文件,进一步可以点击某个约束文件旁的箭头进行逐一查看。

用户也可以取消选择 Group by Source 图标,将视图切换到一个表格,按序显示设计中的所有时序约束,其中 source constraint 文件和 Scoped Cell 信息显示在右侧的两列中。

在 Timing Constraints 窗口进行约束编辑

除了在表格中查看已有约束外,还可以对已有约束进行删减、修改或者添加新的约束,改动结果也会实时反映在下方的 All Constraints 窗口中并应用在当前的 in-memory 设计中,方便用户在不重新跑综合实现的前提下进行多角度的时序分析试验。

-

删除约束 :可以从任一子窗口选中此约束,右键选择

Remove Constraint,或者点击-图标,并点击窗口下方的Apply按键以刷新内存中的约束。

-

编辑约束 (注意只能修改非只读,即约束前没有带锁标志的):选中此约束,右键选择

Edit Constraint,或者点击编辑图标。在随后打开的约束编辑对话框中完成修改,并点击窗口下方的Apply按键以刷新内存中的约束。

-

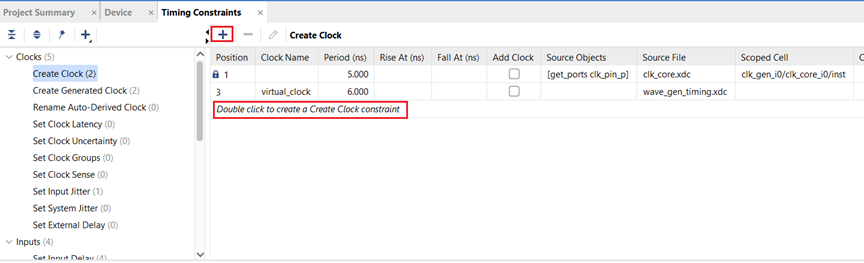

添加新的约束 :可以点击分类表格子窗口的

+图标,或者在某一类约束的空白处双击,在随后打开的对话框中将约束信息补充完整。也可以在 Tcl Console 中敲入新的约束进行添加。新约束会出现在名为 的组中的列表末尾。

约束修改后可以直接在 in-memory 设计上生效,由此展开更新后的时序分析,在当前布局布线的结果上评估修改后的时序。

评估完成后,如果需要保存所作的修改,可以在 Close Design 时选择 Save Constraints,工具会自动选择标记为 Target 的 XDC 文件进行保存。如果不想改动原始约束或者不需要保存全部改动,可以在退出设计时忽略 Save Constraints,之后再手动修改设计中的约束文件,加入想要的改动。

总结

以上内容对 Vivado IDE 中的 Timing Constraints 窗口进行了介绍。与 write_xdc 命令相比,其最大的优势是能直观显示设计中所有约束的分组及来源,为时序约束的查看、验证及假设分析提供了比较方便的接口。结合其他调试手段,可以提升设计效率。

Vivado 使用技巧:使用时序约束向导

FPGA Designer 于 2018-09-21 23:22:39 发布

时序约束向导

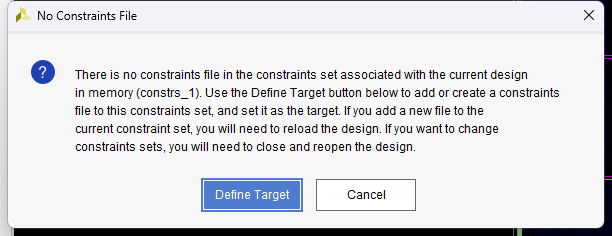

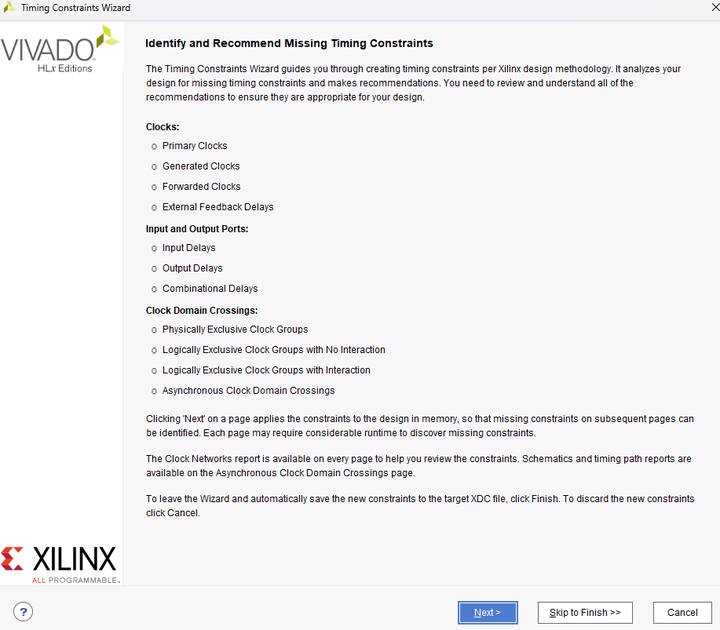

打开综合设计或实现设计后,在 Flow Navigator 中点击 Open Synthesized/Implemented Design 目录下的 Constraints Wizard 可以打开时序约束向导(会要求选择一个 target 约束文件)。弹出如下窗口:

利用该向导可以快速完成时序约束。时序约束向导会分析网表、时钟网络的连接和已存在的时序约束,并给出一些缺少的时序约束的建议。时序约束向导的前 11 页按照 3 个目录给出不同种类的时序约束,下表给出一个大致介绍:

| 时钟 | 描述 |

|---|---|

| Primary clocks | 通常指通过输入端口进入设计的时钟 |

| Generated clocks | 由主时钟产生的时钟,如 MMCM/PLL 输出的时钟 |

| Forwarded clocks | 定义在输出端口上的内部时钟 |

| External feedback delays | FPGA 输入和输出端口之间的板级延时 |

| 输入与输出端口 | |

| Input delays | 描述输入信号与参考时钟之间的相对相位 |

| Output delays | 描述输出信号与参考时钟之间的相对相位 |

| Combinatorial delays | 没有经过任何时序单元,直接穿过 FPGA 的路径 |

| 时钟域交叉 | |

| Physically exclusive clock groups | 指不会在设计中同时存在的物理互斥时钟 |

| Logically exclusive clock groups with no interaction | 这部分时钟在共享时钟树之外,彼此之间没有逻辑路径时,它们在逻辑上是互斥的 |

| Logically exclusive clock groups with interaction | 这部分时钟彼此之间有逻辑路径时,只有限定在共享时钟树部分的时钟在逻辑上才是互斥的 |

| Asynchronous clock domain crossings | 指在不具有明确相位关系的两个时钟之间传输数据,称为异步时钟域交叉 |

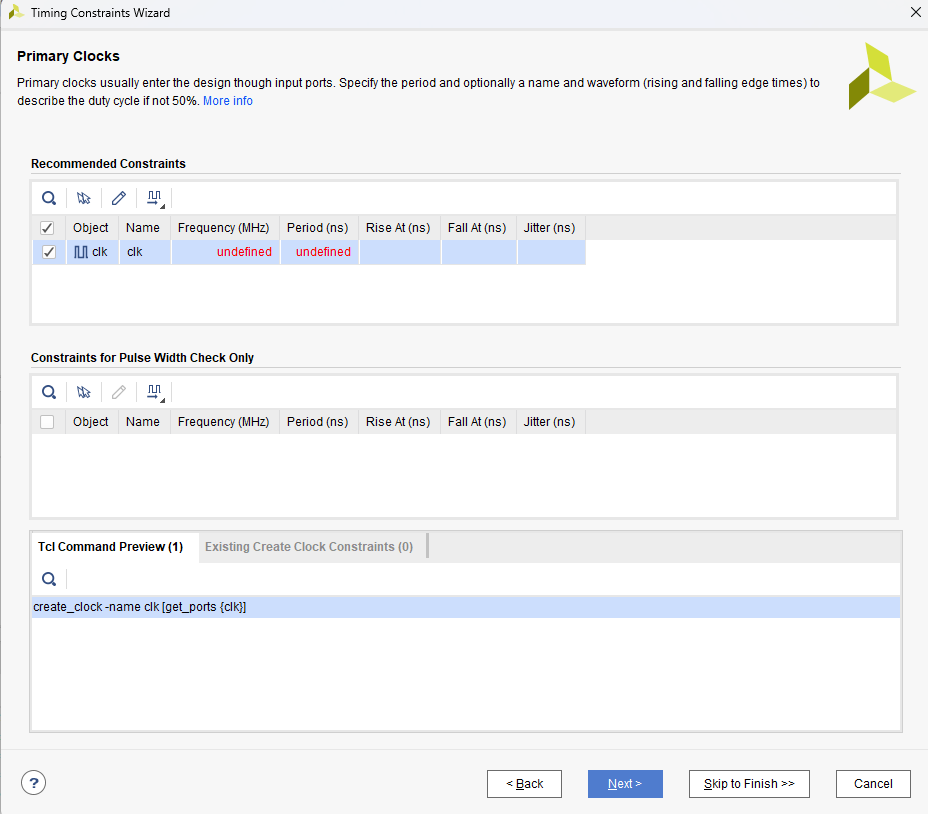

上述每一步都可以根据约束向导的建议进行约束。如果不想约束某个对象,取消勾选对象前的复选框即可。如果取消勾选了某条建议,则后续步骤中的一些缺少的时序约束可能不会被检测出来。例如,跳过了创建主时钟的步骤,约束向导便不会识别出与此时钟相关的时序约束。

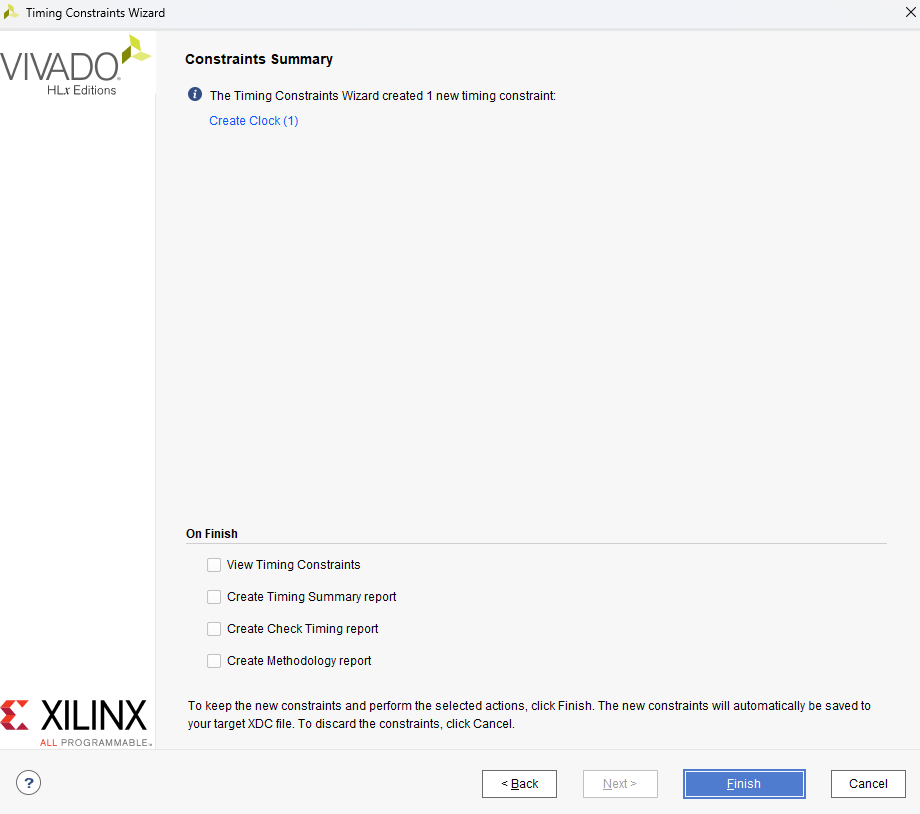

最后是一个 Summary 界面,给出了前面创建的所有约束,可以点击查看约束的详细信息。退出约束向导后,在时序约束窗口中也可以看到新约束。点击 Finish 结束约束向导时,还可以勾选如下选项创建相应报告:

- Create Timing Summary report:报告在新约束条件下的时序裕量。如果设置的周期或 I/O 延迟约束太过苛刻,会出现时序违背情况。

- Create Check Timing report:识别出不恰当或缺少的约束。

- Create DRC Report using only Timing Checks:运行时序相关 DRC 检查。

时序约束向导不会推荐可能引入不安全时序分析的约束,也不会修复当前设计导入内存时已经存在的不恰当约束。因此,如果使用向导之后,运行时序检查或 DRC 检查时仍然存在一些时序问题,通常是由源 XDC 文件中已经存在的约束问题引起的。设计者需要自行解决这些问题,而不是依赖约束向导。

在向导中编辑约束

如上文所述,可以通过对象前的复选框选择是否创建该约束,该功能也可以通过选择对象 -> 右键 -> Create Constraint 或 Do Not Create Constraint 实现。如下图所示:

缺少的值显示为红色的 undefined ,如上图中的 Frequency 和 Period ,双击可以设置值。如果希望同时编辑多个约束,则选中所有约束相同的行,点击 Edit Selected Rows 按钮,在弹出的窗口中同时编辑所有对象的约束值:

使用 Back 和 Next 可以在不同的约束界面之间切换,但如果没有处理当前界面的所有缺少的值,则无法切换到下一个约束界面。再次强调,时钟约束向导无法编辑已经存在的时序约束,只会创建新的约束。

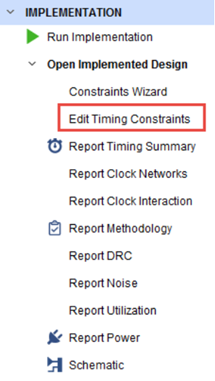

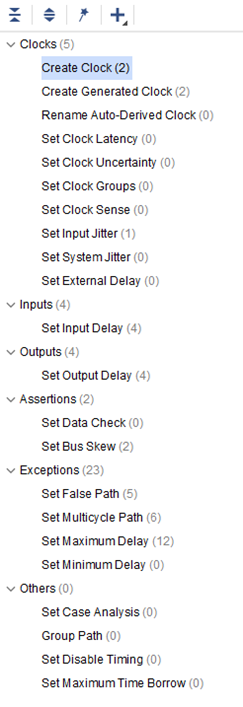

时序约束窗口

如果想要编辑已经存在的约束,在 Elaborated 设计阶段,只能通过修改 XDC 文件实现;而在综合设计或实现设计阶段,还可以通过时序约束窗口来实现。在 Flow Navigator 中点击 Open Synthesized/Implemented Design 目录下的 Edit Timing Constraints 可以打开时序约束窗口:

时序约束窗口下方的 All Constraints 按照 XDC 文件和 Tcl 脚本中的顺序,或者在 Tcl 控制台中输入约束的顺序显示时序约束。如果某些约束不能在该窗口中编辑,则会标记为 No Edit 状态,前面有一个 ? 图标。

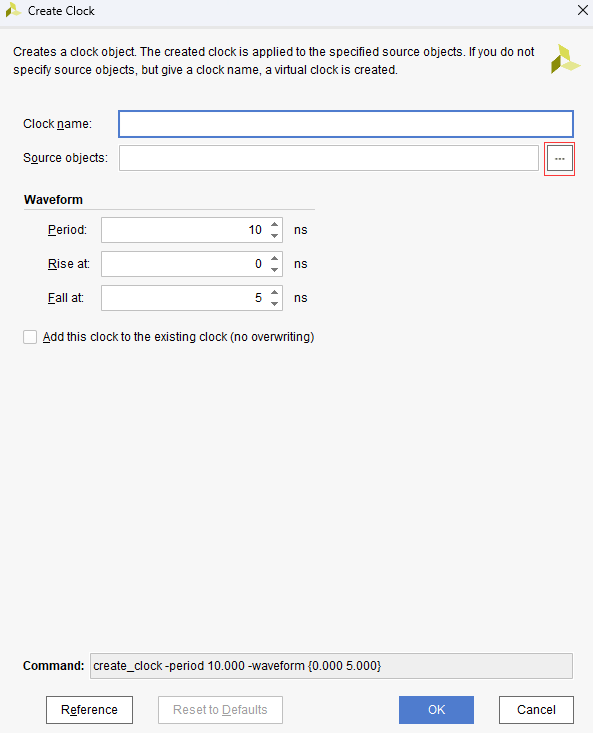

时序约束窗口中显示了所有存在约束的详细信息,并且可以直接编辑。左边以目录的形式列出了各种约束类型。右边双击最后一行可以创建当前所选类型的一个新约束,弹出窗口中完善约束信息。点击 OK 即可将约束在内存中应用,但只有点击 Save Constraints 后才会保存到 XDC 文件中。例如,创建一个新的时钟约束,弹出窗口如下:

另外,IP 核约束是无法编辑或删除的。如果需要进行此类操作,可以禁用 IP 核发布的约束文件,将其中的内容复制粘贴到用户 XDC 中,即可进行编辑操作。

FPGA 时序约束 -- 实战篇(Vivado 添加时序约束)

FPGA 入门到精通 于 2023-06-18 14:28:46 发布

前面几篇文章已经详细介绍了 FPGA 时序约束基础知识以及常用的时序约束命令,相信大家已经基本掌握了时序约束的方法。本文将介绍如何在 Vivado 中添加时序约束。Vivado 添加约束的方法有 3 种:XDC 文件、时序约束向导(Constraints Wizard)、时序约束编辑器(Edit Timing Constraints)。

一、XDC 文件

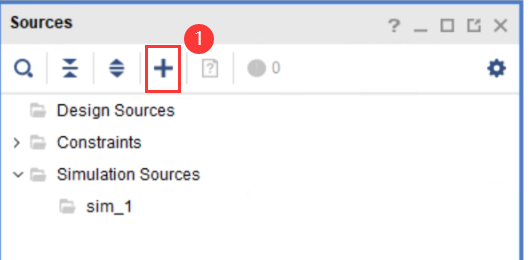

使用 Vivado 的 Source 文件管理器 直接创建新的 XDC 文件或者添加已有的 XDC 文件。具体步骤如下:

-

点击 "+" :

-

选择 "Add or create constraints" ,点击 "next" :

-

如果是添加文件,则点击 "Add Files" ;如果是新建文件,则点击 "Create File" :

-

如果是新建文件,则输入文件名,点击 "OK" ,再点击 "Finish" 即可:

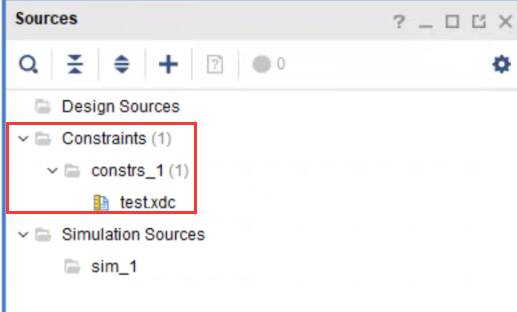

完成上述步骤后,可以在 source 界面中的 "Constraints" 中看到新建的文件:

双击打开新建的 XDC 文件,写入约束语句即可。创建 XDC 文件的方式很灵活,但在添加约束时需要谨慎,因为错误的约束可能导致电路出错或性能下降。

二、时序约束向导(Constraints Wizard)

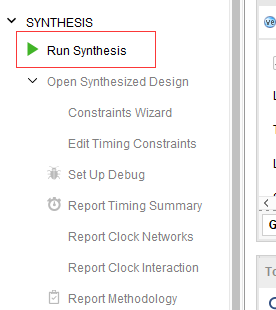

时序约束向导是 Vivado 提供的一个交互式添加约束工具,可以帮助用户通过简单的设置界面自动生成 XDC 文件中的 TIMING 约束。具体步骤如下:

-

将 HDL 代码综合:

-

点击 Vivado 左边导航栏的 "Synthesis" 中的 "Constraints Wizard" :

-

如果未创建 XDC 文件,Vivado 会提示新建 XDC 文件:

-

进入时序约束向导界面。时序约束向导按照主时钟约束、衍生时钟约束、输入延迟约束、输出延迟约束、时序例外约束、异步时钟约束等顺序依次创建时钟约束:

点击下一步,这里只演示填入主时钟,输入时钟周期,点击 "skip to finish" :

-

最后点击 "finish",生成的约束会自动保存到 XDC 文件中。

三、时序约束编辑器(Edit Timing Constraints)

时序约束编辑器是 Vivado 中提供的可视化界面,用于修改编辑 XDC 文件中的时序约束。用户可以通过这个界面添加/删除约束、调整约束优先级及修改约束属性。具体步骤如下:

-

将 HDL 代码综合完后,点击 Vivado 左边导航栏的 "Synthesis" 中的 "Edit Timing Constraints" :

-

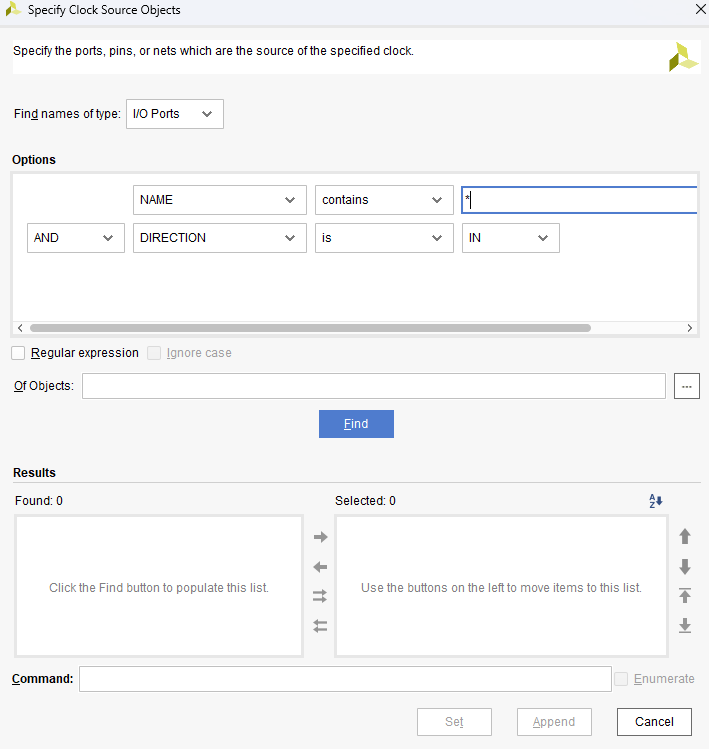

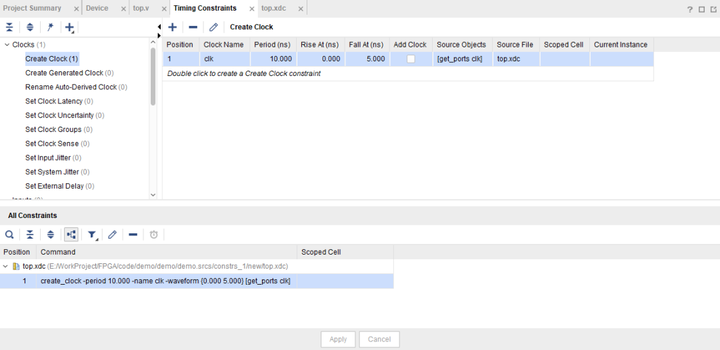

弹出编辑界面,如下图所示。先在左侧选择时序约束类型,再点击右侧窗口的 "+" 号,开始添加时序约束命令:

-

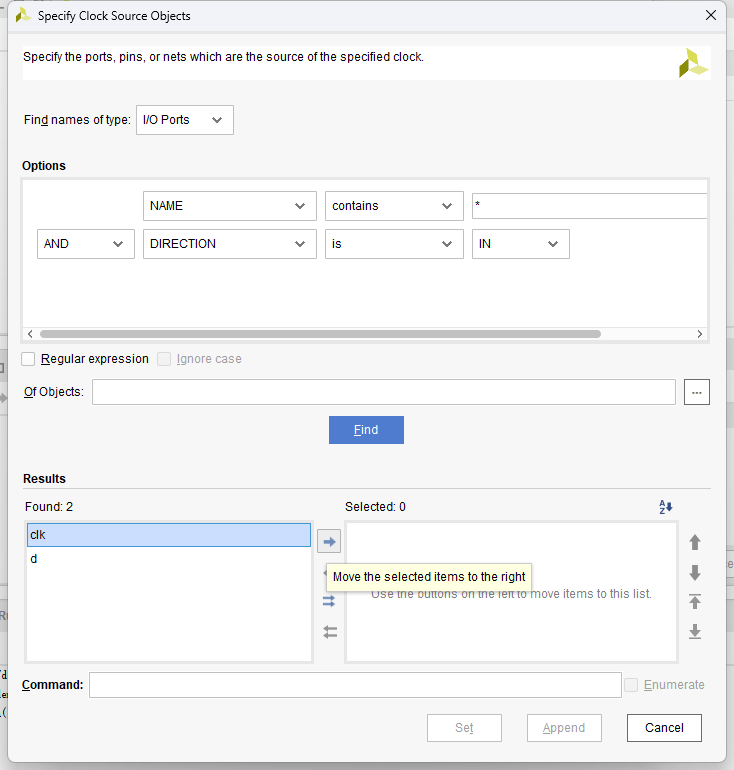

点击红框中的 "..." ,打开搜索端口界面,再点击 "find" 按钮,自动弹出搜索到的端口号:

-

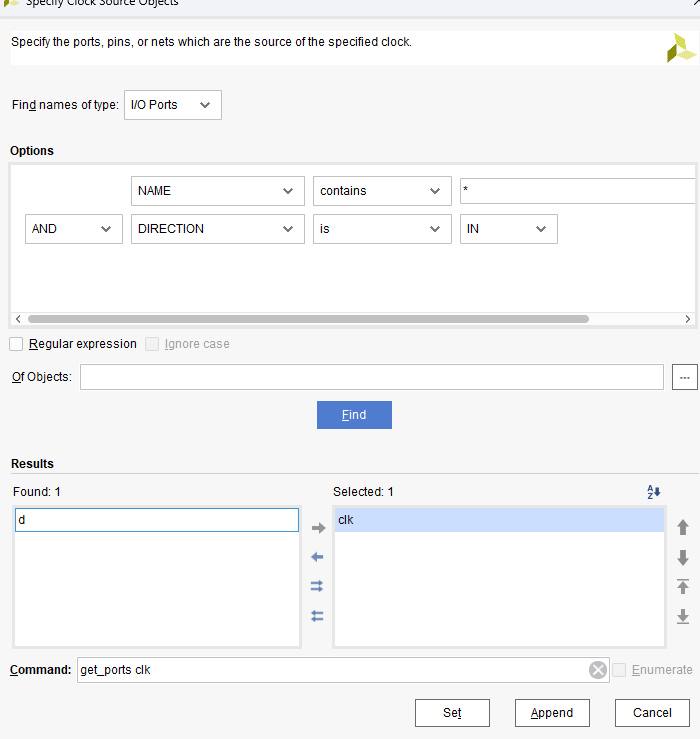

选中需要添加约束的端口(如 "clk" ),点击右侧箭头,移动到 "选中窗口" ,再点击 "set" 按钮:

-

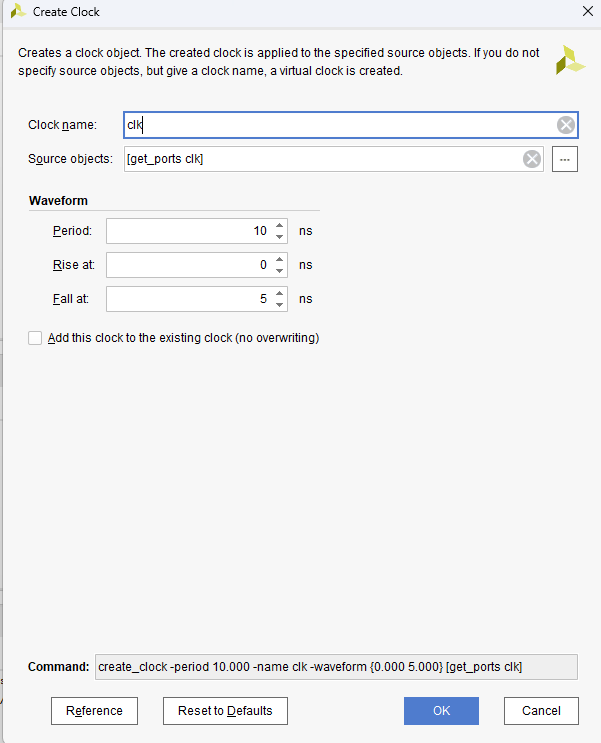

输入约束端口名,并设置时钟周期和占空比,点击 "OK" :

-

按 "Ctrl+S" 快捷键保存,最下方的预览窗口会显示设置的时钟约束,并且会自动保存到 XDC 约束文件中:

与直接编辑 XDC 文件相比,时序约束编辑器提供了时序约束的详细分类和说明,更容易理解和使用。

四、总结

本文分享了 Vivado 中常用的添加时序约束的方法,读者可以根据自己的习惯和喜好选择合适的方式。

讨论:建立时间和保持时间不满足如何解决

歪枣树 发表于 2011-12-8 23:21:46

回答一

-

建立时间违规(setup violation) :

主要解决思路是削减关键路径(critical path)的延迟。可采用以下方法:

- 进行流水线(pipeline)处理。

- 进行重定时(retiming)操作。

- 对组合逻辑在前后级之间进行适当调整。

-

保持时间违规(hold time violation) :

保持时间违规通常由时钟树的偏移(clock tree skew)导致。主要解决原则是增加前一级组合逻辑的延迟,例如添加缓冲器(buffer)。当保持时间不满足要求时,需使前一级的延迟足够大,至少比时钟周期(clock period)多出一个保持时间。此外,也可适当缩短时钟周期。然而,保持时间并非完全可控,处理起来较为棘手。

在综合过程中,建立时间违规是由前级组合逻辑延迟过大造成的,因此可使用set_max_delay进行限制;保持时间违规是由于前级组合逻辑延迟过小导致的,所以不能让其过小,可使用set_min_delay进行限制。

回答二(对回答一的解析)

"建立时间违规是由于前级组合的延迟过大引起的,因此要用set_max_delay来限制;保持时间违规是由于前级组合延迟过小引起的,因此不能让它太小,要用set_min_delay来限制"这种说法有误。

这属于例外约束,并非针对路径延时的约束。它只能改变指定路径发射沿和锁存沿的关系,即会依据设置的值进行分析,但无法对延时起到约束作用。

via:

-

Xilinx FPGA 管脚 XDC 约束之:物理约束_fpga 差分信号管脚约束 - CSDN 博客

https://blog.csdn.net/gslscyx/article/details/103016237 -

vivado:解读 xdc 约束文件 - CSDN 博客

https://blog.csdn.net/m0_46830519/article/details/125166256 -

vivado 进行管脚约束(详细教程)-CSDN 博客

https://blog.csdn.net/weixin_62432906/article/details/130873178 -

FPGA 管脚约束之电平标准_fpga 引脚电平标准 - CSDN 博客

https://blog.csdn.net/dalingertong/article/details/134419844 -

Xilinx FPGA 未使用管脚的默认电平设置方法_vivado 不用的引脚 默认电平 - CSDN 博客

https://blog.csdn.net/qsj_csdn/article/details/115354286 -

Vivado Error 问题之 [DRC NSTD-1] 问题解决 - CSDN 博客

https://blog.csdn.net/m0_37779673/article/details/121054991 -

vivado 约束未使用引脚_vivado 不用引脚悬空 - CSDN 博客

https://blog.csdn.net/crjmail/article/details/118516731 -

VIVADO 中关于管脚约束错误的一种解决方法_vivado 引脚约束 - CSDN 博客

https://blog.csdn.net/csdnqiang/article/details/105786227 -

Xilinx FPGA 相关约束,原语,函数使用及问题记录_xilinx 约束 - CSDN 博客

https://blog.csdn.net/weixin_41838250/article/details/115491737 -

读懂用好Timing Constraints窗口 | FPGA 开发圈

https://fpga.eetrend.com/content/2022/100563988.html -

Vivado 使用技巧:使用时序约束向导_[timing 38-313] there are no user specified timing-CSDN 博客

https://blog.csdn.net/FPGADesigner/article/details/82808420 -

FPGA 时序约束 -- 实战篇(Vivado 添加时序约束)-CSDN 博客

https://blog.csdn.net/mengzaishenqiu/article/details/131271202 -

FPGA 设计中常见的时序问题及解决方法!_fpga 时序违例怎样改 - CSDN 博客

https://blog.csdn.net/weixin_49780322/article/details/143307156 -

建立时间和保持时间不满足如何解决 - 数字IC设计讨论(IC前端|FPGA|ASIC) - EETOP 创芯网论坛 (原名:电子顶级开发网) -

https://bbs.eetop.cn/forum.php?mod=viewthread&tid=315737&page=1

-

Xilinx FPGA programming skills of common timing constraints detailed - FPGA Technology

https://www.fpgakey.com/technology/details/xilinx-fpga-programming-skills-of-common-timing-constraints-detailed