- Ad9268芯片

AD9268是一款双通道、16位、80 MSPS/105 MSPS/125 MSPS模数转换器(ADC)。AD9268旨在支持要求高性能、低成本、小尺寸和多功能的通信应用。双通道ADC内核采用多级差分流水线架构,集成输出纠错逻辑。每个ADC都具有宽带宽、差分采样保持模拟输入放大器,支持各种用户可选的输入范围。集成基准电压源简化了设计考虑。占空比稳定器用于补偿ADC时钟占空比的变化,使转换器保持出色的性能。ADC输出数据可以直接路由至两个外部16位输出端口。这些输出可以设置为1.8 V CMOS或LVDS。有灵活的关断选项可以显著省电。设置和控制编程利用三线式SPI兼容型串行接口完成。

AD9643管脚与AD9268相同,故一般都兼容设计。AD9643的最高采样率为250Msps,分辨率为14bit。

2.调试环境

使用UD LAN-402信号处理模块,软件配置如下:

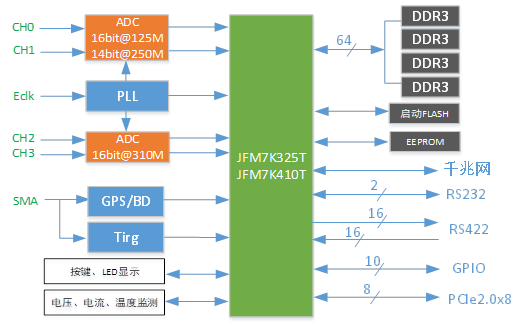

硬件框图如下:

硬件框图如下:

LAN-402的主要特点是支持4通道A/D(可以分别用于短波、超短波和雷达),对外支持16路双向差分RS422接口(可用作波控),也有千兆网和PCIe2.0x8接口,fpga可以完成信号处理任务。

3.调试过程

AD9268对外的接口支持LVDS接口、CMOS接口两种模式,通过SPI可以配置芯片使用哪种接口、是否开启测试模式等等。

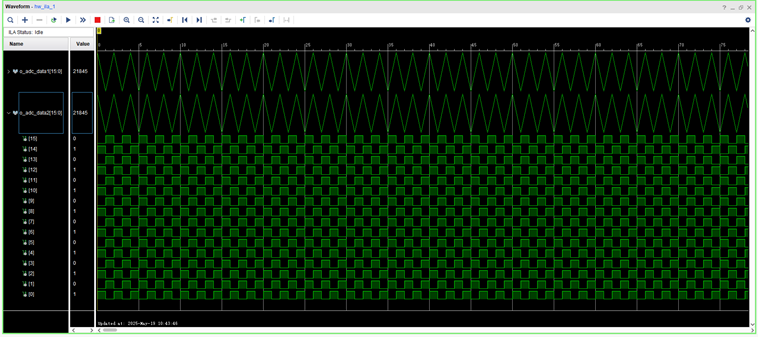

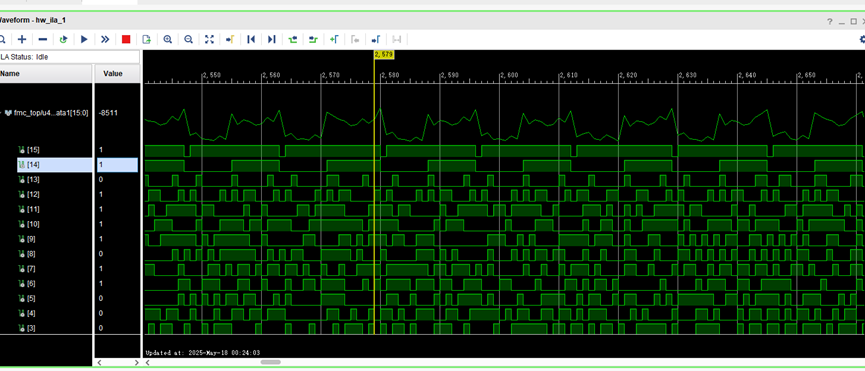

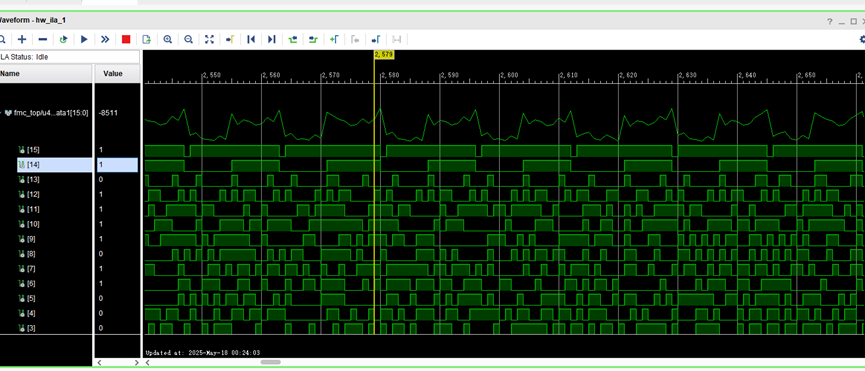

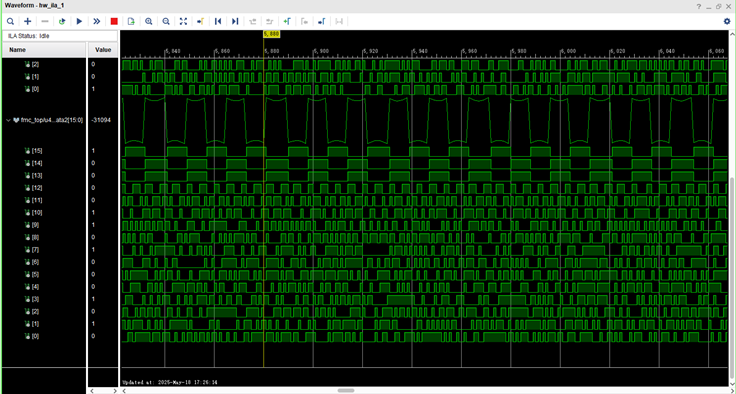

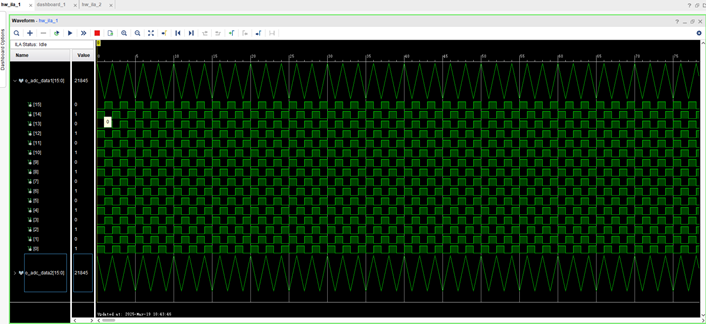

调试中时,可以先通过SPI对ADC芯片进行配置为累加数测试模式(用于测试硬件连接是否正常),效果如下:

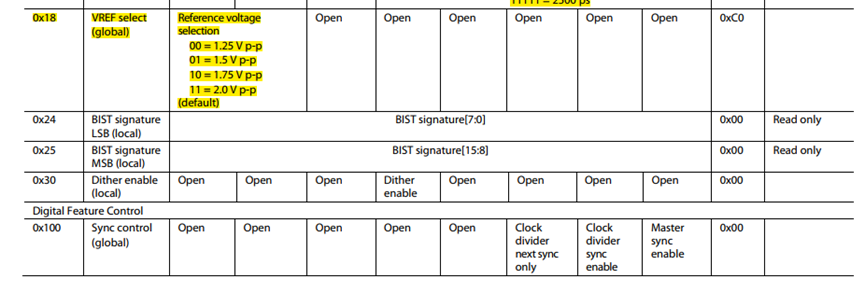

再配置为PN码测试模式,用于校验相位和测误码,效果如下:

4.调试遇到的问题

4.调试遇到的问题

-

- 调试时遇到的问题记录

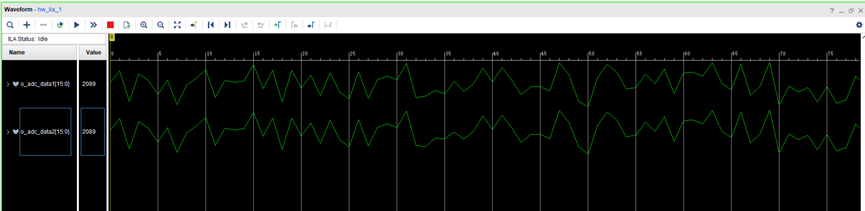

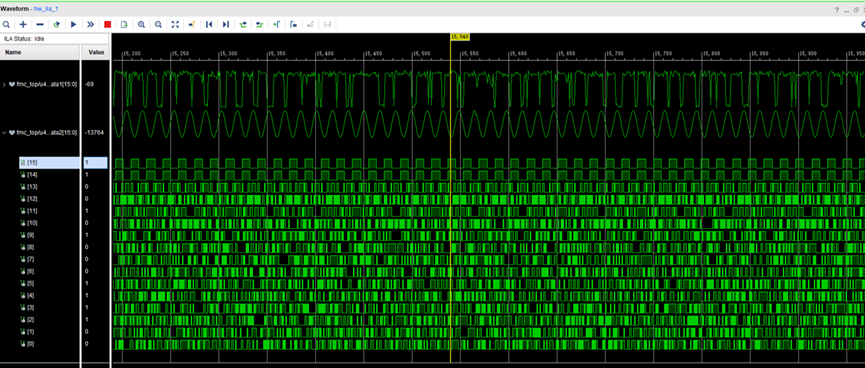

- 通道1的ADC数据无法呈现正常的正弦波脉络,表现如下

- 调试时遇到的问题记录

-

-

-

- 分析猜测1:可能是通道1和2数据隔离没做好,导致ADC数据混合

-

-

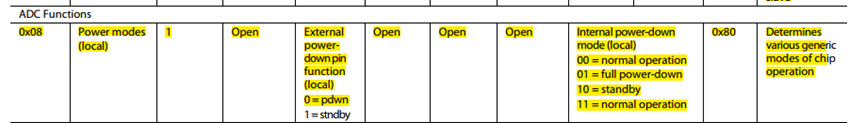

尝试测试与实验:配置寄存器将通道2设置未完全断电模式:

结果仍然不正确:

-

-

-

- 分析猜测2:ADC寄存器配置错误,导致ADC数据输出有

- 分析猜测2:ADC寄存器配置错误,导致ADC数据输出有

-

-

1;尝试修改数据输出格式:

二进制补码:

偏移二进制

结果仍不正确

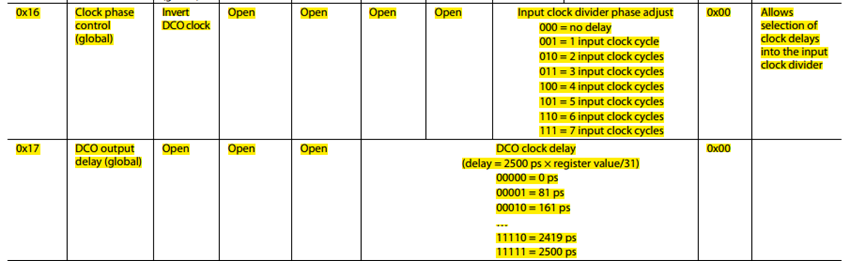

2;尝试配置输入输出延时

3;打开deither_enable

4;测试寄存器配置表

配置完成后,表现变好;但仍然不正确

-

-

-

- 分析猜测3:ADC数据输出后在FPGA内部DDR采样时出问题

-

-

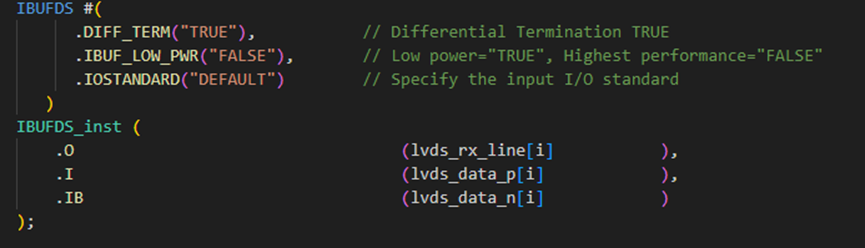

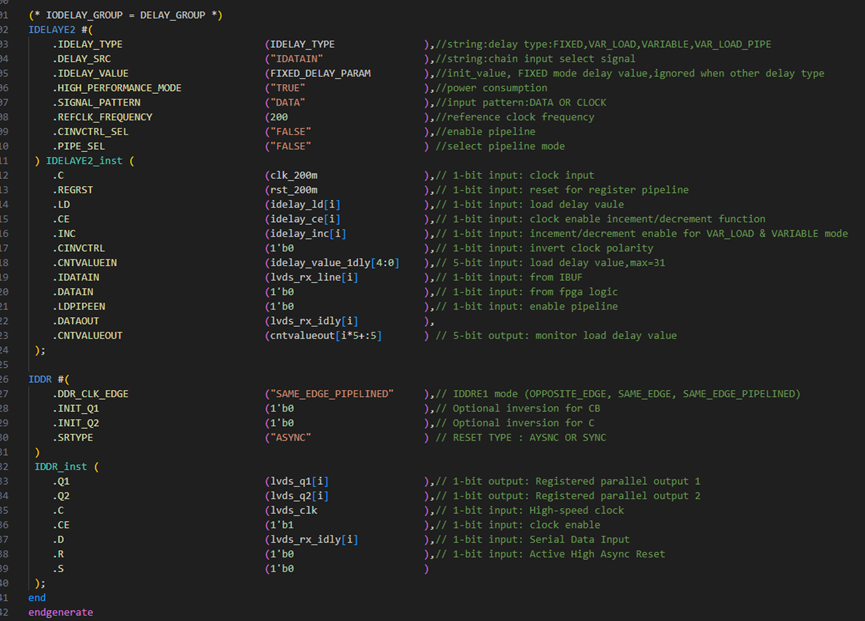

将DDR采样时 差分终结设置为TRUE,设置为高性能表现模式。

-

-

-

- 分析猜测4:ADC数据输出后在FPGA内部DDR采样时时钟未对齐(延迟)

-

-

给DDR的数据线的时钟添加延时

-

-

-

- 分析猜测5:ADC芯片未焊接好,导致LVDS模式下P/N某个脚无数据

-

-

1;在FPGA内部将ADC数据输出的电平约束改为LVCMOS,发现通道2数据完全正确,但通道1仍不正确

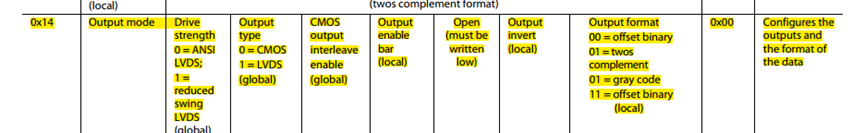

2;在使用FPGA内部测试模式,输出一个累加数据,发现ADC芯片通道1的bit15,13,12一直没有数据,通道2正确

-

-

-

- 最终问题定位为ADC芯片通道1的15,13,12三个管脚未焊接好

-

-

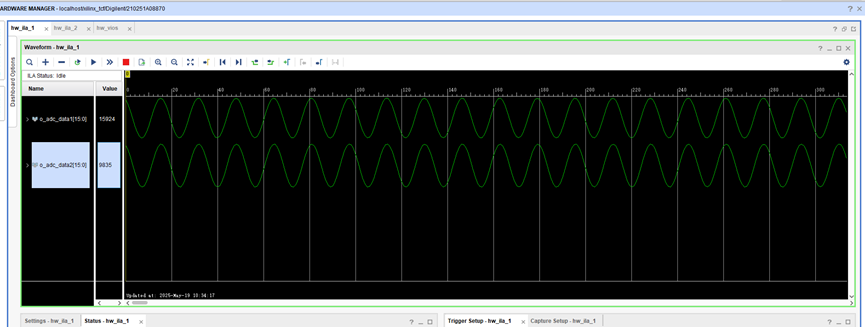

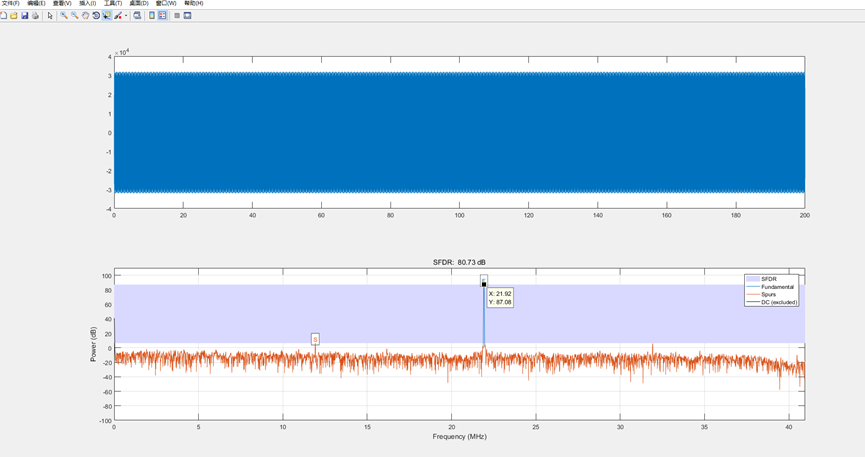

再次焊接后,输入70MHz中频,双通道最终数据采集结果与环境记录。

数据导入matlab,查看频谱图,分析信噪比:

以上频谱可以看出,输入70MHz中频时,有两个杂散,导致SFDR才80.73dB,还没有达到datasheet的性能指标,还需要继续调试。

这两个杂散分布为主信号的左右两侧,且对称,频率为10MHz。模块中,使用10MHz的晶振给PLL供时钟,应该是这个10MHz泄露产生的。今天没时间来调试了,请关注后续文章,来解决此问题的记录。