Chapter.1 AXI4总线协议

作者:齐花Guyc(CAUC)

一、总线介绍

AXI4总线

AXI4总线就像是SoC内部的"高速公路",负责在不同硬件模块之间高效传输数据。

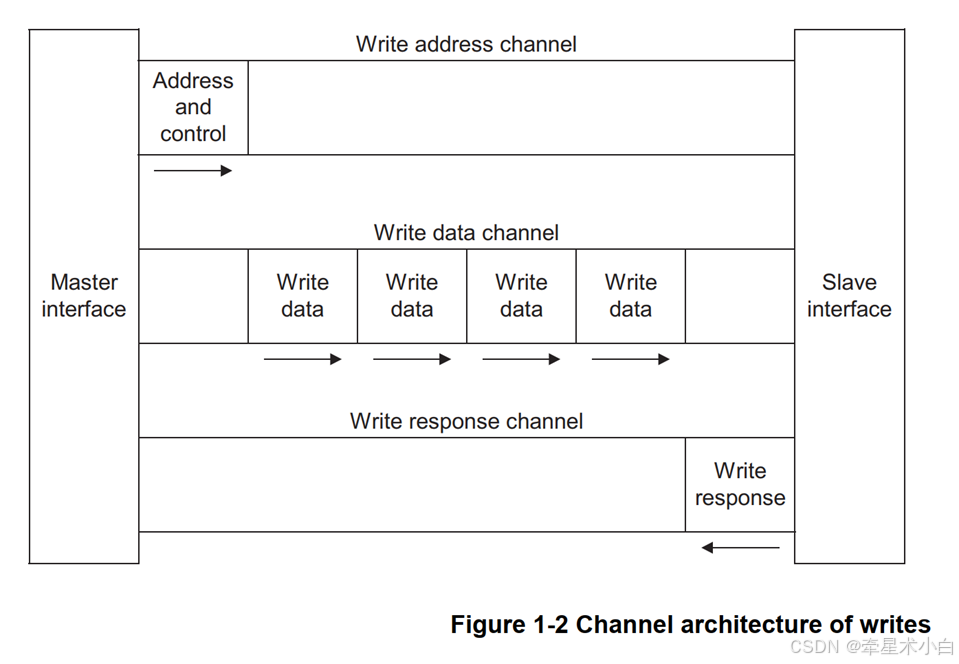

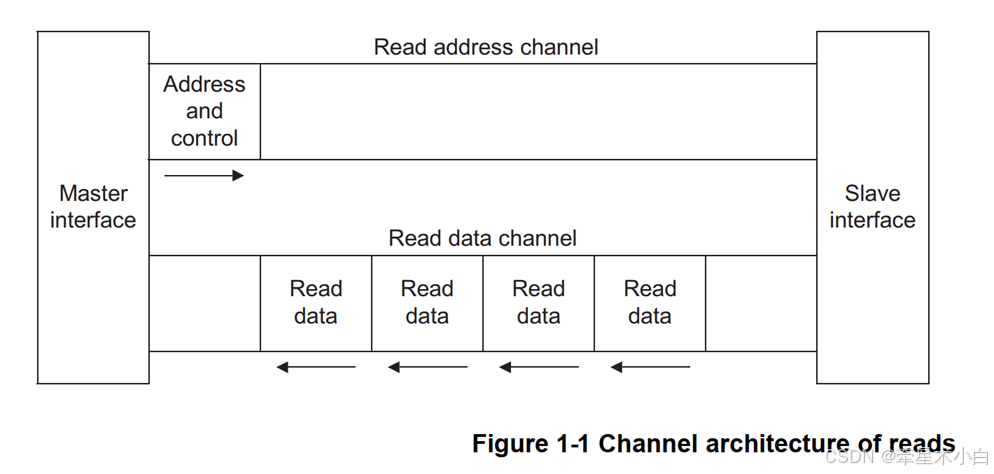

AXI4协议通过 5个独立通道 传输数据和控制信号,每个通道都有自己的信号线,互不干扰。

-

写地址通道(Write Address Channel, AW)

主设备(Master)告诉从设备(Slave)要写入数据的地址和相关信息(如突发长度、数据大小等)。

信号:

AWVALID:主设备表示写地址有效。

AWREADY:从设备表示准备好接收写地址。

AWADDR:写操作的目标地址。

AWLEN:突发长度(0表示1次传输,1表示2次,依次类推,最多255)。

AWSIZE:每次传输的字节数(如2表示4字节)。

AWBURST:突发类型(固定、递增、环绕)。

-

写数据通道(Write Data Channel, W)

主设备通过这个通道将数据发送到从设备。

信号:

WVALID:主设备表示写数据有效。

WREADY:从设备表示准备好接收数据。

WDATA:写数据内容。

WSTRB:字节选通信号,指示哪些字节有效。

WLAST:表示当前数据是突发传输的最后一个。

-

写响应通道(Write Response Channel, B)

从设备告诉主设备写操作是否成功。

信号:

BVALID:从设备表示写响应有效。

BREADY:主设备表示准备好接收响应。

BRESP:响应状态(如OKAY、ERROR)。

-

读地址通道(Read Address Channel, AR)

主设备告诉从设备要读取数据的地址和相关信息。

信号:

ARVALID:主设备表示读地址有效。

ARREADY:从设备表示准备好接收读地址。

ARADDR、 ARLEN、 ARSIZE、 ARBURST:类似写地址通道。

-

读数据通道(Read Data Channel, R)

从设备将读取的数据返回给主设备。

信号:

RVALID:从设备表示读数据有效。

RREADY:主设备表示准备好接收数据。

RDATA:读数据内容。

RRESP:响应状态。

RLAST:表示当前数据是突发传输的最后一个。

AXI4总线时序

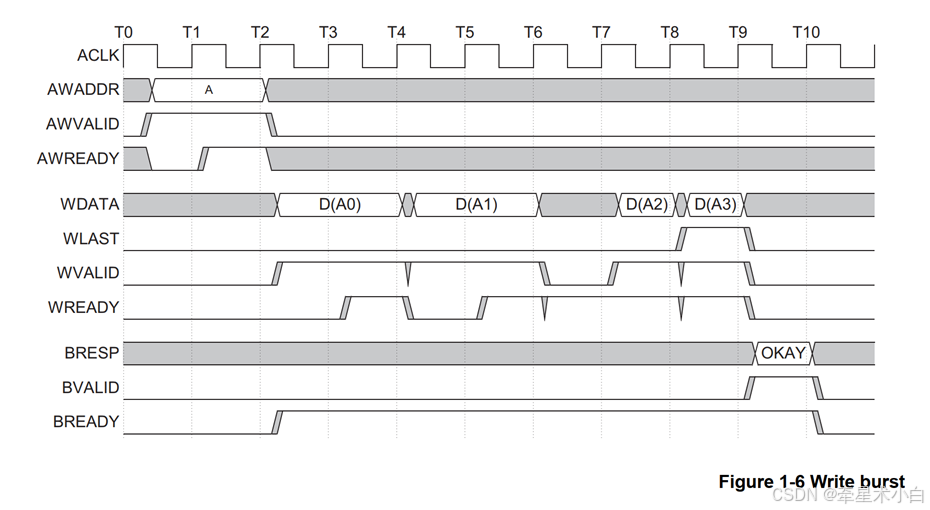

1.AXI4写操作时序

突发写操作(burst write),一次写操作传输4个数据 [D(A0)、D(A1)、D(A2)、D(A3)]

AXI4写操作使用3个通道:

- 写地址通道(AW):AWADDR、AWVALID、AWREADY

- 写数据通道(W):WDATA、WLAST、WVALID、WREADY

- 写响应通道(B):BRESP、BVALID、BREADY

2.时序图信号解读

时钟(ACLK)

ACLK 是一个周期性的时钟信号,从T0到T10,每周期一个上升沿,用于同步所有信号。

写地址通道(AW)

AWADDR:在T1到T2,主设备(Master)设置写地址为 A,表示目标地址。地址信号在 AWVALID 有效期间保持不变。

AWVALID:在T1,主设备将 AWVALID 置高,表示写地址有效。一直保持高电平直到T2,因为地址传输完成。

AWREADY:在T2,从设备(Slave)将 AWREADY 置高,表示准备好接收地址。

握手:在T2的时钟上升沿,AWVALID 和 AWREADY 同时为高,地址传输完成。

握手机制 :

VALID:由发送端(主设备或从设备)置高,表示数据或地址有效。

READY:由接收端置高,表示准备好接收数据或地址。

数据传输只有在 VALID 和 READY 同时为高 时才会发生。

写数据通道(W)

WDATA:从T3到T8,主设备依次发送4个数据:D(A0)、D(A1)、D(A2)、D(A3)。每个数据在一个时钟周期内传输。

WLAST:在T8,发送最后一个数据 D(A3) 时,主设备将 WLAST 置高,表示这是突发传输的最后一个数据。

WVALID:从T3到T8,主设备将 WVALID 置高,表示数据有效。每次数据传输都需要 WVALID 和 WREADY 同时为高。

WREADY:从T3到T4,从设备将 WREADY 置高,表示准备好接收数据。但在T5,WREADY 变低,表示从设备暂时未准备好(可能是处理延迟)。在T6到T8,WREADY 再次变高,继续接收数据。

握手:在T3、T4、T6、T7、T8的时钟上升沿,WVALID 和 WREADY 同时为高,数据传输完成。

写响应通道(B)

BRESP:在T9,从设备设置响应状态为 OKAY,表示写操作成功。

BVALID:在T9,从设备将 BVALID 置高,表示响应有效。

BREADY:在T2到T9,主设备将 BREADY 置高,表示准备好接收响应。

握手:在T9的时钟上升沿,BVALID 和 BREADY 同时为高,响应传输完成。

写操作流程

- 写地址传输(T1-T2):

主设备发送地址 A(通过 AWADDR),并通过 AWVALID 和 AWREADY 握手完成地址传输。 - 写数据传输(T3-T8):

主设备发送4个数据 D(A0) 到 D(A3)。

数据传输在T3、T4、T6、T7、T8完成(因为T5时 WREADY 为低,数据传输暂停了一个周期)。

在最后一个数据 D(A3) 时,WLAST 置高,表示突发传输结束。 - 写响应(T9):

从设备返回 OKAY 响应,表示写操作成功。

通过 BVALID 和 BREADY 握手完成响应传输。

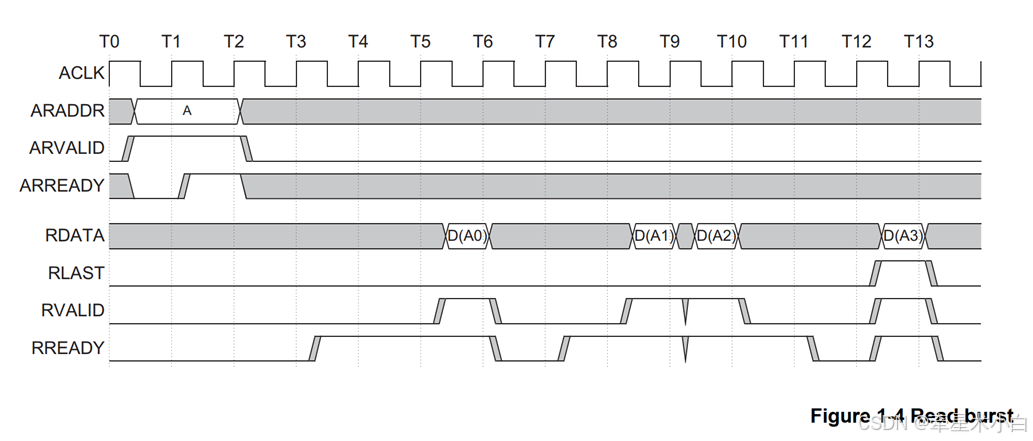

2.AXI4读操作时序

突发读操作(burst length=4),主设备(Master)请求4个连续的数据。

AXI4读操作使用2个通道:

读地址通道(AR):ARADDR、ARVALID、ARREADY

读数据通道(R):RDATA、RLAST、RVALID、RREADY

2.时序图信号解读

时钟(ACLK)

ACLK 是一个周期性的时钟信号,从T0到T13,每周期一个上升沿,用于同步所有信号。

读地址通道(AR)

ARADDR:在T1到T2,主设备设置读地址为 A,表示起始读取地址。地址信号在 ARVALID 有效期间保持不变。

ARVALID:在T1,主设备将 ARVALID 置高,表示读地址有效。一直保持高电平直到T2,因为地址传输完成。

ARREADY:在T2,从设备将 ARREADY 置高,表示准备好接收读地址。

握手:在T2的时钟上升沿,ARVALID 和 ARREADY 同时为高,地址传输完成。

读数据通道(R)

RDATA:从T6到T13,从设备依次返回4个数据:D(A0)、D(A1)、D(A2)、D(A3)。每个数据在一个时钟周期内传输。

RLAST:在T13,发送最后一个数据 D(A3) 时,从设备将 RLAST 置高,表示这是突发传输的最后一个数据。

RVALID:从T6到T13,从设备将 RVALID 置高,表示数据有效。每次数据传输都需要 RVALID 和 RREADY 同时为高。

RREADY:从T4到T6,主设备将 RREADY 置高,表示准备好接收数据。在T7,RREADY 变低,表示主设备暂时未准备好(可能是处理延迟)。在T8到T11,RREADY 再次变高,继续接收数据。在T12,RREADY 变低。在T13,RREADY 再次变高。

握手:RVALID 和 RREADY 同时为高,数据传输完成。

读操作流程

- 读地址传输(T1-T2):

主设备发送地址 A(通过 ARADDR),并通过 ARVALID 和 ARREADY 握手完成地址传输。 - 读数据传输(T4-T13):

从设备在T6到T13返回4个数据 D(A0) 到 D(A3)。

数据传输在T6、T9、T10、T13完成。

在最后一个数据 D(A3) 时,RLAST 置高,表示突发传输结束。