一、背景说明

board to board通信的时候,两块板子通信,在正常温度下都是正常的,但是到了低温就会概率性

出现通信异常,然后温度升高又正常了,这个会是什么原因呢?这个就是边缘温度恢复的现象,接近经典低温失效机制。

二、可能出现的原因

1.冷焊、虚焊、裂纹

在比较低的温度下,材料会收缩,尤其是BGA焊接球收缩;

还有可能是焊点裂纹扩展;

PCB层之间热膨胀系数的不匹配。

2.如果固定为某一路引脚或者信号线,这个焊点存在微裂,可能在低温下完全断开或者高阻,导致信号线悬空,表现为

固定高电平。当温度升高,材料接触恢复,断点又接触上了,通信恢复;

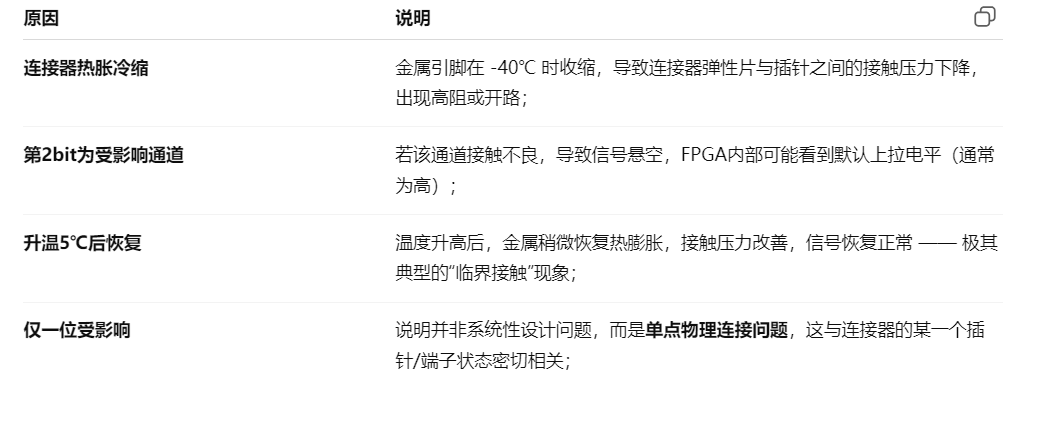

三、现象表征

这种现象典型表现为:

在某一特定极端温度出现问题;

升高或降低几度后又恢复;

一般是单 bit 出问题;

一样的代码、配置、逻辑,在温度改变时出现跳变。

四、其他原因

1.IO驱动能力边缘

某个IO驱动边缘,能力或者阈值刚好在低温下发生临界变化;

该bit的上拉或者下拉太弱,在低温时候电平维持不了;

2.IO的PCB信号质量有问题

走线太长,过孔多,阻抗不匹配

低温下介质损耗,传输延迟变化,造成信号变形

这种情况是波形失真或者出现末次,不会固定为高;

3.FPGA输入IO边界效应或者时序窗口偏移

FPGA输入延迟在低温下变化,采样在不稳定区域;这种情况的

是错位或者花屏,不是固定为某种电平。