1.DMA

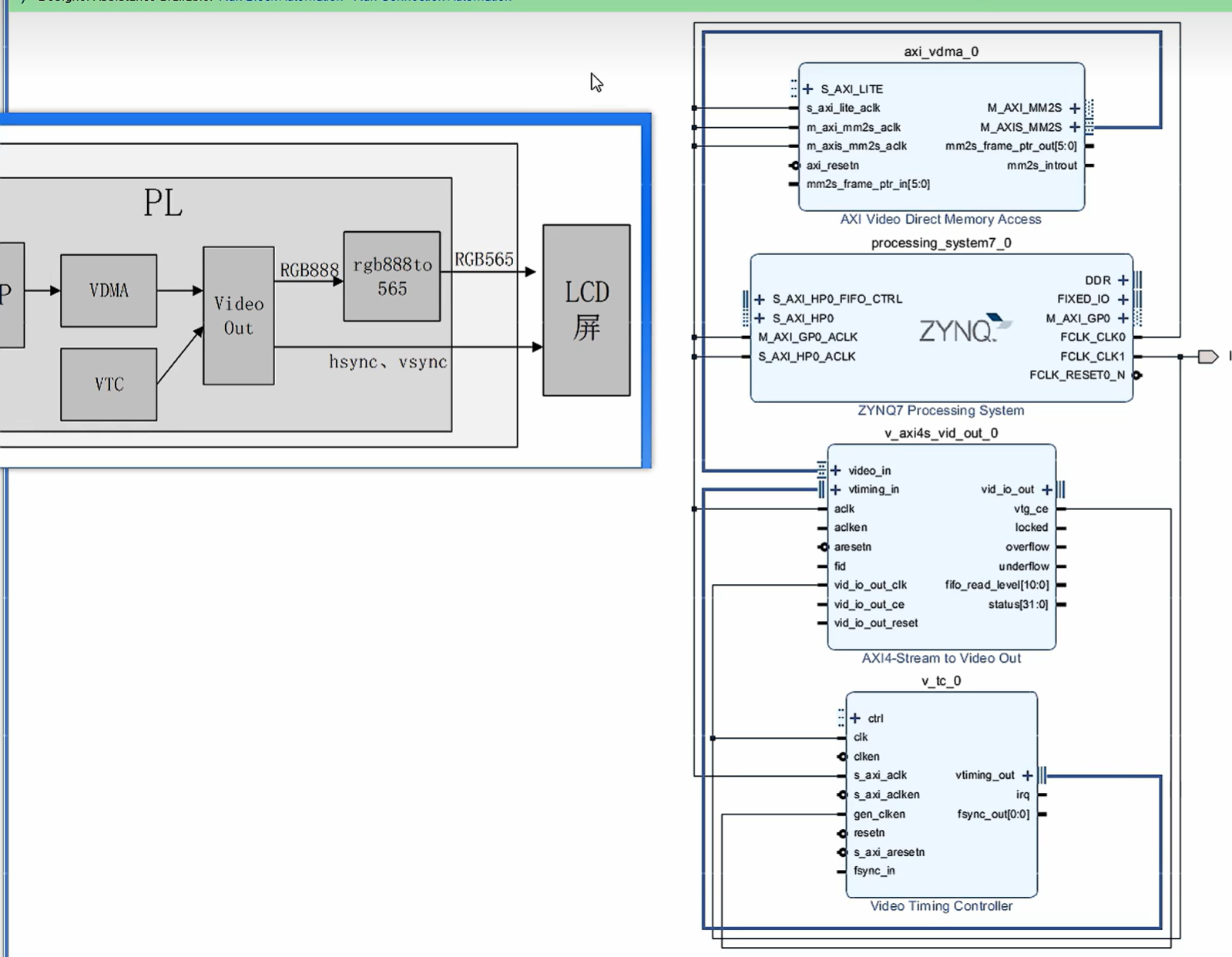

我们的整体VGA显示分为几步:比如先导入VIDEO TIMING CONTROL来做对输入数据的时序"对齐",这里开源骚客写的很详细,先用了一个虚拟IO(VIO)来作为输入,导入了一个简单的RTL模块(当VTL的使能信号有效时,RGB_DATA_OUT就接收来自VIO的RGB_DATA_IN);

接着,我们要把VIO替换掉为DMA+PS端的模块(即输入数据变成了PS端处理过后的,被DMA读取)

DMA 有两个 AXI 流端口。一个是 AXI 主流 (M_AXIS _MM2S),对应于 READ 通道。数据将通过 M_AXI_MM2S 端口从内存中读取,并发送到 M_AXIS_MM2S 端口(并发送到连接到此端口的 IP)。

以下是对VDMA的通俗解释(来自AI):

VDMA就是视频数据的"快递专车",它直接在摄像头(PL端)和内存(PS端)之间建立一条专用高速公路,让视频帧数据不经过CPU就能直达目的地。

写的很详细的教程:Tutorial: PYNQ DMA (Part 1: Hardware design) - Learn - PYNQ

另一个对DMA很通俗的解释视频:10行代码,就能让你真正理解DMA!你用的可能很少,但是在单片机中非常重要!_哔哩哔哩_bilibili

2.AXI接口之读写DDR

-

AXI4主控制器 :模块(axi4_rw)作为AXI总线的主设备,主动发起读写请求。

-

DDR访问:通过HP接口连接到Zynq(从机)的DDR控制器,实现对DDR内存的读写。

-

控制接口 :提供启动信号(

init_axi_txn)、完成标志(txn_done)和错误指示(error)。

无用户信号 :AWUSER/ARUSER/WUSER等宽度为0,简化设计。

用户信号是什么?

在AXI协议中,用户信号(如

AWUSER,ARUSER,WUSER等)是可选的扩展信号,用于在标准AXI通道中传递额外的自定义信息。它们不属于AXI核心协议规范,而是提供给设计者的"扩展槽"。------内容由AI生成

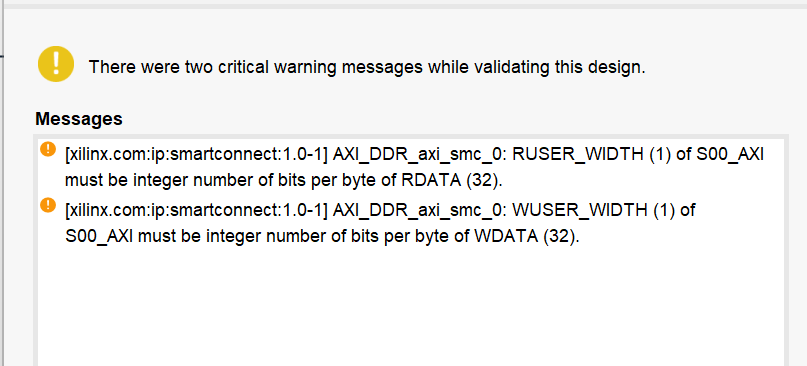

对着野火的PS文档直接复现,一个问题是警告:

你把 AXI 接口的 RUSER_WIDTH 和 WUSER_WIDTH 设成了 1 位,但这不符合 AXI 规范,因为数据总线是 32 位(4 字节),而用户信号宽度必须是"每字节整数倍"的位数。但其实这里我们根本不需要什么用户位宽,双击axi4_rw的ip把后面五个位宽全部修改成0即可解决:

所有m00_axi_*信号连接到Zynq的HP0/HP1等AXI从端口。

当外部逻辑拉高(也就是对应的按键消抖模块的flag有效),m00_axi_init_axi_txn拉高,触发模块开始读写操作。

总结:axi4_rw模块是FPGA与Zynq DDR通信的"桥梁",通过标准化AXI4协议实现高效突发传输。编写者只需触发init_axi_txn,模块自动完成地址分配、突发控制、握手响应等复杂操作,极大简化了DDR交互逻辑设计。

3.ip核配置

对于GP M口,PS端是主;对于HP ,PS端是从。

| 信号名称 | 总线类型 | 协议特点 | 典型连接对象 |

|---|---|---|---|

M_AXI_MM2S |

AXI4-Full | 存储器映射,含地址/控制信号 | DDR内存控制器 |

M_AXIS_MM2S |

AXI4-Stream | 纯数据流,无地址信号 | 流处理IP核 |

S就是Stream的缩写,表示"流式数据传输";摄像头采集的视频就是没有地址的视频流,CPU无法直接解析无地址的流数据,我们要使用VDMA;

在野火的第17个例程DMA环回读写实验中,由于数据经过DMA之后变成了数据流,与之打交道的也应该是带有 Stream 接口的高速的 AD 或 DA IP 核(比如AXI4_STREAM TO VIDEO OUT),这里我们方便起见选择了AXI4 Stream Data FIFO IP 核来充当这类 IP,这个FIFO起到 将AXI-Full 总线转换为 AXI-Stream 总线 ,并且充当一个"流数据池"的作用。其S_AXIS与DMA的M_AXIS_MM2S相连,M_AXIS与DMA的S_AXIS_S2MM相连,非常类似于正负极的连接。

AXI DMA 的 MM2S/S2MM 两个通道 → 通过 fabric 中断号 → 接到 PS 的 GIC → 由 TxIntr_Handler / RxIntr_Handler 处理完成/错误事件 → 把全局标志 Tx_Done / Rx_Done / Error 置位 → 主循环里根据标志位做后续动作。

#define RX_INTR_ID XPAR_FABRIC_AXIDMA_0_S2MM_INTROUT_VEC_ID

#define TX_INTR_ID XPAR_FABRIC_AXIDMA_0_MM2MM_INTROUT_VEC_ID

GIC给中断源分配了中断号,这两个宏就是 BSP 在 xparameters.h 里根据我们的硬件设计自动生成的;在 Vivado 里把 AXI-DMA 的 mm2s_introut / s2mm_introut 信号拉到 PS 的 IRQ_F2P[x] 引脚的那一刻,就已经决定了它的中断号;之后 Vivado 导出 HDF,SDK/Vitis 根据 HDF 生成 xparameters.h,把连线结果翻译成宏值,软件直接用即可。