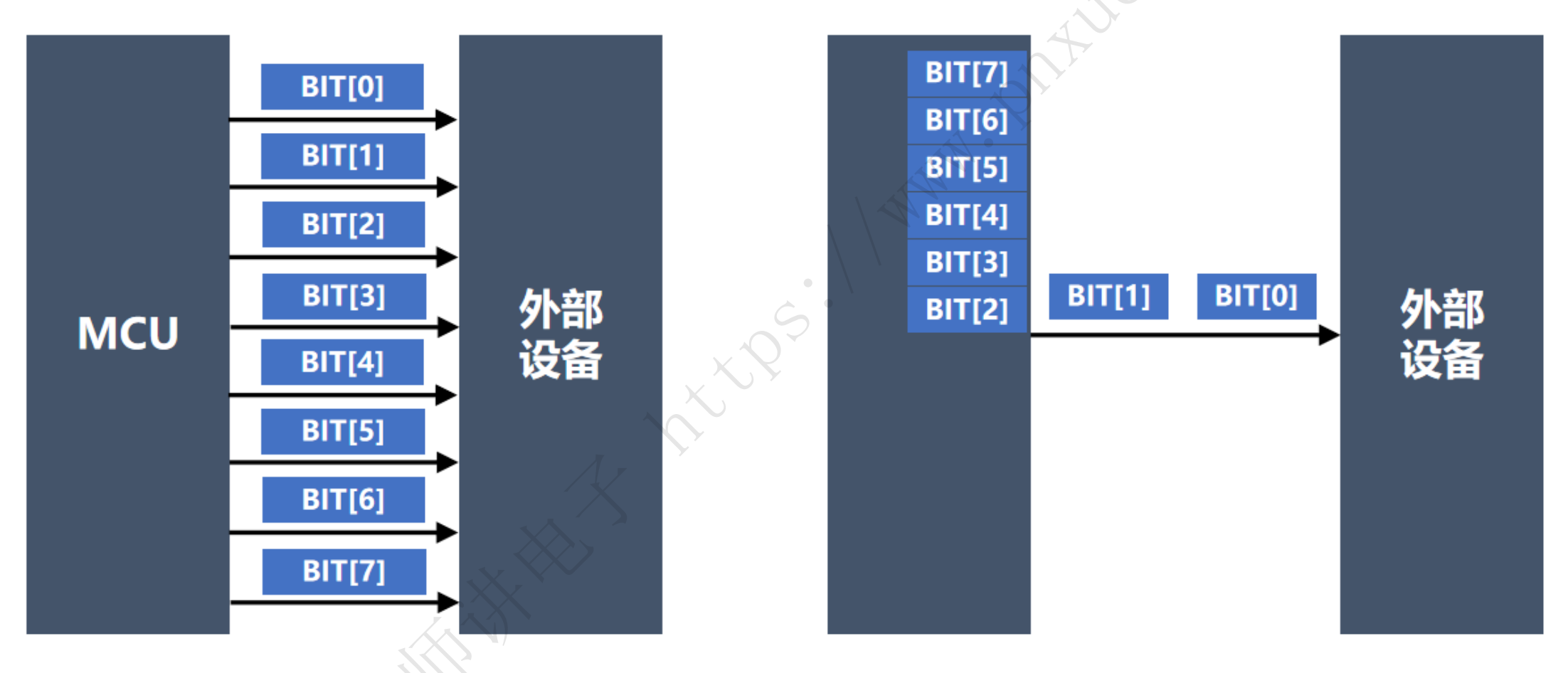

通信可分为并行通信和串行通信

1. 并行通信

核心原理

同时使用多条物理线路 传输数据的多个比特(通常8位、16位或32位)。

示例 :

8位并行通信 = 8条数据线同时传输1字节(8比特)。

特点

| 特性 | 说明 |

|---|---|

| 传输速度 | 理论速度高(多条线路并发) |

| 硬件复杂度 | 高(需多条数据线 + 控制线) |

| 抗干扰能力 | 弱(信号同步要求高,长距离易失真) |

| 成本 | 高(线缆/接口更复杂) |

| 典型应用 | 短距离高速传输: • 内存总线(DDR) • 早期打印机(LPT接口) • FPGA片内通信 |

关键问题

-

时钟偏移 (Skew) :

长距离传输时,各线路信号延迟不同,导致数据无法同时到达。

-

电磁干扰 (EMI) :

多线并行产生交叉干扰,限制频率提升。

2. 串行通信

核心原理

通过单条线路 逐比特顺序传输数据。

示例 :

传输1字节(8比特)需连续发送8个时钟周期。

特点

| 特性 | 说明 |

|---|---|

| 传输速度 | 单线速度低,但可通过高频率补偿(现代串行协议远超并行) |

| 硬件复杂度 | 低(仅需1-2条数据线 + 时钟/控制线) |

| 抗干扰能力 | 强(差分信号技术可抗干扰,适合长距离) |

| 成本 | 低(线缆/接口简化) |

| 典型应用 | 长短距离通用: • USB/PCIe/SATA • 以太网 • UART(串口) • I²C/SPI |

技术优势

-

差分信号 (LVDS) :

如USB、以太网使用

D+/D-双线抵消共模噪声。 -

内嵌时钟 :

如PCIe使用8b/10b编码将时钟信号融入数据流。

-

拓扑灵活 :

支持点对点(SATA)、总线(I²C)、环状(Token Ring)等结构。

3. 核心区别总结

| 维度 | 并行通信 | 串行通信 |

|---|---|---|

| 数据线数量 | 多条(如8/16/32线) | 1条(单端)或2条(差分) |

| 传输方式 | 多比特同时传输 | 单比特顺序传输 |

| 速度瓶颈 | 时钟偏移和干扰限制高频 | 可提升频率至GHz级 |

| 传输距离 | 短(通常<0.5米) | 长(USB可达5米,以太网100米) |

| 现代应用 | 逐渐被取代(除片内总线外) | 主流(USB4/PCIe 5.0/Thunderbolt) |

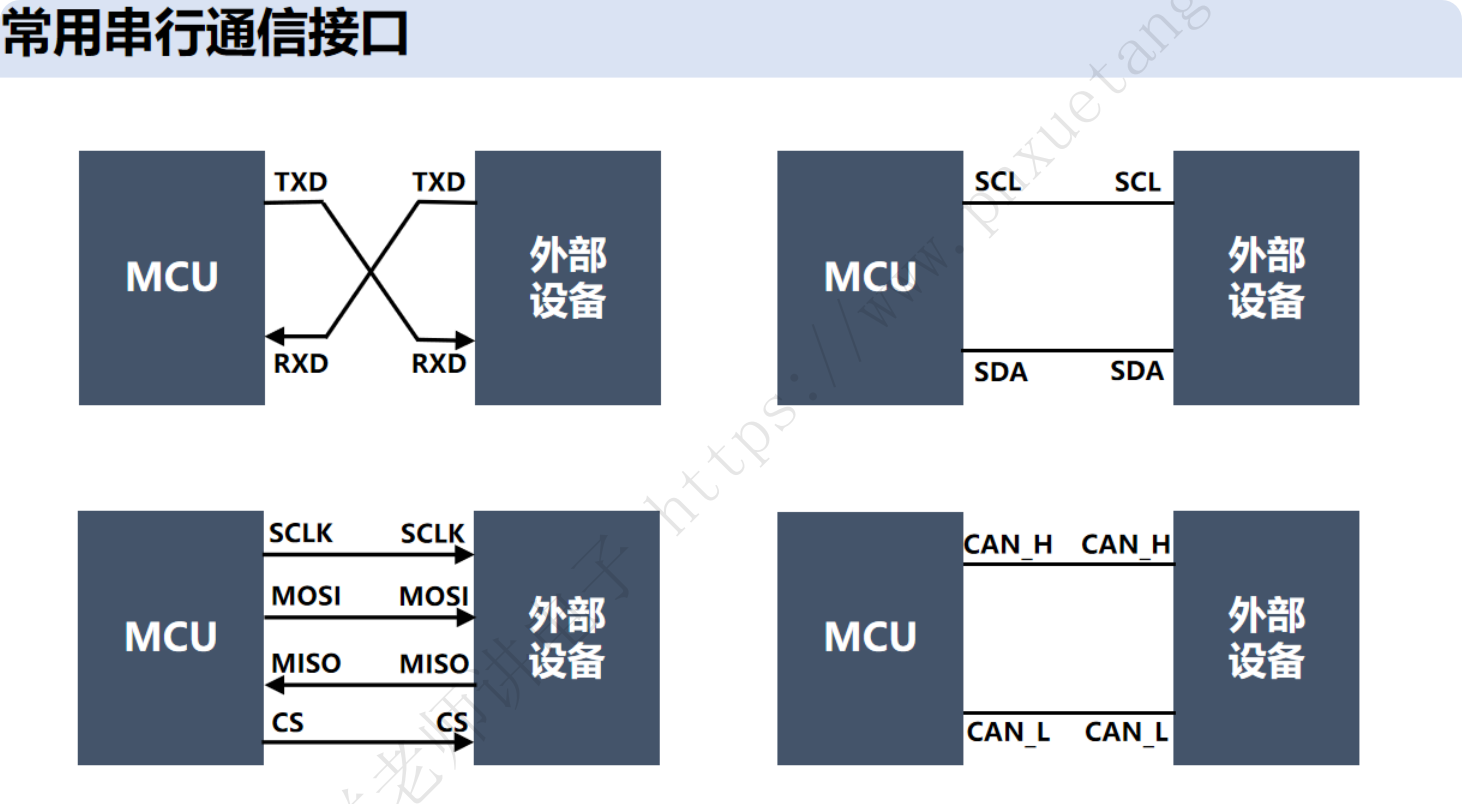

异步 :UART/USART

同步:I²C, SPI, USB, PCIe, SATA, Ethernet,CAN

平常经常说的串口,其实是串行通信中的UART接口标准(协议)

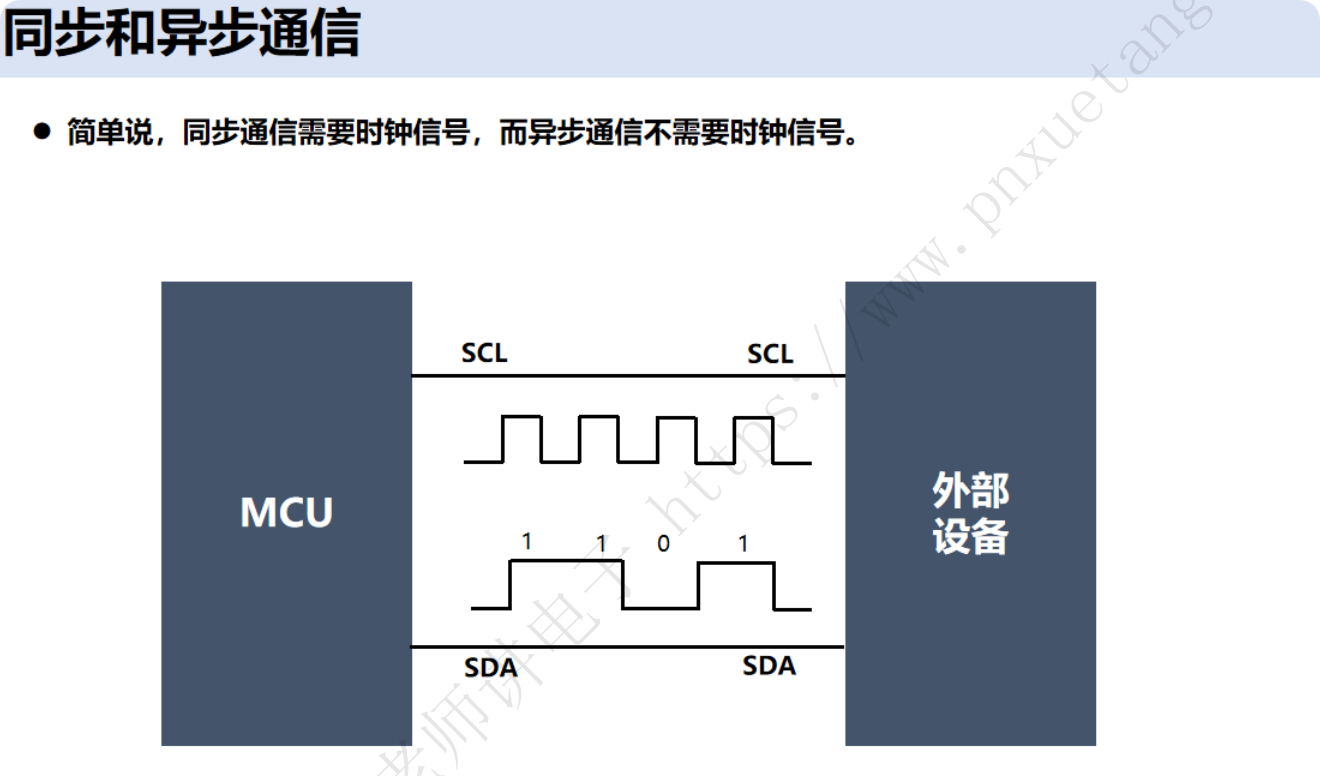

同步通信和异步通信

同步通信 (Synchronous Communication)

核心原理

收发双方使用同一时钟信号 (由主设备或独立时钟源提供),在时钟边沿(上升沿/下降沿)触发数据采样,实现精确同步。

关键特征:

-

必须有时钟线(如SCK、CLK)

-

数据以连续数据块传输(无需起止位)

-

时钟频率决定传输速率

典型协议

| 协议 | 时钟线 | 数据线 | 特点 |

|---|---|---|---|

| SPI | SCK | MOSI, MISO | 全双工,高速(可达100MHz+) |

| I²C | SCL | SDA(双向) | 半双工,地址寻址,多主从 |

| SDIO | CLK | CMD, DAT0-3 | 存储卡扩展协议 |

| PCIe | RefClk | 内嵌于数据流 | 高速差分串行,时钟恢复技术 |

优势

-

速度高:无冗余起止位,传输效率>95%

-

实时性强:时钟严格同步,适合高速场景(如传感器实时采集)

-

错误率低:时钟边沿采样抗干扰强

缺点

-

需额外时钟线(增加布线复杂度)

-

通信距离受限(时钟信号长距离易失真)

异步通信 (Asynchronous Communication)

核心原理

无共享时钟 ,收发双方依赖预定义的波特率(Baud Rate) 和数据帧格式 实现自同步。

关键特征:

-

无需时钟线

-

每字节数据添加起止位(Start/Stop Bits)

-

波特率偏差须<2%

| 协议 | 电气标准 | 应用场景 |

|---|---|---|

| UART | TTL/RS-232 | 单片机调试,模块通信 |

| RS-485 | 差分信号 | 工业总线(Modbus) |

| USB 1.x | 异步传输模式 | 早期USB设备 |

优势

-

布线简单:仅需1-2条数据线(如TX/RX)

-

距离灵活:RS-485可达千米级

-

容错性强:起始位重新同步机制

缺点

-

效率低:起止位占20-30%开销(如8N1格式效率80%)

-

速率限制:波特率通常<10Mbps(高速需过采样)

串口UART几种电气协议

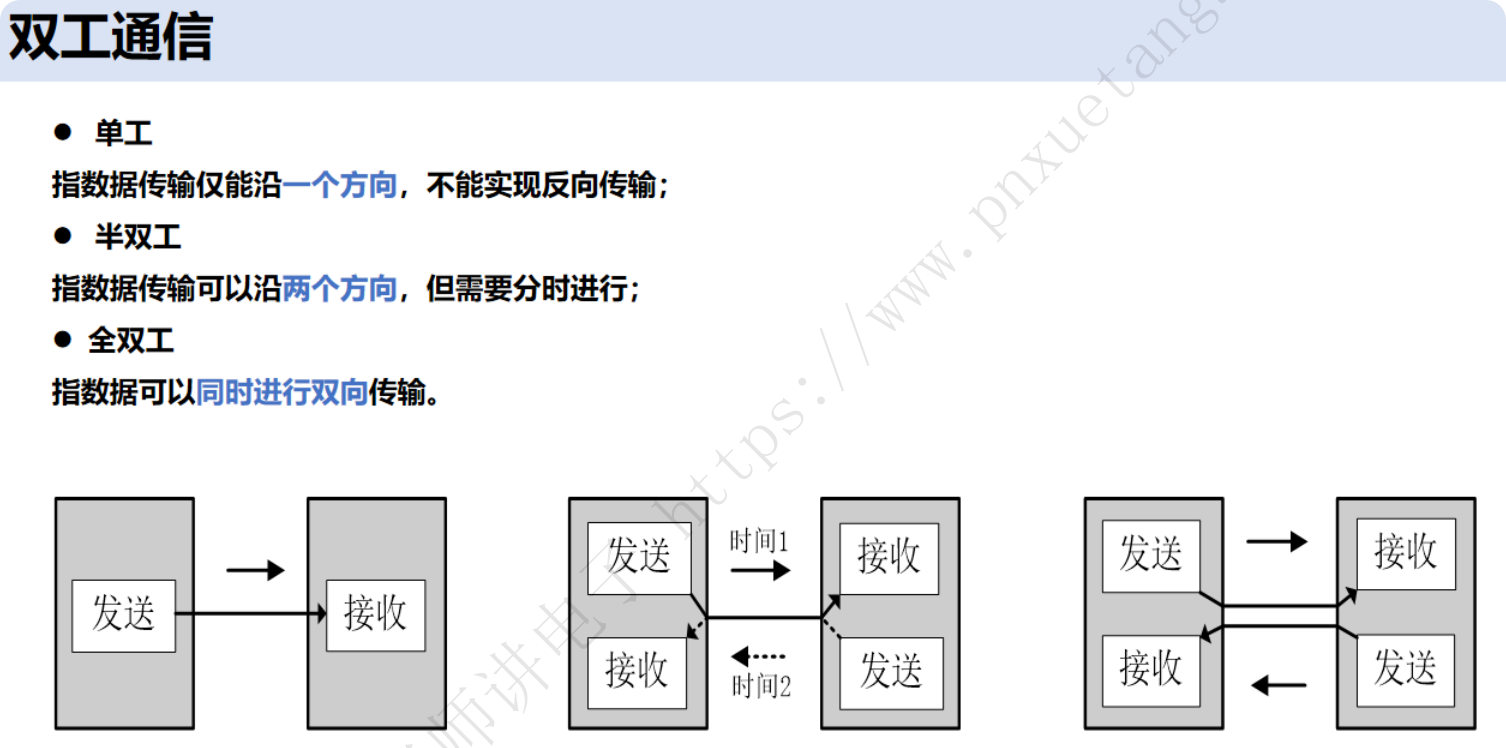

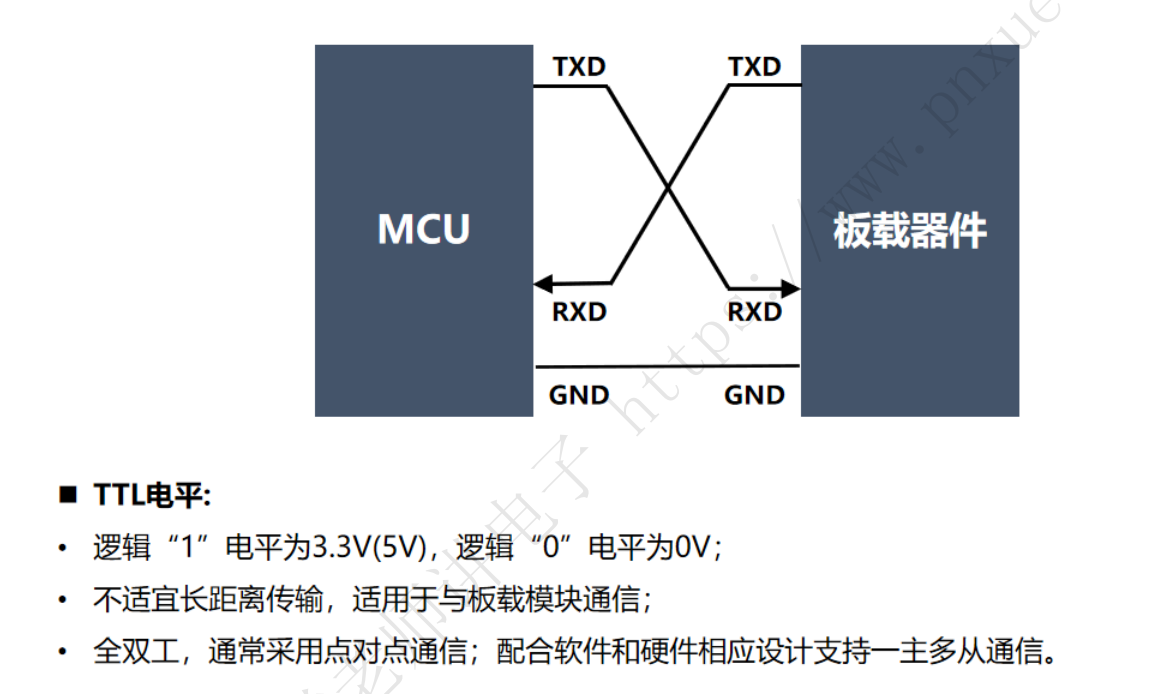

TTL是全双工

TTL是全双工

TTL (Transistor-Transistor Logic)

核心特征

-

电平范围:

-

逻辑 1 (High):+3.3V 或 +5V(取决于供电电压)

-

逻辑 0 (Low):0V (GND)

-

-

通信方式 :全双工(需独立 TX/RX 线)

-

拓扑结构:点对点(1:1)

-

传输距离:短距离(通常 ≤ 0.5 米)

典型应用场景

-

单片机开发板(如 Arduino、STM32)的 UART 引脚

-

板级芯片间通信(如 MCU 连接传感器)

-

USB转TTL模块(如 CH340、CP2102)

优点与局限

| 优点 | 局限 |

|---|---|

| 简单易用,无需复杂转换 | 抗干扰能力弱(单端信号) |

| 低功耗(直接匹配数字IC电平) | 传输距离短 |

| 成本低(无需电平转换芯片) | 不支持多设备共享总线 |

⚠️ 关键风险:TTL 与 RS-232 直接连接会烧毁芯片!(电压不兼容)

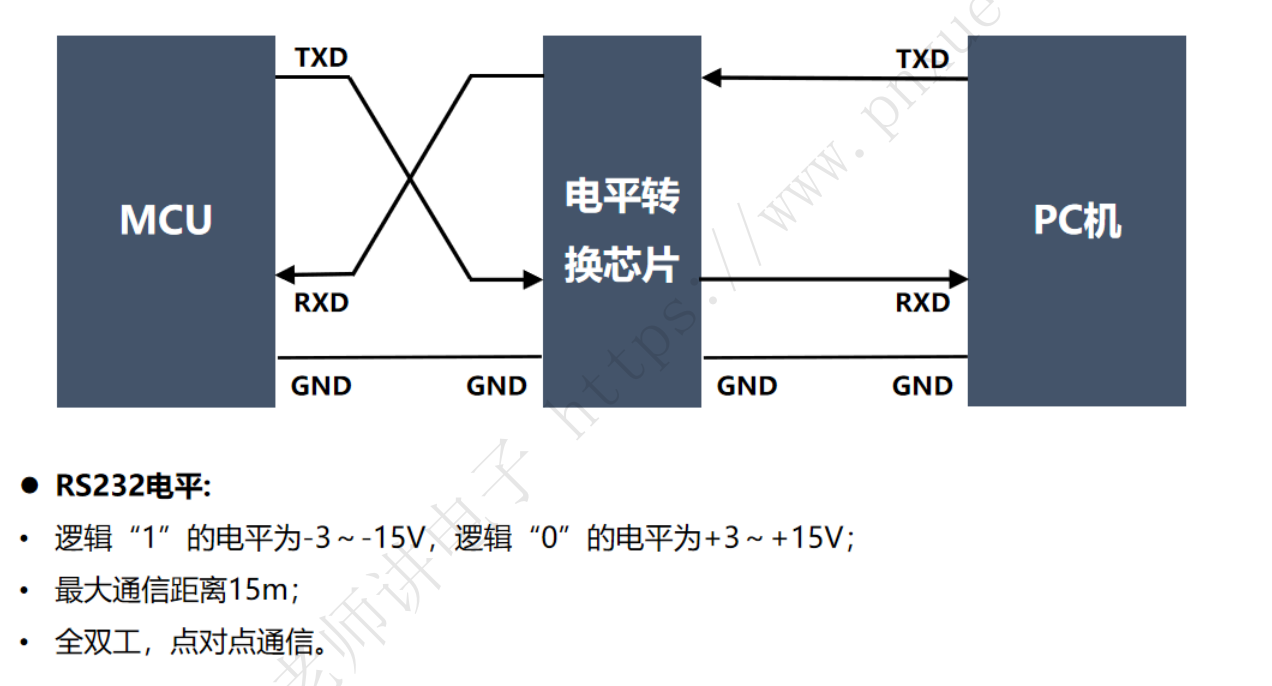

RS-232 (Recommended Standard 232)

核心特征

-

电平范围:

-

逻辑 1 (High) :-3V ~ -15V(负电压)

-

逻辑 0 (Low) :+3V ~ +15V(正电压)

-

-

通信方式 :全双工(独立 TX/RX 线)

-

拓扑结构:点对点(1:1)

-

传输距离:中距离(≤ 15 米,波特率≤20kbps)

典型应用场景

-

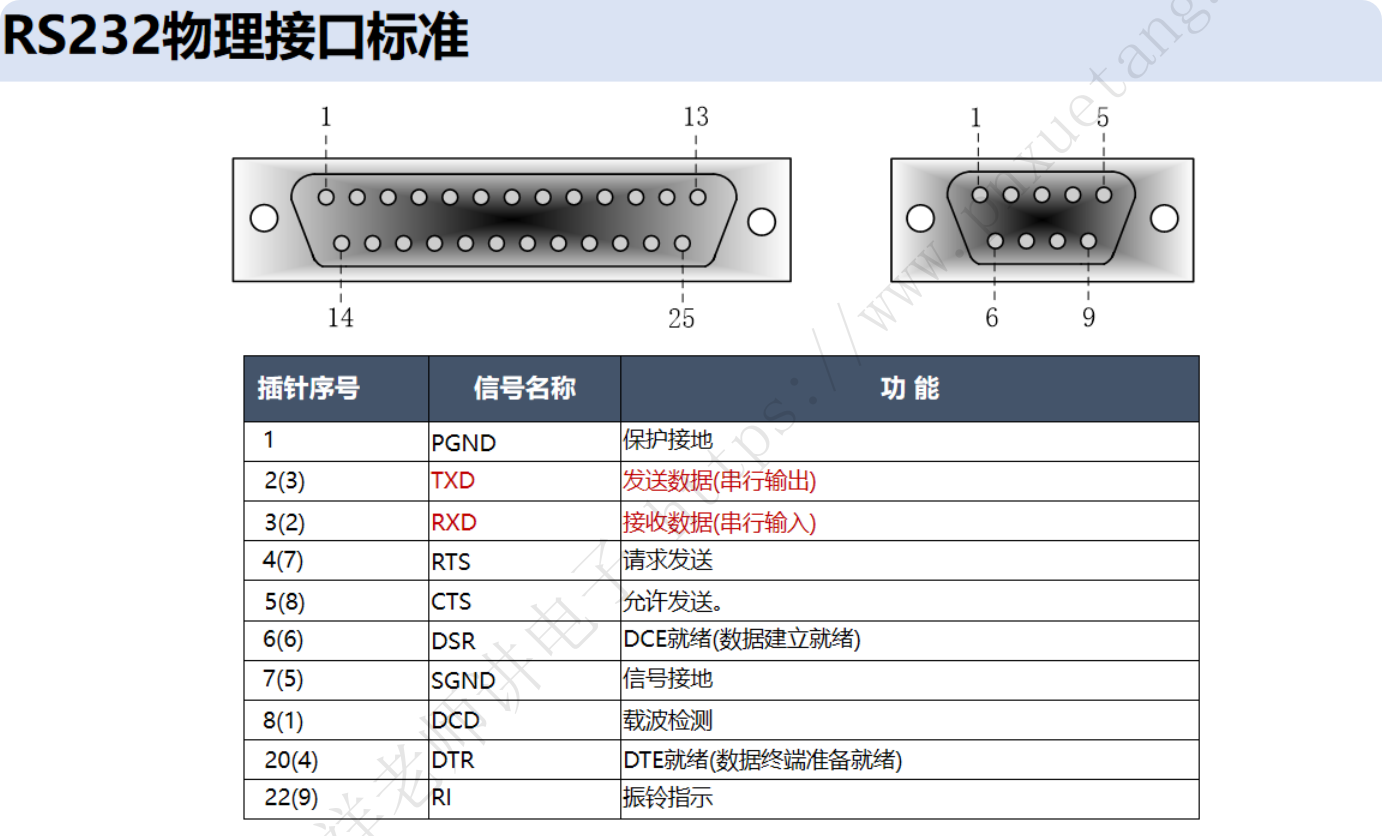

老式计算机串口(DB9 接口)

-

工业设备配置口(如路由器、交换机 Console 口)

-

短距离工控设备通信

优点与局限

| 优点 | 局限 |

|---|---|

| 抗干扰强于 TTL(高电压摆幅) | 速度低(通常 ≤ 115.2kbps) |

| 支持较长距离传输 | 需专用电平转换芯片(如 MAX232) |

| 广泛兼容旧设备 | 不支持多设备总线 |

常用于和PC机通信

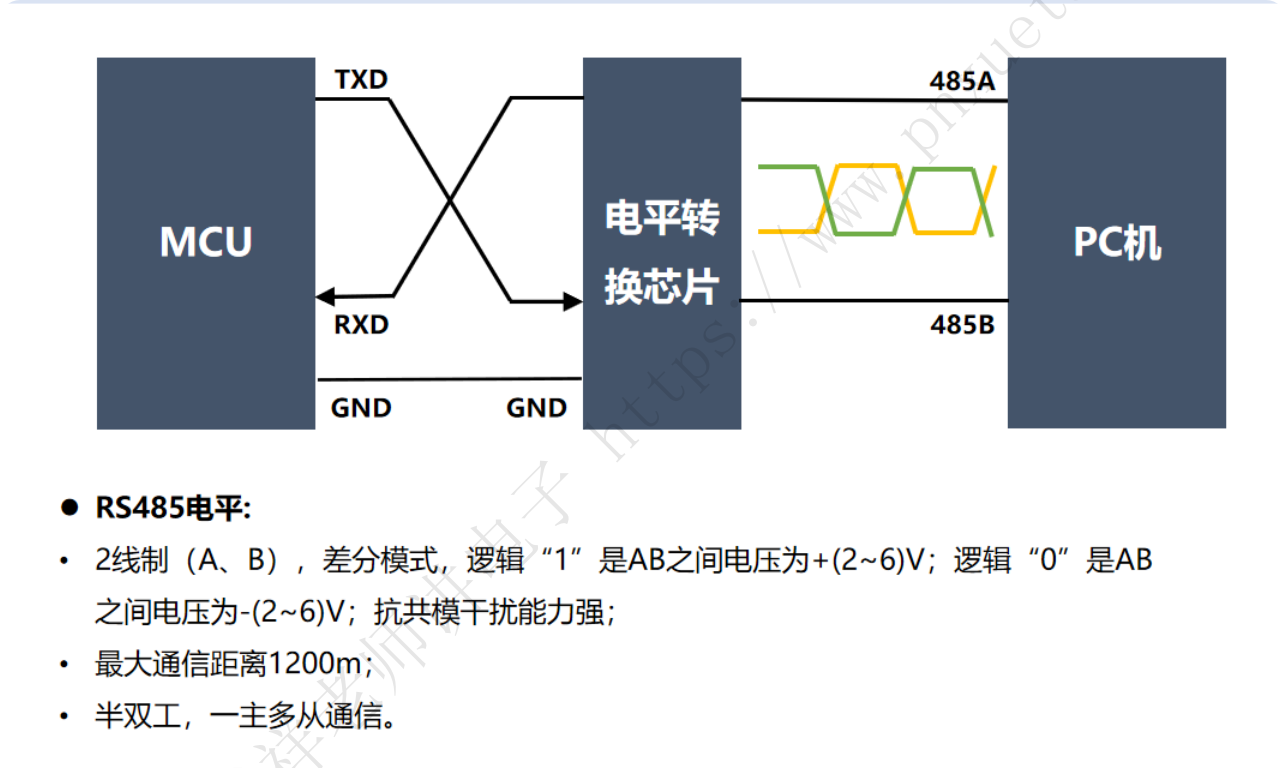

RS-485 (Recommended Standard 485)

核心特征

-

电平范围:

-

逻辑 1:B-A > +200mV(差分正电压)

-

逻辑 0:B-A < -200mV(差分负电压)

-

-

通信方式 :半双工 (单对差分线)或 全双工(两对差分线)

-

拓扑结构 :多点总线(1:N,最多 32 设备)

-

传输距离:长距离(≤ 1200 米,波特率≤100kbps)

典型应用场景

-

工业自动化总线(如 Modbus RTU)

-

楼宇安防系统(门禁、传感器网络)

-

远距离数据采集(电力监控、环境监测)

硬件特性

-

差分信号 :

使用双绞线传输

A+/B-信号,通过电压差抵消共模噪声。 -

终端电阻 :

总线两端需接 120Ω 电阻匹配阻抗,防止信号反射。

优点与局限

| 优点 | 局限 |

|---|---|

| 超强抗干扰(工业EMC环境) | 需手动控制收发使能(半双工) |

| 支持多设备组网(总线拓扑) | 协议需地址寻址(如 Modbus) |

| 长距离传输(千米级) | 布线需终端电阻 |

三者的核心对比表

| 特性 | TTL | RS-232 | RS-485 |

|---|---|---|---|

| 电平类型 | 单端数字电平 | 单端高压 (±3-15V) | 差分电压 (A/B线) |

| 逻辑表示 | 1=+3.3V/5V, 0=0V | 1=-3~-15V, 0=+3~+15V | 1=B-A>+200mV, 0=B-A<-200mV |

| 传输距离 | ≤ 0.5m | ≤ 15m | ≤ 1200m |

| 拓扑结构 | 点对点 (1:1) | 点对点 (1:1) | 多点总线 (1:N) |

| 通信模式 | 全双工 | 全双工 | 半双工/全双工 |

| 抗干扰能力 | 弱 | 中 | 极强(差分抗噪) |

| 最大速率 | 10Mbps+ | 115.2kbps | 10Mbps(短距离) |

| 典型转换芯片 | 无需 | MAX232, SP3232 | MAX485, SN65HVD72 |

4. 互联转换方案

(1) TTL ↔ RS-232

-

必备芯片:电平转换器(如 MAX232)

-

电路原理 :

MAX232 内部集成电荷泵,将 TTL 的 0V/5V 转换为 RS-232 的 ±10V。

(2) TTL ↔ RS-485

-

必备芯片:RS-485 收发器(如 MAX485)

-

关键控制 :

半双工模式下需 RE/DE 引脚控制收发方向(RE=接收使能, DE=发送使能)。

(3) RS-232 ↔ RS-485

-

转换器结构 :

RS-232 → TTL → RS-485(两级转换)

-

工业方案 :

专用隔离转换模块(如 ADM2483 带光耦隔离)。

5. 协议与电气标准的关系

-

UART 是协议层:定义数据帧格式(起止位、数据位、校验位)。

-

TTL/RS-232/RS-485 是物理层:定义如何用电压表示 UART 的 0 和 1。

✅ 重要结论 :

同一 UART 数据可通过不同物理层传输(例如:MCU 的 TTL-UART → MAX485 → RS-485 总线)。

6. 选型指南

| 场景 | 推荐标准 | 理由 |

|---|---|---|

| 板级芯片间通信 | TTL | 简单直接,无需转换 |

| 设备调试口(短距离) | RS-232 | 兼容旧设备,抗干扰优于 TTL |

| 工厂传感器网络(长距离多节点) | RS-485 | 抗干扰+多设备+远距离 |

| 高速数据传输(如视频流) | 非三者(用LVDS/USB) | TTL/RS 速率不足 |

经典问题解答

Q1 :为什么 RS-232 用负电压表示逻辑 1?

A:历史设计(1960年代),高电压摆幅(±15V)抗干扰更强,且负电压可区分线路断开(0V)与逻辑 1。

Q2 :RS-485 如何避免总线冲突?

A :半双工模式下需软件协议控制(如 Modbus 的主从轮询),发送前检测总线空闲(监听-发送机制)。

Q3 :TTL 与 CMOS 电平的区别?

A:CMOS 电平范围更宽(逻辑 1 ≈ Vcc,逻辑 0 ≈ 0V),但现代系统中常统称 "TTL电平"(实际多为 CMOS 兼容)。