【 声明:版权所有,欢迎转载,请勿用于商业用途。 联系信箱:feixiaoxing @163.com】

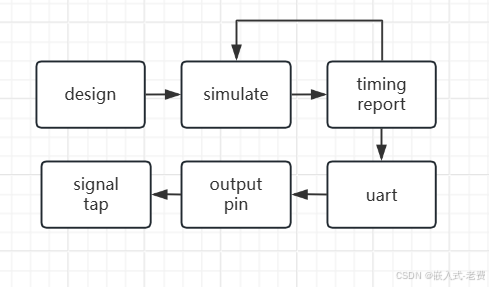

我们之前在学校学习c、c++的时候,其实学校漏掉了很重要的一个教学环节,那就是调试、测试。很多时候我们代码写出来了,不知道怎么测试、调试。其实fpga也是一样的。fpga本质上还是信号的处理,我们与其说是写代码,不如说是设计电路。这个电路以寄存器和时序电路为基础,以组合电路为辅,通过状态机、协议和流程共同实现一个模块的开发。那么这个模块写的对不对,就需要通过调试来进行判别了。

1、做好设计

设计是我们所有工作的起点,这个设计的来源,一方面是需求,一方面是标准协议,还有一方面来自于fpga的现实接口约束。在开发之前,就要想好解决什么问题,系统的协议、交互逻辑和状态机是什么样的。子模块的信号,甚至可以提前把波形设计好,这样就可以直接转化成verilog代码了。后续的调试就变成对这个波形的确认。

2、仿真调试

仿真是很重要的一个环节。fpga相比较c语言编程有一个缺点,那就是综合、编译的速度会比较慢。在前期开发调试的时候,没有必要直接上板子测试,这和嵌入式开发是一样的。能仿真的部分,尽量用仿真来解决。简单一点的iverilog+gtkwave仿真,复杂一点的modelsim仿真,都是可以去做的。仿真的部分,尽可能做成自动化测试,用类似python之类的脚本串起来,这样效率会比较高。仿真本身解决的是逻辑层面的问题,如果逻辑层面都有问题,直接上fpga基本就是浪费时间。

3、会查看时序报告

前面说过,仿真只是解决功能层面是否正确,但是时序层面是不是正确,需要通过综合时得到的时序报告,去进行判断。实际fpga验证的时候,最好把这些关键路径做一个时序优化。这里面最主要的方法,就是组合逻辑拆分、case优化、做延时tap。修改后,通常需要回头重新做一下仿真测试。测试没问题之后,继续修正时序,直到得到想要的结果。毕竟我们总是希望频率越高越好,而频率收到关键路径的约束,所以只好通过识别关键路劲,通过优化来不断提高处理频率。

时序的本质,其实就在于两个clock之间的组合逻辑,是否可以满足时钟约束的要求。**我们编写时序电路的时候,中间会有很多的判断条件。这些判断条件综合出来,很多都是组合逻辑。**这些组合逻辑如果过于复杂和冗长,其实是需要进行优化和拆分的,这就是时序分析的根本来源。

4、添加串口打印

串口本身还是非常方便的,一个fifo模块,再加一个uart,就可以通过循环打印的方式,不停把状态机里面的信号读出来,非常方便。**如果奢侈一点的话,可以自己准备一个软核cpu,这样还可以通过软核+串口的方式,直接编程解决ip内部的调试问题。**要做到这一点,就要对编译器、链接器、汇编、二进制代码有所了解。某种意义上,这就相当于一个小型的mcu开发了。

5、output pin

这里的outpin就不仅仅是串口打印,而是内部的register、wire信号查看,绑定到外部的pin而已。原理是比较简单,就是开发效率比较低。因为想看什么信号,每次都需要通过重新综合+外部示波器查看的办法来解决。当然如果对cpu软核和嵌入式软件不算太了解,这也是很有效的一种调试方式。

6、signal tap

signal tap的本意就是通过内置signal ram的方式,把一部分运行信号锁到ram里面,再通过jtag的方式把信号送出来。因为signal tap本身是占有一定资源的,所以实际使用的时候,必须有选择性地去挑选一些信号进行debug处理。本质上,signal tap就是一个藏在fpga里面的小示波器。挑选哪些信号,怎么触发,都是可以通过ide进行设置的。和output pin一样,它也需要在每次调试的时候,重新进行综合处理。

7、其他

对fpga的调试,其实很大程度上取决于自己对于软件的理解、对于数字电路的理解。实际开发的时候,要把自己想象成一个cpu、一个时序和组合逻辑模块,而不是单纯的verilog代码,这样会调试起来好很多。出现问题,优先从原理入手,原理没问题再看电路、看信号、看打印,这样一步步去解决,最终肯定会找到问题的所在。