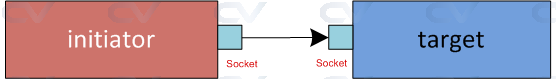

TLM 2.0引入了套接字(Socket)机制,实现发起方(initiator)与目标方(target)组件间的异步双向数据传输。套接字与端口(port)和导出(export)同源,均继承自uvm_port_base基类。发起事务的组件使用发起方套接字(initiator socket),称为发起方;接收事务的组件使用目标方套接字(target socket),称为目标方。需注意:发起方套接字仅能连接目标方套接字,目标方套接字仅能连接发起方套接字。

TestBench

让我们来看看启动器组件,了解套接字是如何声明和使用的。b_transport() 方法中使用的时序注解参数允许时序点从调用和返回任务的仿真时间中偏移。

cpp

class initiator extends uvm_component;

`uvm_component_utils (initiator)

// Declare a blocking transport socket (using initiator socket class)

uvm_tlm_b_initiator_socket #(simple_packet) initSocket;

uvm_tlm_time delay;

simple_packet pkt;

function new (string name = "initiator", uvm_component parent= null);

super.new (name, parent);

endfunction

virtual function void build_phase (uvm_phase phase);

super.build_phase (phase);

// Create an instance of the socket

initSocket = new ("initSocket", this);

delay = new ();

endfunction

virtual task run_phase (uvm_phase phase);

// Let us generate 5 packets and send it via socket

repeat (5) begin

pkt = simple_packet::type_id::create ("pkt");

assert(pkt.randomize ());

`uvm_info ("INIT", "Packet sent to target", UVM_LOW)

pkt.print (uvm_default_line_printer);

// Use the socket to send data

initSocket.b_transport (pkt, delay);

end

endtask

endclass考虑目标套接字,你会发现它与我们在前几次课程中看到的端口和导出方案非常相似。

cpp

class target extends uvm_component;

`uvm_component_utils (target)

// Declare a blocking target socket

uvm_tlm_b_target_socket #(target, simple_packet) targetSocket;

function new (string name = "target", uvm_component parent = null);

super.new (name, parent);

endfunction

virtual function void build_phase (uvm_phase phase);

super.build_phase (phase);

// Create an instance of the target socket

targetSocket = new ("targetSocket", this);

endfunction

// Provide the implementation method of b_transport in the target class

task b_transport (simple_packet pkt, uvm_tlm_time delay);

`uvm_info ("TGT", "Packet received from Initiator", UVM_MEDIUM)

pkt.print (uvm_default_line_printer);

endtask

endclass缺失的一环是两个套接字之间的连接,而实现这一连接的最佳位置是在初始化器和目标组件都被实例化的环境中。

cpp

class my_env extends uvm_env;

`uvm_component_utils (my_env)

initiator init;

target tgt;

function new (string name = "my_env", uvm_component parent = null);

super.new (name, parent);

endfunction

virtual function void build_phase (uvm_phase phase);

super.build_phase (phase);

// Create an object of both components

init = initiator::type_id::create ("init", this);

tgt = target::type_id::create ("tgt", this);

endfunction

// Connect both sockets in the connect_phase

virtual function void connect_phase (uvm_phase phase);

init.initSocket.connect (tgt.targetSocket);

endfunction

endclass