【 声明:版权所有,欢迎转载,请勿用于商业用途。 联系信箱:feixiaoxing @163.com】

和c语言平台提供posix api一样,一般fpga厂家也会提供各种各样免费的ip给客户使用。这样,客户就不需要自己去写每一个ip了,把重心放在自己的业务上就好了。这些免费的ip有的是关于频率的,有的关于存储的,有的关于总线的,有的关于计算的,还有的是关于dma的,大家可以先简单了解下。

1、pll类ip

每一个fpga都有一个基本输入晶振,比如50M,或者是100M。但是实际用的时候,我们希望可以实现倍频或者分频,这种情况下就可以直接使用fpga提供的免费ip,也就是锁相环pll,直接做频率处理。我们配置好ip之后,就可以直接拿过来用即可。

2、存储设置

这里的存储设置很广,有rom,有ram等等。如果是rom,比如是查找表,我们希望提前导入到一个rom里面,那么就可以借助于rom生成这样一个ip。ram和fifo也是一样的道理。

如果需要处理的数据比较多,这个时候就会使用到ddr。因为ddr2、ddr3的编写比较麻烦,所以quartus或者vivado也会提供对应的ip供客户使用。

3、计算类ip

这里使用到的、比较多的ip就是fifo和硬件乘法。**其中fifo,在图像处理当中使用特别多,而硬件乘法则用于需要整数相乘的场景。**大家都知道,在fpga下面进行除法或者是浮点运算,都是不太容易的,这种情况下一般都是转成乘法去进行处理的。

4、各种外设总线

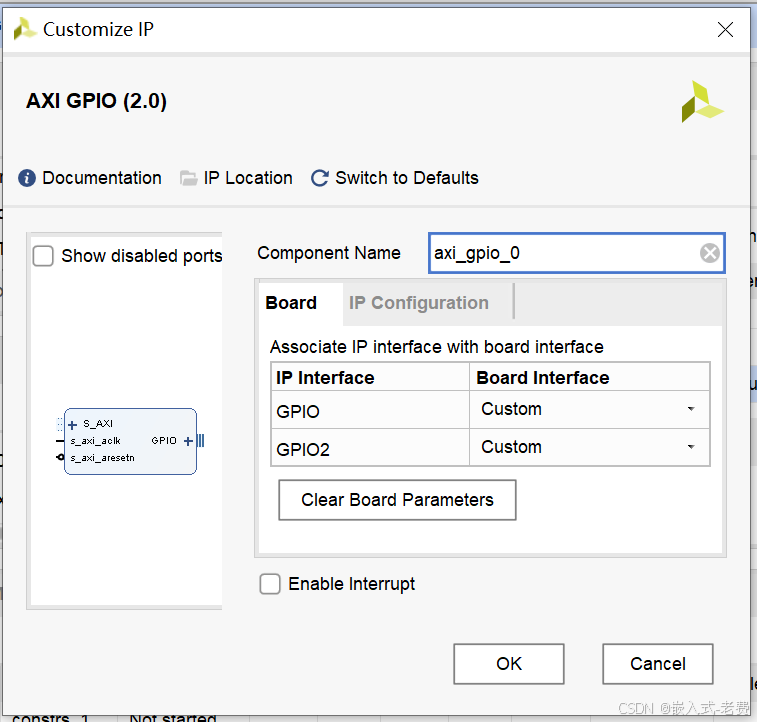

fpga要想工作,除了最小电路之外,还要和其他芯片进行通信。既然是通信,就离不开各种各样的总线,比如gpio、uart、spi、iic、pwm等等。有些总线自己用verilog写也可以,比如uart。但是如果是实际项目开发的话,建议多多使用厂家提供的免费ip,个人把精力放在业务上面,也就是状态机的设计和算法的落地上面,这样可能会更加好一点。

5、视频输出接口

图像处理,是fpga应用的一个重要应用场景。比如,如果zynq通过usb拿到的图像,可以直接在pl测通过视频接口输出。简单的VGA接口、RGB接口、MCU接口可以自己实现。如果是hdmi接口,最好还是使用厂家提供的ip去实现。

6、被低估的dma接口ip

zynq平台一般涉及到ps和pl。ps就是cpu,pl就是fpga。如果此时ddr放在ps测,那么pl要处理数据,就势必涉及到数据的搬运。这个时候用dma是最好的,不管是ddr搬到pl,还是pl送到ddr,都是可以的。我们知道dma可以实现地址递增的搬运,也可以实现同一地址的连续读写,pl一般是后者。所以不管是写的时候,还是读的时候,pl测直接在dma接口处等着数据就可以了。

7、其他

除了上面所说的ip,还有一些加密ip、以太网ip、算法ip等等,这里就不一一描述了。**本身fpga就是一个平台,厂家也提供的各种各样的模块,我们只需要在这个基础之上专注于自己的业务,精通状态机、协议和算法即可,没有必要什么都做。**把fpga用好、用起来、服务于业务,这才是最重要的。