背景:在学习高速接口协议中,往往容易混淆GTH架构的初始化流程和复位逻辑,下面学习GTH的UG576中的初始化和复位流程。

资料:UltraScale Architecture GTH Transceivers UG576 (v1.7.1) August 18, 2021

本文为UG576的学习记录。以下内容全部在官方文档中有介绍。

复位和初始化

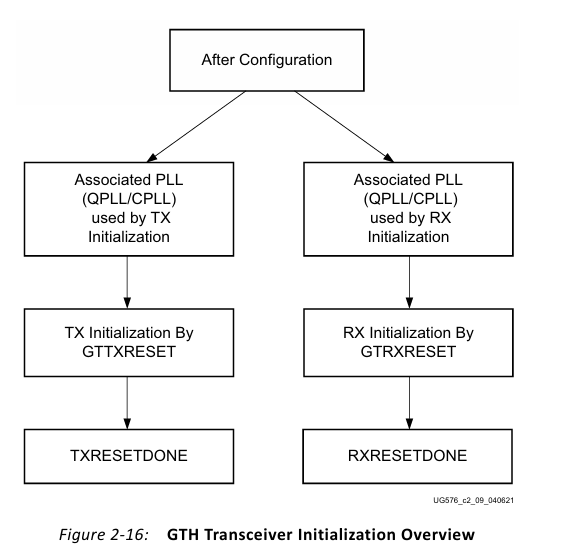

GTH收发器在设备上电并完成配置后,必须先进行初始化。收发器的TX和RX可以独立的并行的进行初始化。包含如下两个步骤。

1、初始化驱动TX/RX的关联锁相环PLL

2、初始化TX和RX数据通道包含物理层PMA与物理编码层。

GTH收发器TX和RX可以从QPLL或者CPLL中获取时钟。TX 和 RX 所使用QPLL/CPLL必须在TX和RX初始化之前完成初始化。TX和RX所使用的任意一个锁相环均需单独复位,且其复位操作完全独立于所有 TX 和 RX 的复位操作。仅当关联锁相环锁定后,才能对 TX 和 RX 数据通路进行初始化。

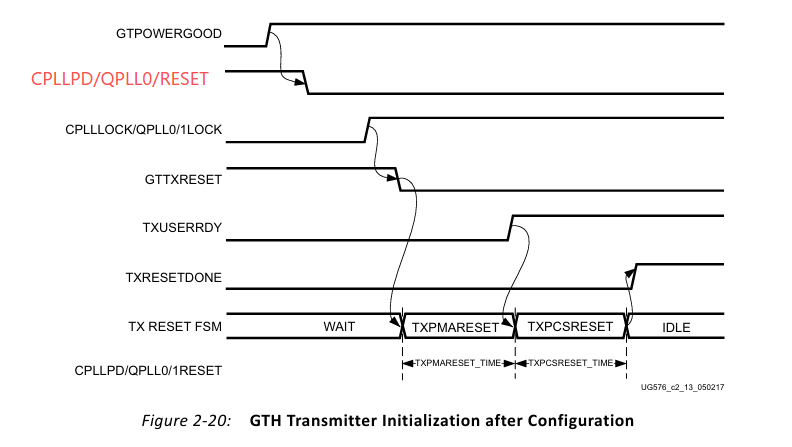

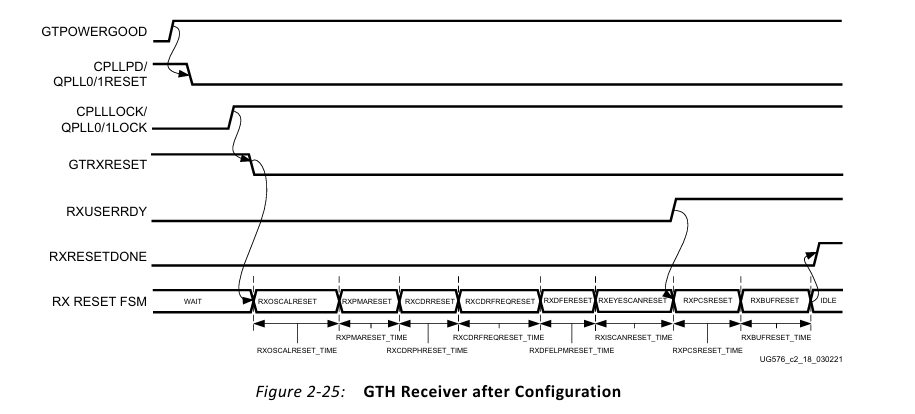

在配置完成后,分别对TX和RX所使用的QPLL和CPLL进行初始化。接着通过GTTXRESET/GTRXRESET对TX和RX初始化。最后初始化完成时对TXRESETDONE和RXRESETDONE,以此表示初始化流程结束。

GTH收发器提供两种类型的复位:初始化复位与组件复位。

初始化复位:用于完成GTH收发器的完整初始化,必须在设备上电并并完成配置后使用,在正常运行过程中,若有需要,也可以通过GTTXRESET/GTRXRESET对TX和RX重新初始化。

组件复位:适用于GTH收发器正常运行期间的特殊场景和特定子模块复位。无需对整个收发器进行完整初始化。

TX组件复位端口:包括TXPMARESET(TX PMA复位)和TXPCSRESET(TX PCS 复位)。

RX组件复位端口:包括 RXPMARESET(RX PMA 复位)、RXDFELPMRESET(RX 判决反馈均衡器低功耗模式复位)、EYESCANRESET(眼图扫描模块复位)、RXPCSRESET(RX PCS 复位)、RXBUFRESET(RX 缓冲器复位)和 RXOOBRESET(RX 带外信号模块复位)。

复位多通道和quad

复位模式

顺序模式:复位状态机以初始化复位或组件复位输入信号置高为起。会依次经过复位状态机中所有请求的复位状态之后的状态。当TX/RXRESETDONE拉高后,表示顺序复位完成。

单独模式:复位状态机仅请求组件复位。复位时长又其属性预先设定。不会执行请求状态之后的任何状态。请求的复位可以是任意组件复位,包括物理层PMA、物理编码层PCS。当TX/RXRESETDONE信号拉高时完成复位。

GTH收发器初始化复位必须使用顺序模式。所有组件复位可以选择工作在顺序模式或者单独模式,但是TX复位除外---仅能工作在顺序模式。

UltraScale系列FPGA中,GTH收发器通过GTRESETSEL信号选择顺序复位模式或者单独复位模式。在UltraScale+系列FPGA中,GTH收发器通过GTTXRESETSEL与GTRXRESETSEL分别对TX/RX选择复位模式。

正常工作期间,引用可以通过顺序模式或单独模式对GTH收发器或RX进行复位。复位前需要先将RESETOVER信号置低。对于UltraScale,需要在任何复位信号有效前300-500ns置位RESETOVRD 和 GTRESETSEL 。对于UltraScale+,需要在任何复位信号有效前300-500ns置位RESETOVRD 和 GTTXRESETSEL/GTRXRESETSEL置位。

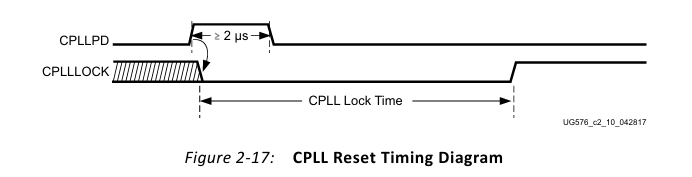

CPLL复位

CPLL使用前复位。时序图如下。CPLLPD信号至少拉高2us。

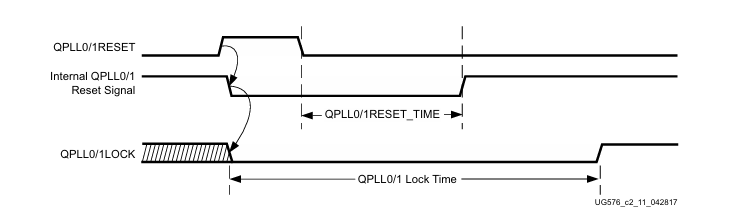

QPLL0/QPLL1复位

QPLL使用前复位。QPLL0/1RESET用于复位QPLL0/1信号。内部会自己产生一个QPLL0/1RESET信号。这个内部产生的复位信号持续时间远大于外部。QPLL0/1LOCK为锁定指示。

TX发送端初始化和复位

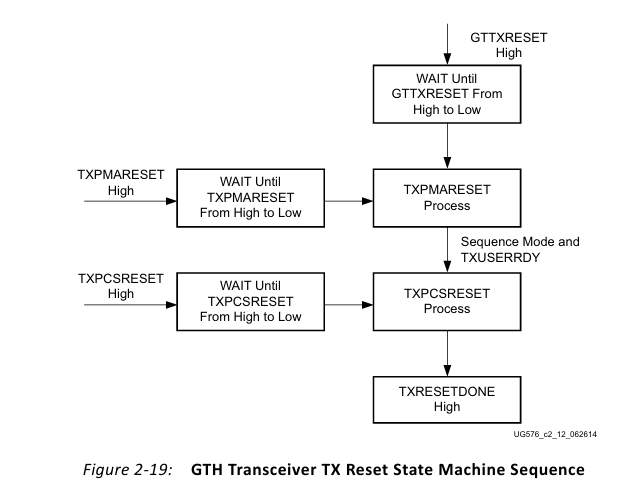

GTH收发器发送端TX采用复位状态机控制复位过程。复位过程分为两个区域,发送端PMA复位,和PCS复位。这种分区设计使得发送端的初始化和复位只能工作在顺序模式下。

初始化阶段发送端必须在顺序模式下使用GTTXRESET信号。激活GTTXRESET信号可以自动触发一次完整的异步发送端复位。在正常工作期间,顺序模式允许通过激活TXPMARESET信号来复位发送端,并继续运行复位状态机。直至TXRESETDONE信号从低到高。

发送端复位状态机在检测到TXUSERRDY信号变高之前。不会复位PCS。在满足以下条件后,将TXUSERRDY置高。

1、应用所使用的所有时钟TXUSRCLK/TXUSRCLK2均已稳定。

2、用户接口已准备好向GTH收发器传输数据。

配置完成后GTH收发器发送端TX复位

1、为使用顺序模式,GTRESETSEL(UltraScale )或 GTTXRESETSEL(UltraScale + )必须为低电平。

2、必须使用GTTXRESET信号。

3、在检测到TXRESETDONE信号拉高之前,整个复位过程中TXPMARESET 和 TXPCSRESET 信号必须保持低电平。

4、PLL锁定前,不能将GTTXRESET置低。

5、释放C/QPLLREST和GTRESET信号之前,需要确保GTPOWERGOOD信号为高。

若复位模式为单独模式,则需要执行以下操作:

1、将复位模式改为顺序模式。

2、等待300-500ns。

3、按照图所述复位序列,置位QPLLRESET、CPLLPD和GTTXRESET信号。

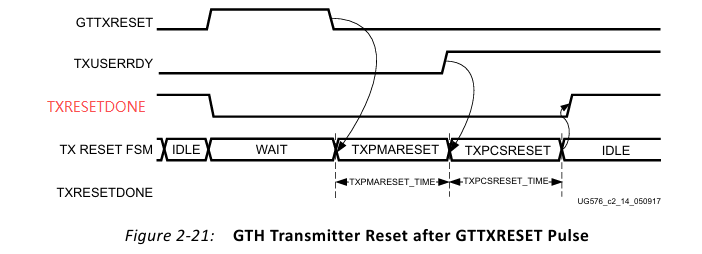

GTH 收发器发送端(TX)响应 GTTXRESET 脉冲的复位

GTH允许通过向GTTXRESET发送高电平有效脉冲,在任何时候对整个发送端进行复位。

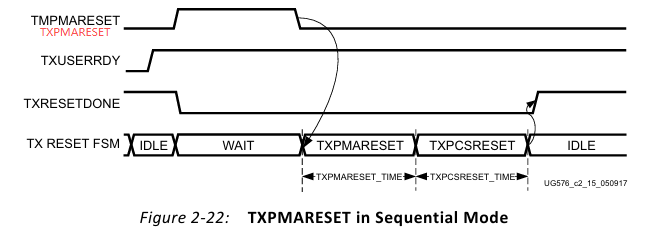

GTH 收发器发送端(TX)组件复位

发送端PMA和PCS可单独复位。在 TXPMARESET 或 TXPCSRESET 过程完成之前,GTTXRESET 必须保持低电平。将TXPMARESET从高电平拉低会启动PMA复位过程。在顺序模式下,若TXUSERRDY为高电平,复位状态机会在完成PMA复位后自动启动PCS复位。

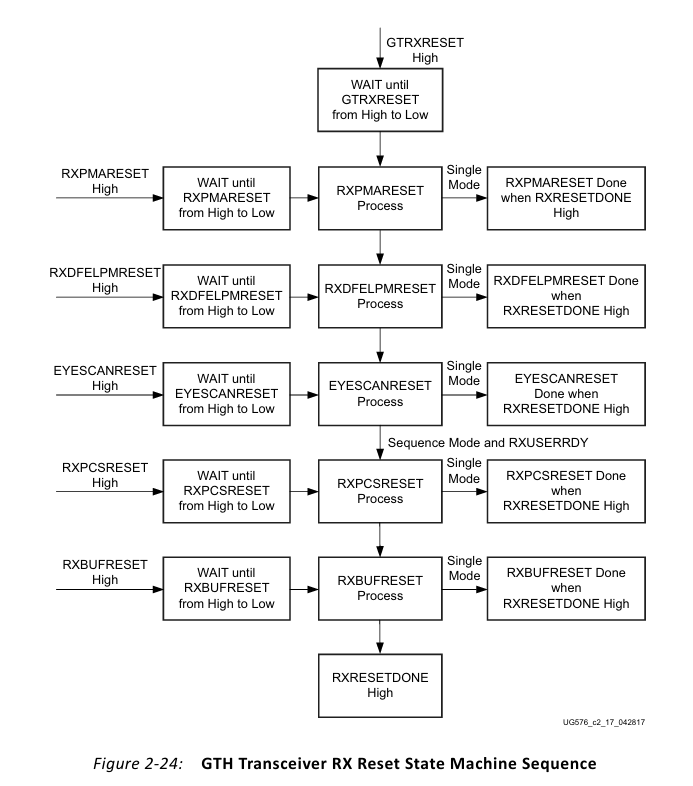

RX接收端初始化和复位

接收端复位比发送端复位复杂。

接收端顺序模式:初始化GTH收发器接收端RX,必须在顺序模式下使用GTRXRESET信号。激活后自动完成一次接收端复位。还可以通过使用以下信号来启动复位,包括 RXPMARESET(接收端 PMA 复位)、RXDFELPMRESET(接收端 DFE 低功耗模式复位)、EYESCANRESET(眼图扫描复位)、RXPCSRESET(接收端 PCS 复位)和 RXBUFRESET(接收端缓冲器复位),并继续运行复位状态机,直至 RXRESETDONE 信号从低电平跳转为高电平。

接收端单独模式:当收发器接收端工作在单独模式时,复位序列中的 RXPMARESET、RXDFELPMRESET、EYESCANRESET、RXPCSRESET 和 RXBUFRESET 可单独独立执行,不会触发其他复位区域的复位。

无论那种模式,接收端复位状态机在RXUSERRDY拉高之前都不会复位PCS。RXUSERRDY拉高条件。

1、应用所使用的所有时钟TXUSRCLK/TXUSRCLK2均已稳定。

2、用户接口已准备好从GTH收发器接收数据。

配置完成后GTH收发器接收端复位

接收端复位序列不会跟随全局GSR全局复位启动。必须满足一些条件,这些和TX部分基本一样。

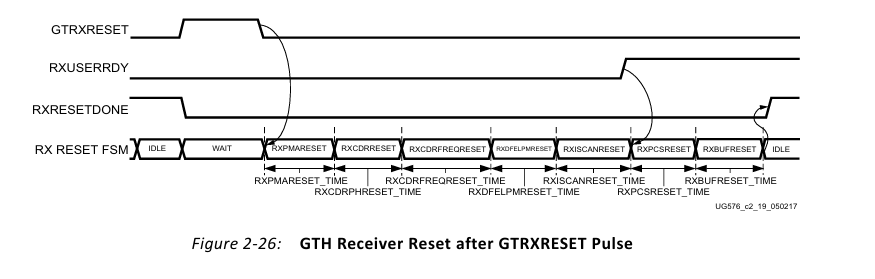

GTH 收发器接收端(RX)响应 GTRXRESET 脉冲的复位

GTH在任何需要的时候,通过向GTRRESET发送一个高电平有效脉冲。对整个GTH收发器接收端复位。

Xilinx的transceiver的初始化复位流程学习完毕。