一、基本概要

1、定时器 (EPIT GPT):

是一个通过对已知频率的时钟信号进行计数,来实现定时 、延时 或事件计数功能的硬件模块或软件机制。

定时器是嵌入式系统中常用的外设,用于完成精准定时、周期性中断、输入捕获和输出比较等功能。在i.MX6UL等嵌入式SoC中,主要提供了两种定时器:EPIT(增强型周期中断定时器)和GPT(通用定时器)。

(1)EPIT:

- 概念:

- EPIT全称为Enhanced Periodic Interrupt Timer,即增强型周期中断定时器,是i.MX6UL处理器中的一种专用定时器

- 主要特性:

- 32位向下计数器:计数器从设定值开始递减,直到减为0

- 可选时钟源:ipg_clk(66MHz)、ipg_clk_32k和ipg_clk_highfreq?

- 12位分频器:分频值范围0-4095,对应1-4096分频?

- 比较中断功能:当计数值与比较寄存器值相等时产生中断?

- 两种工作模式 :set-and-forget模式和free-running模式, 通过控制寄存器EPITx_CR的RLD位设置

- 工作模式:

-

set-and-forget模式:

- 计数器从加载寄存器(EPITx_LR)中获取初始值

- 不能直接向计数寄存器(EPIT_CNR)写入数据

- 当计数器减到0时,自动从加载寄存器重新加载数据到计数器,循环往复

- 适用于需要精确周期定时中断的应用场景

-

free-running模式:

- 计数器减到0后会重新从0xFFFFFFFF开始计数

- 不从加载寄存器获取数据

- 适用于需要连续运行但不需精确重载的场景

-

- 主要寄存器组

- EPITx_CNR(计数寄存器):反映当前计数值

- EPITx_CMPR(比较寄存器):设置比较值

- EPITx_LR(加载寄存器):设置重载值

- EPITx_SR(状态寄存器):包含中断标志位

- EPITx_CR(配置寄存器):设置时钟源、分频值、工作模式、使能定时器等

(2)GPT:

- 概念:

- GPT全称为General Purpose Timer,即通用定时器,是比EPIT功能更丰富的定时器模块

- 主要特性:

- 32位向上计数器:从0x00000000开始递增计数

- 多路时钟源选择:ipg_clk_24M、GPT_CLK(外部时钟)、ipg_clk(66MHz)、ipg_clk_32k和ipg_clk_highfreq

- 12位分频器:分频值范围0-4095,对应1-4096分频

- 输入捕获功能:2路输入捕获通道,可设置上升沿/下降沿触发

- 输出比较功能:3路输出比较通道,可设置输出模式

- 丰富的中断源:捕获中断、比较中断和溢出中断

- 两种工作模式:Restart(重启)模式和Free-Run(自由运行)模式

- 工作模式:

- Restart(重启)模式:

- 比较事件发生后计数器重新计数

- 当计数值与比较寄存器1(OCR1)的值相等时,计数器清零并重新开始计数

- 仅比较通道1有此功能,通道2和3无此功能

- 向比较寄存器1写入任何数据都会复位计数器

- 适用于需要精确周期重置的应用

- Free-Run(自由运行)模式:

-

比较事件发生后计数器继续计数

-

比较事件发生后计数器继续计数,直到0xFFFFFFFF后回滚到0x00000000

-

适用于所有三个比较通道

-

适用于需要连续运行且不中断计数的场景

-

- Restart(重启)模式:

- 主要寄存器组

-

GPTx_CR(控制寄存器):配置时钟源、工作模式、使能定时器等

- SWR(bit15):软件复位位

- FRR(bit9):工作模式选择(0=Restart,1=Free-Run)

- CLKSRC(bit8:6):时钟源选择

- ENMOD(bit1):使能模式(关闭时是否清零计数器)

- EN(bit0):定时器使能位

-

GPTx_PR(分频寄存器):设置12位分频值

-

GPTx_SR(状态寄存器):包含各种中断标志位

- ROV(bit5):计数器回滚标志

- IF1/IF2(bit4:3):输入捕获中断标志

- OF1-OF3(bit2:0):输出比较中断标志

-

GPTx_IR(中断寄存器):控制各种中断的使能

-

GPTx_OCR1-3(输出比较寄存器):设置3路比较值

-

GPTx_ICR1-2(输入捕获寄存器):保存捕获值

-

GPTx_CNT(计数寄存器):反映当前计数值

-

(3)比较EPIT、GPT

| 特性 | EPIT定时器 | GPT定时器 |

|---|---|---|

| 计数器方向 | 向下计数 | 向上计数 |

| 时钟源 | 3种(ipg_clk等) | 5种(ipg_clk_24M等) |

| 分频器 | 12位(1-4096分频) | 12位(1-4096分频) |

| 工作模式 | set-and-forget/free-running | restart/free-run |

| 输入捕获 | 不支持 | 2通道 |

| 输出比较 | 不支持 | 3通道 |

| 中断类型 | 比较中断 | 捕获/比较/溢出中断 |

| 主要用途 | 周期定时(按键消抖、周期性任务中断) | 通用定时/捕获/PWM (高精度延时) |

- 总结

- **EPIT:**更适合简单的周期性定时中断应用,结构简单,配置方便

- **GPT:**功能更为丰富,支持输入捕获、输出比较等多种功能,适合更复杂的定时需求

2、时钟(clock):

在电子系统中是一个产生稳定、周期性振荡信号的电路或组件。这个信号像节拍器或心跳一样,为数字电路中的各种操作提供同步时序基准;

在ARM裸机开发中,时钟系统是整个SoC运行的基础,它像"心跳"一样为CPU内核、总线及外设提供同步时序基准;

时钟在SoC中的作用:

同步控制:协调CPU、总线和外设的操作时序

频率调节:通过倍频/分频为不同部件提供合适的工作频率

功耗管理:通过动态调整时钟频率实现节能

时间基准:为定时器、RTC等提供时间计量基础

时钟信号的获取方式

外部输入时钟信号(通过芯片引脚)

外部晶振+内部时钟发生器

外部晶振+内部PLL倍频+内部分频器

(1)时钟数

时钟根:时钟根"(Clock Root)是时钟树(Clock Tree)中的核心节点,通常作为时钟信号的起始点或关键分发节点,负责将时钟信号分配到整个系统或芯片的各个部分; 时钟根是时钟树的源头,可以是外部晶振、内部振荡器、PLL输出或其他时钟生成模块的输出端

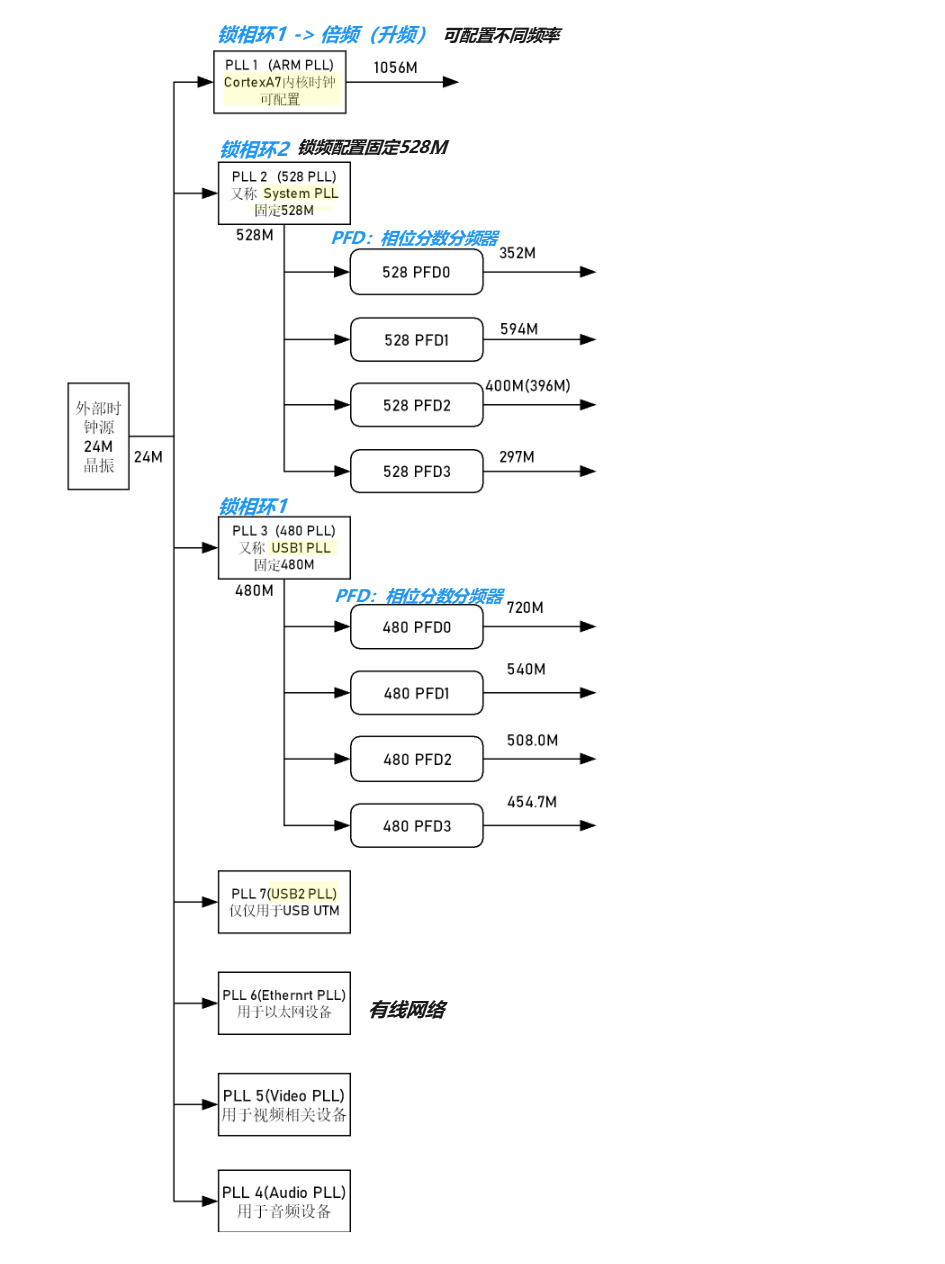

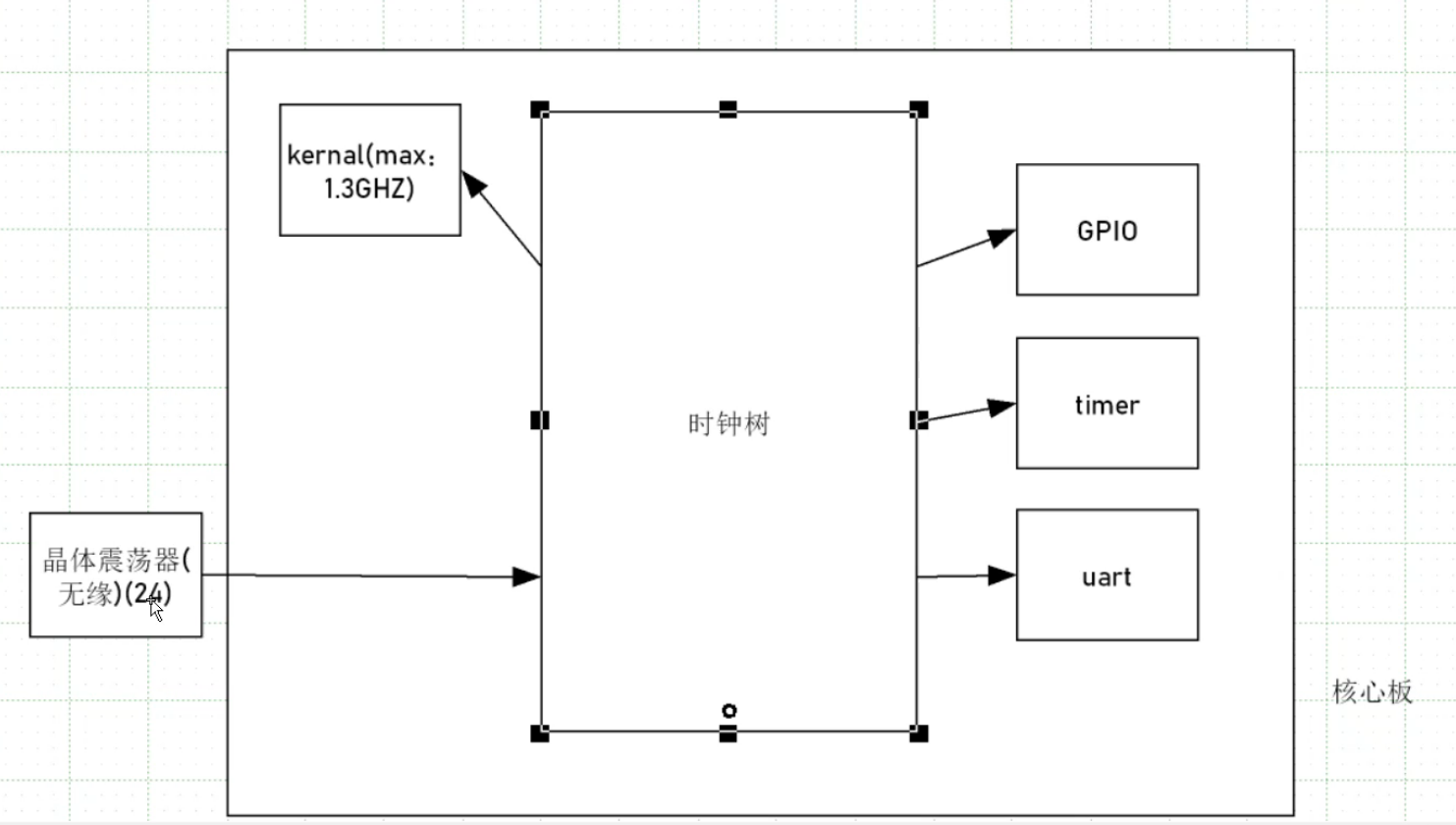

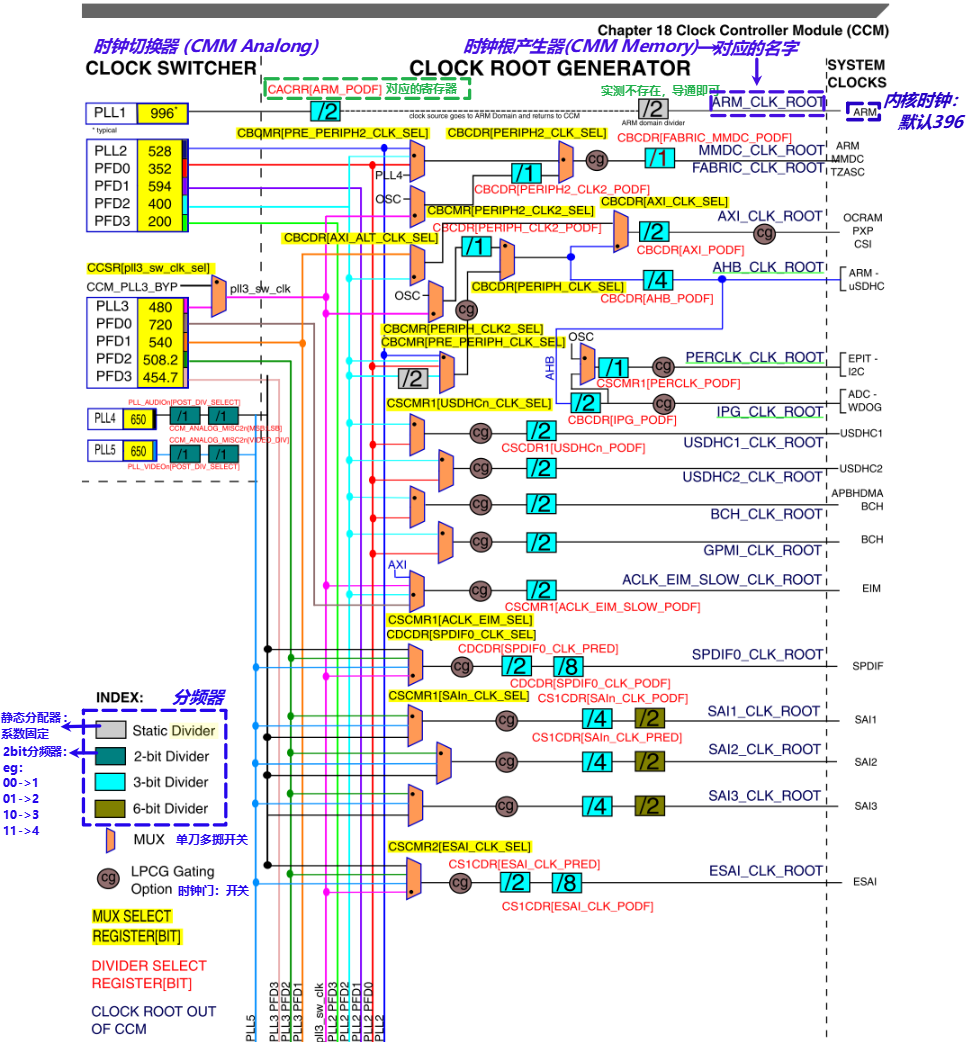

(2)时钟树综合与分配

外部晶振信号通过时钟树的倍频、分频和分配,转化为多频段时钟信号,满足从ARM内核到各类外设的时序需求;

外部激励->经过时钟数->产生合适的频率

时钟树综合与分配工作-简单分析图

时钟树综合与分配工作-简单分析图

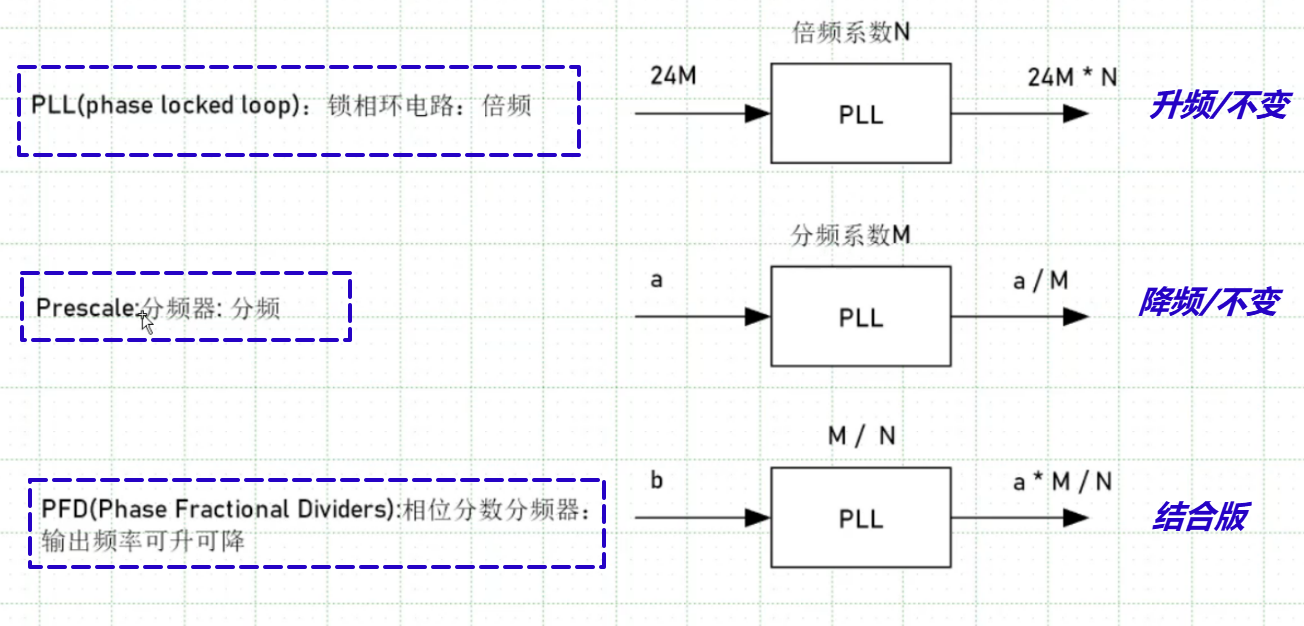

(3)时钟数三大部件

(4)时钟数

(5)简单配置过程图