源同步接口(六)

文章目录

- 源同步接口(六)

- 前言

- [源同步接口 PCB 设计要点速览](#源同步接口 PCB 设计要点速览)

-

- [1. 核心概念](#1. 核心概念)

- [2. 设计步骤(checklist)](#2. 设计步骤(checklist))

前言

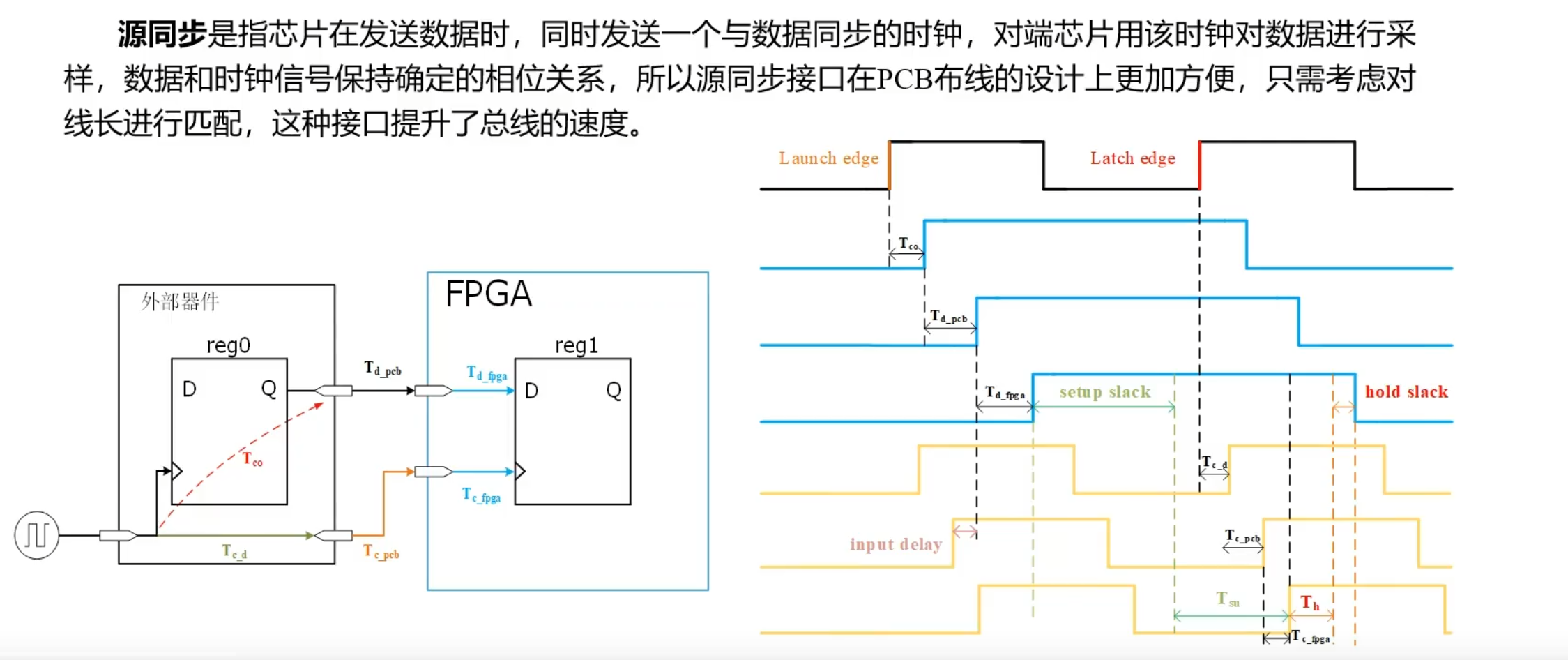

- 后面一系列分析,均可将外部设备和FPGA想象为在一个设备内种的分析方式。即,片内两个寄存器之间的时序计算 ,时刻0点是在源时钟为起点(源同步两个时钟之间是有相位差偏斜的,而系统同步可当做没有偏斜,即clk1和clk2相减为0)

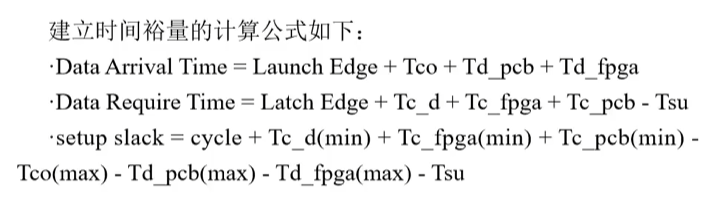

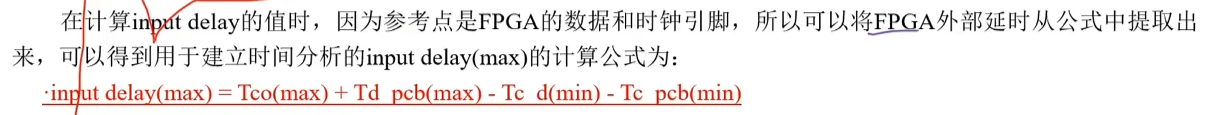

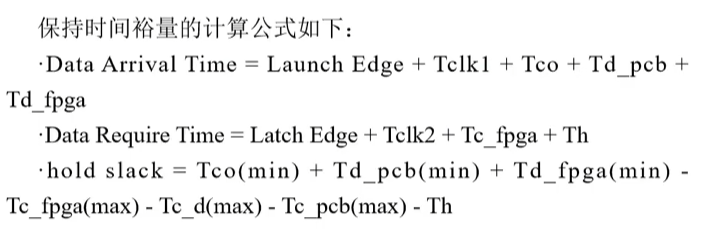

- 通过输入input_delay最大最小值,让软件知晓 如何计算建立时间裕量和保持时间裕量,才能正确分析是否违例,免得看着没时序问题,实际上隐藏时序问题不知道

- 建立时间裕量是再下一个时钟周期进行计算,时刻以源时钟开始为标准。

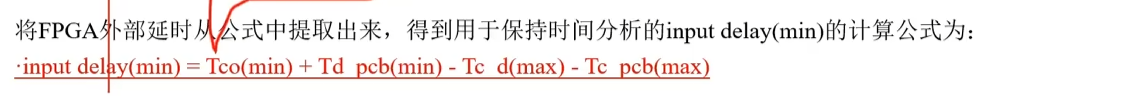

- input_delay和output_delay min和max,均是对外部走线源和目的相对延迟 来说(延迟分两个,内部延迟和外部延迟,input_delay和output_delay均分析的为外部延迟,下面公式单独提取出来了)。在分析时均以如何试探建立时间和保持时间的极限值来进行计算,以这个思路就好分析公式的用意。总体来说,求的是源到目的到达时间的相对值。

- 公式中时序分析中是源减目的还是目的减源,都可以,求出相对值即可,正负的问题,一般是在建立时间分析时是目的减去源,得到一个正值,如果为负值则违例。对于保持时间来说,源减去目的得到一个正值,说明数据来的慢,不会冲坏保持时间裕量中的数据,负值表示违例。因此建立时间和保持时间均以负表示违例,这样就统一了

- 公式求IO延迟中,求的是外部数据走向相对于时钟的偏差(数据和时钟的关系),因此以原数据路径到FPGA端口或者端口到DEV的相对于时钟的延迟来计算,即外部原延迟减去时钟之间的偏差

源同步接口 PCB 设计要点速览

一句话总结:把"时钟+数据"当成一对差分线来处理,所有时序余量都靠"等长"解决。

1. 核心概念

| 术语 | 含义 |

|---|---|

| 源同步(Source-Synchronous) | 发送端随路输出时钟,接收端用该时钟直接采样数据。 |

| Launch edge | 发送端寄存器(reg0)的触发沿。 |

| Latch edge | 接收端寄存器(reg1)的采样沿,通常与 Launch edge 相差 1 个时钟周期。 |

| Tc | 时钟网络延迟(PCB 走线 + 封装 + 缓冲)。 |

| Tdata | 数据网络延迟(PCB 走线 + 封装 + 缓冲)。 |

| Tsetup / Thold | 接收端器件要求的建立/保持时间。 |

| Input Delay | FPGA 时序约束里"告诉工具"外部已经消耗掉的时间预算(看下面的公式)。 |

| Setup Slack | 数据到达时间 -- 建立要求时间,必须 > 0。 |

| Hold Slack | 保持要求时间 -- 数据到达时间,必须 > 0。 |

2. 设计步骤(checklist)