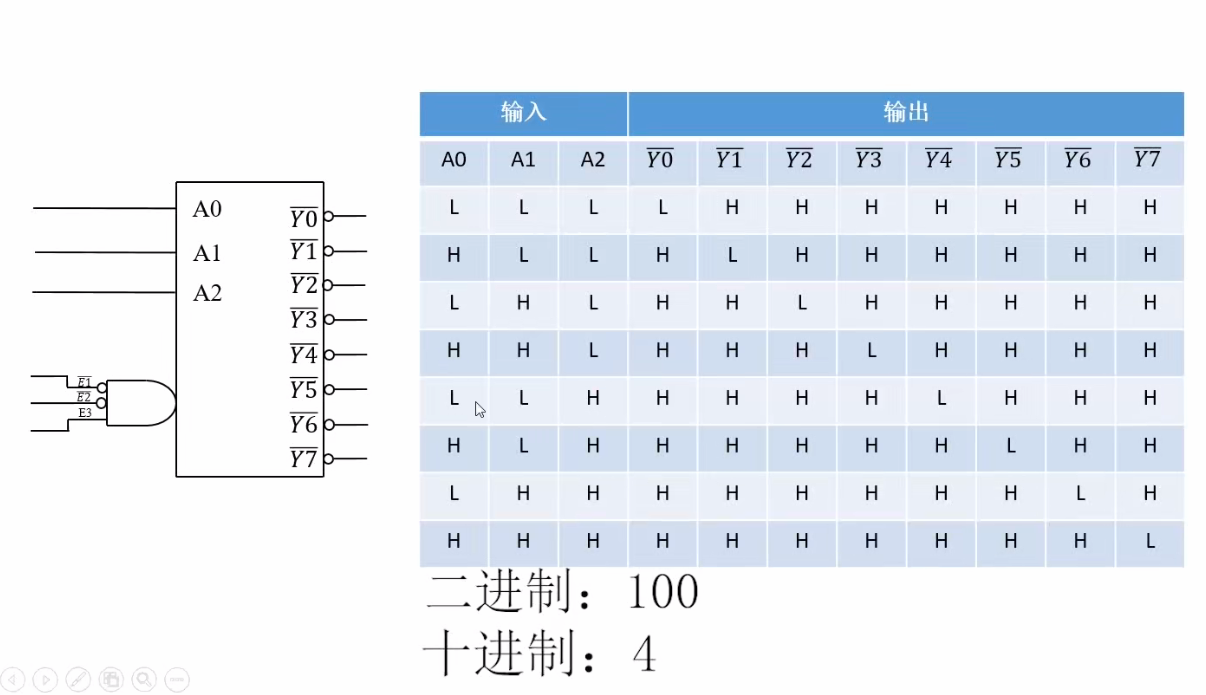

一、原理

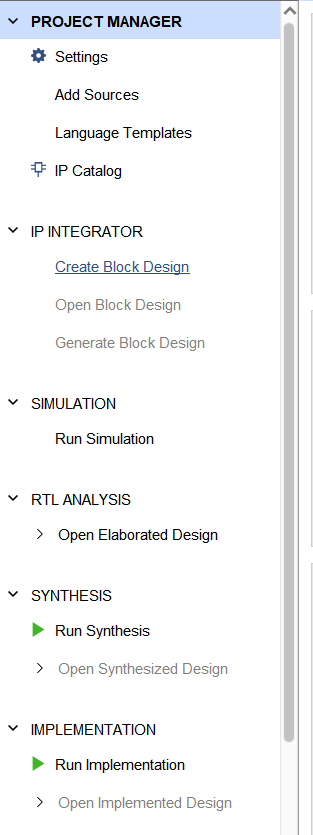

左边第一个是工程管理器

第二个是IP的,后面会讲到

第三个是仿真的

第四个是对设计进行逻辑分析的

第五个是对设计进行逻辑综合的

第六个是对设计进行逻辑布线

最后一个是生成bit文件去下载调试的

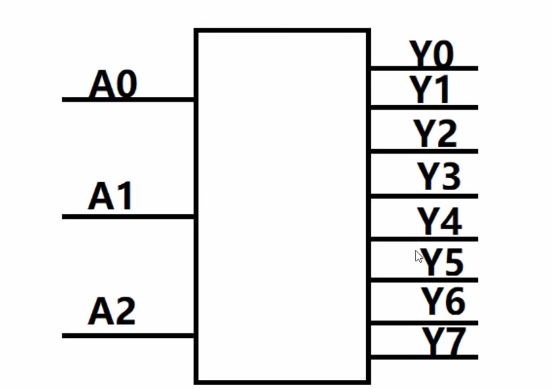

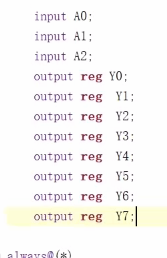

三八译码器有三个输入和八个输出

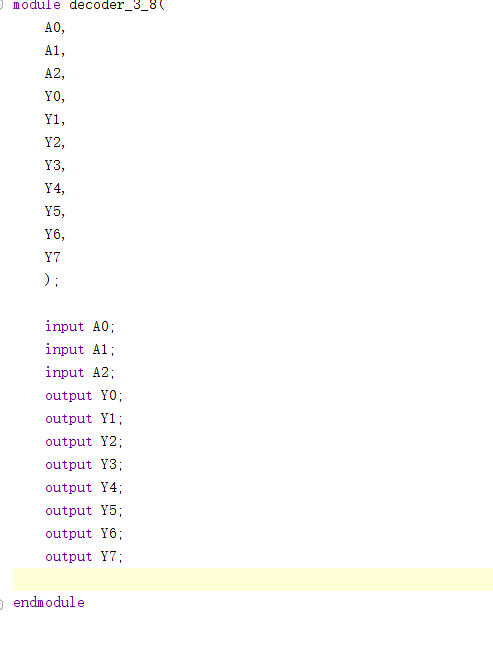

二、代码编写

根据编写的代码可以知道,这个输出没有取反,所以与三八译码器的电平输出均相反

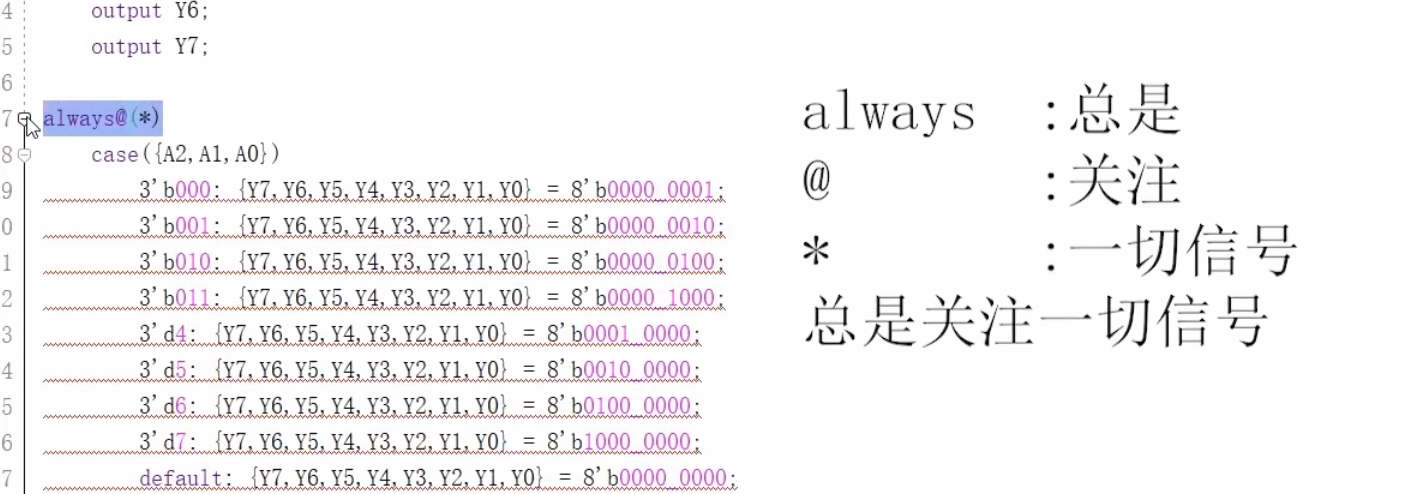

下面过程赋值语句

- 一切信号的范围是后续的赋值语句中所有需要判断的信号,比如这个代码里的A0,A1,A2

- 位拼接,A0,A1,A2都是单比特的信号,能表示的值为0或者1,位拼接就表示按从左到右的顺序进行拼接,得到三位位宽的信号

,前面四个用的是二进制表示,后面用的是十进制表示

,前面四个用的是二进制表示,后面用的是十进制表示 - 8'h5e等同于C语言中的0x5e,好处是可以在表示数据时在前面加数字,可以表示位宽

- case表示判断,判读括号里面的值是多少

由于对输出端口赋值了,就在定义是加上reg

三、设计进行分析

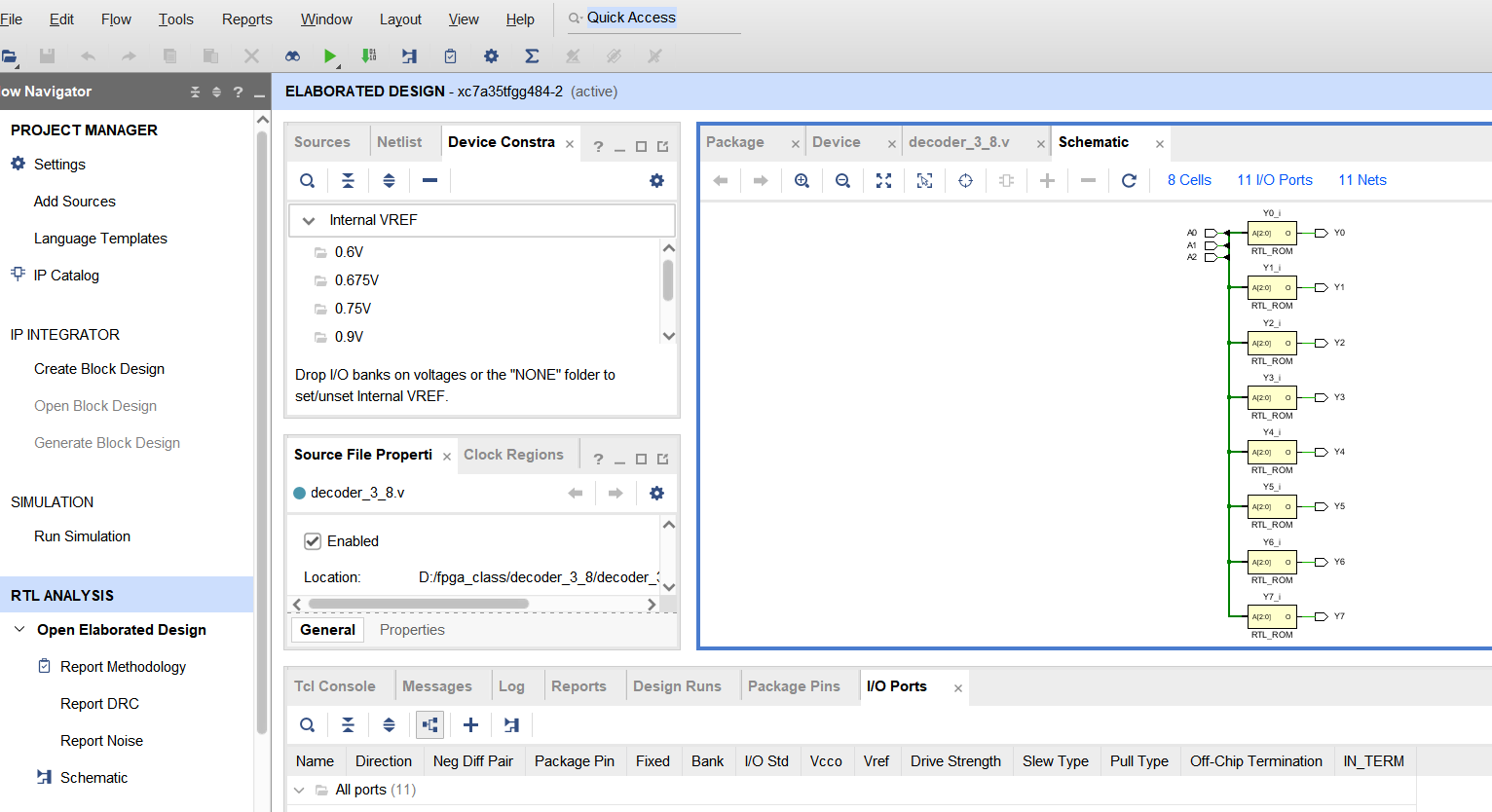

可以看到,这个图就不行二选一多路器一样形象,这是因为三八译码器不是最底层单元,软件本身是没有三八译码器这种模型的,因此就将其分解后在显示了

可以看到,这个图就不行二选一多路器一样形象,这是因为三八译码器不是最底层单元,软件本身是没有三八译码器这种模型的,因此就将其分解后在显示了