一、三八译码器

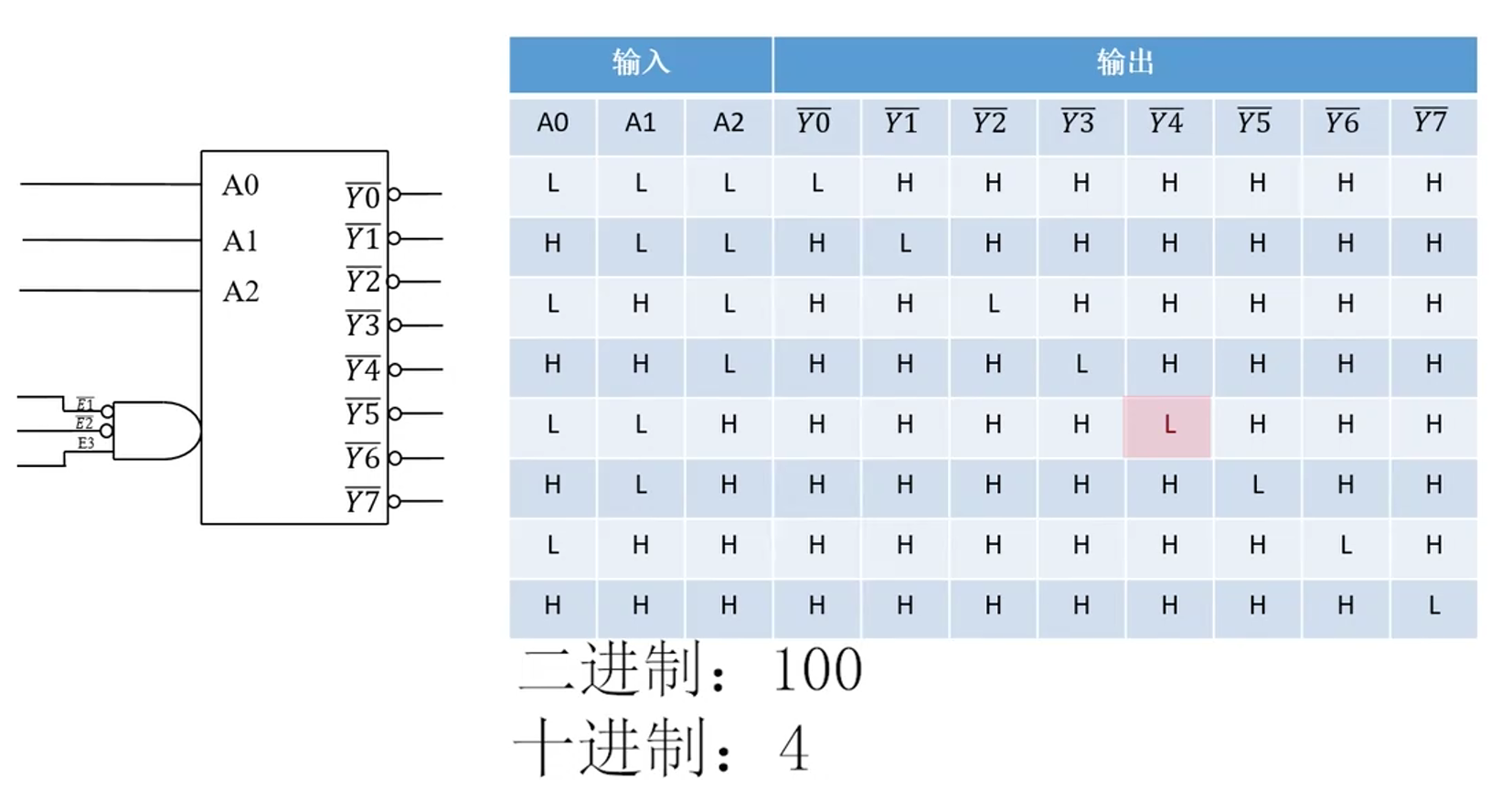

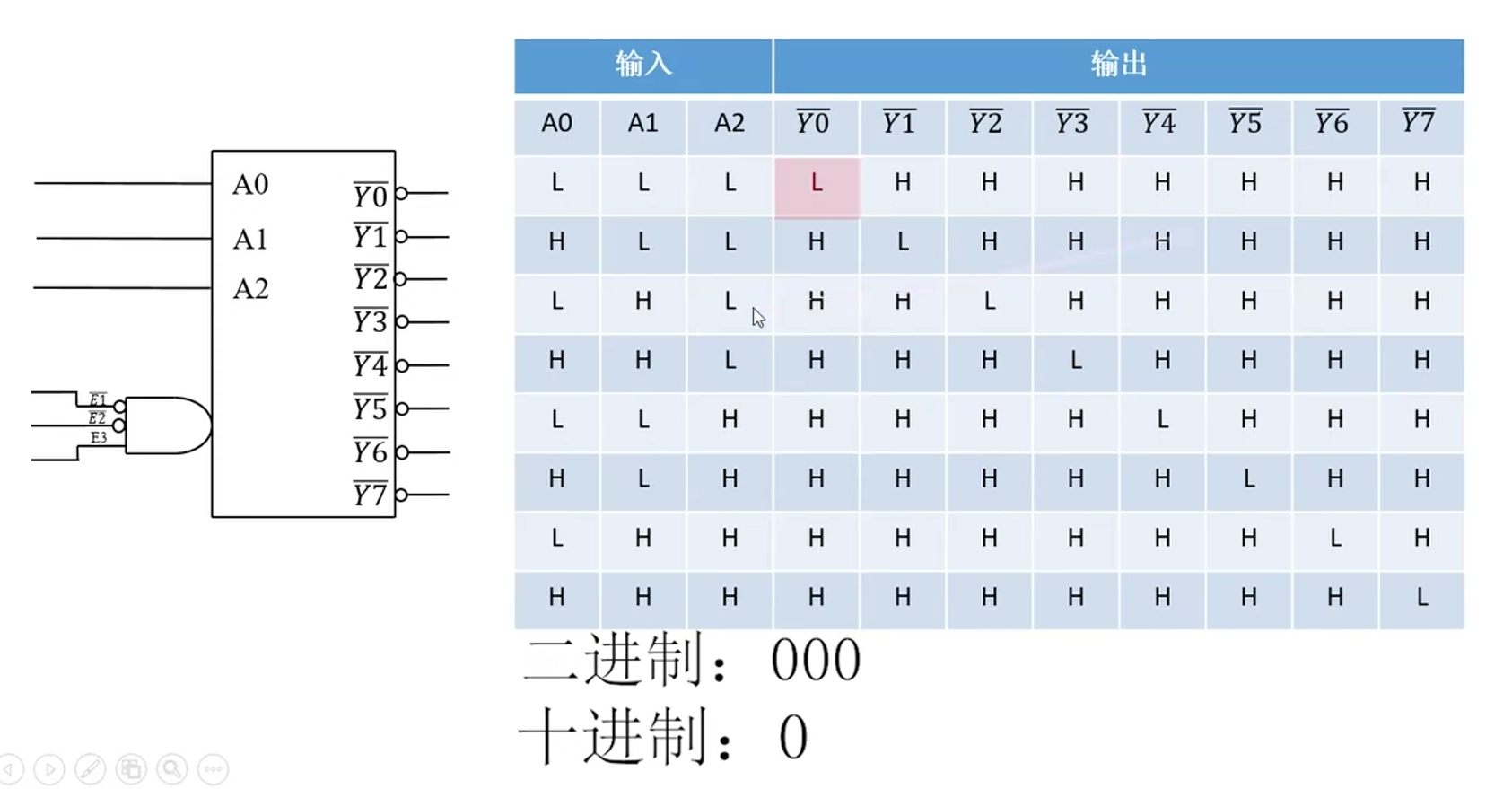

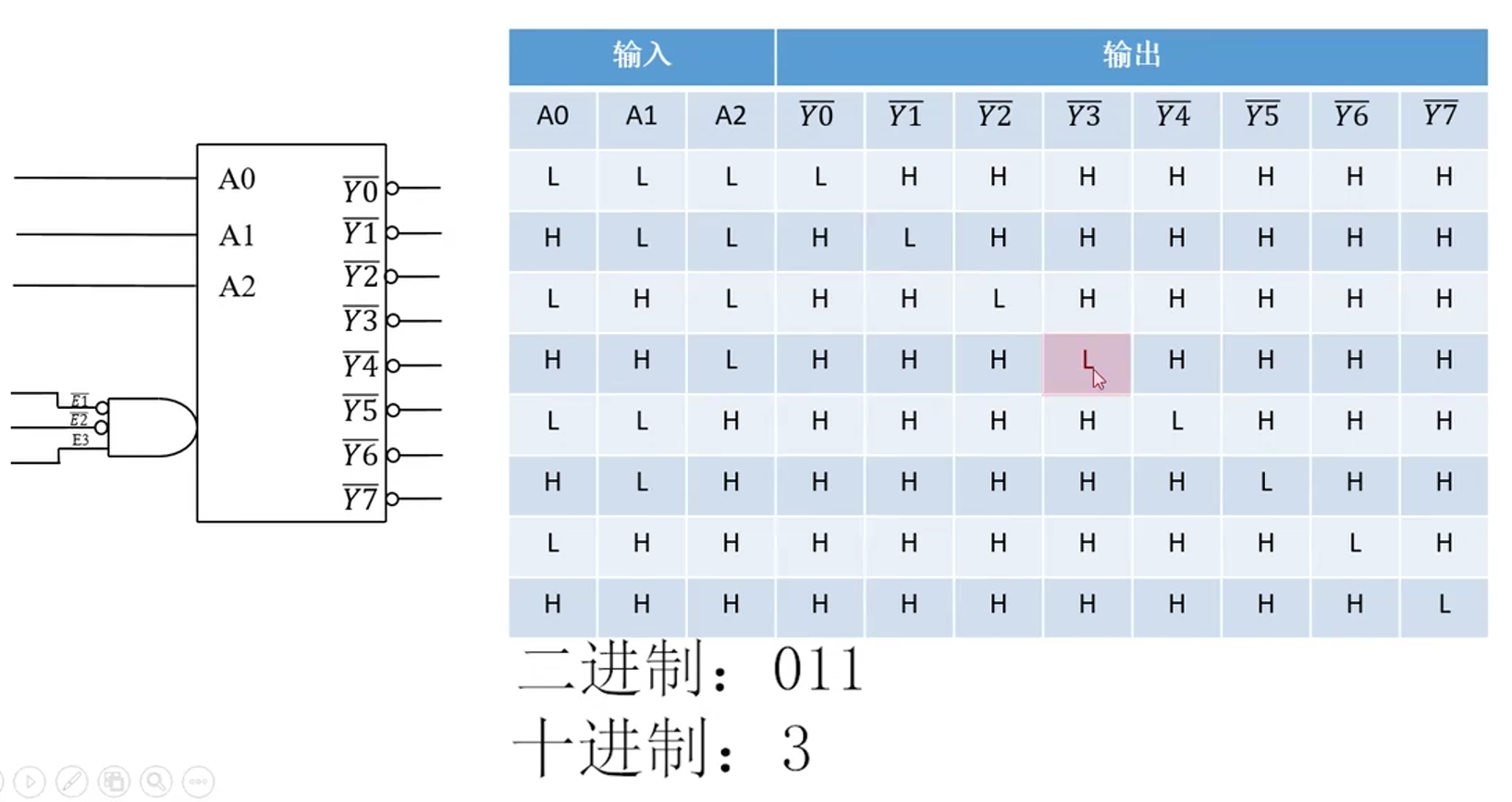

三八译码器,核心功能是通过三个输入端口控制八个输出端口

八位中每次有且仅有一位是高电平,无法实现有两位及两位以上的端口同时输出低电平

二、Verilog输入

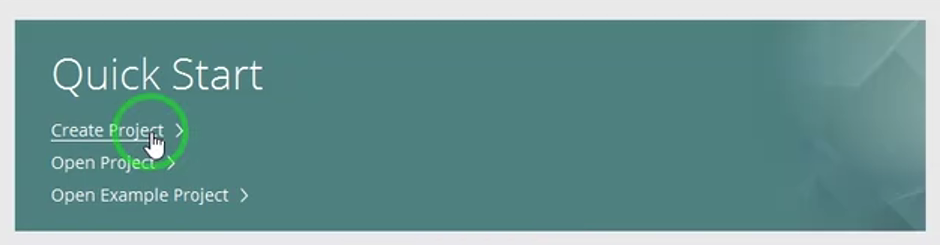

1.创建新工程

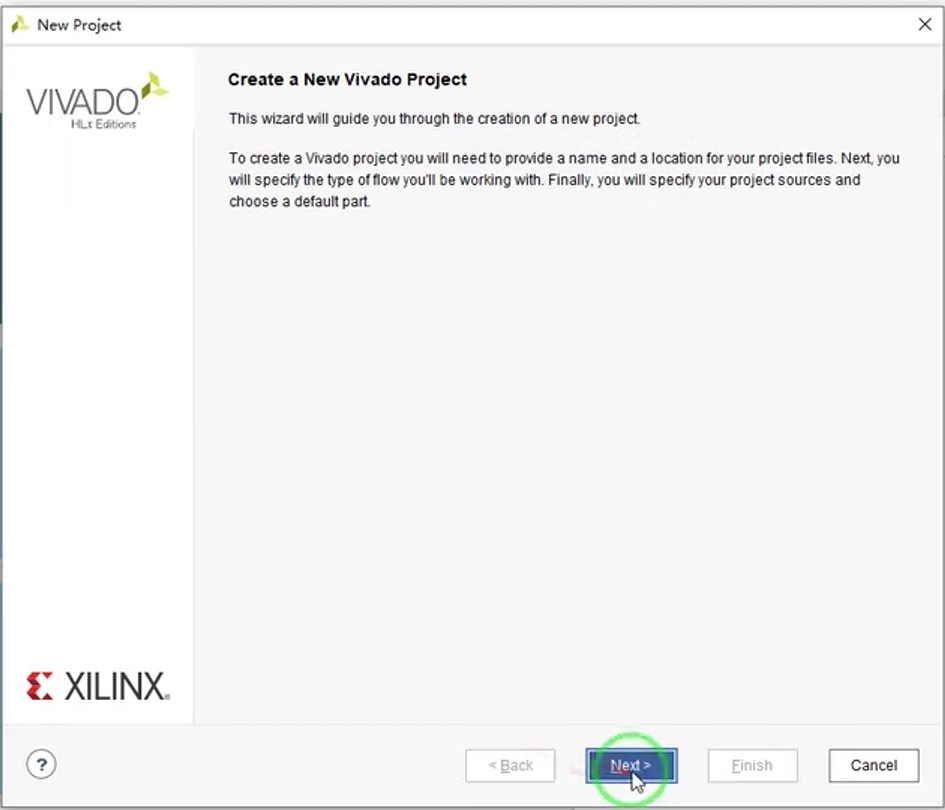

点击Next

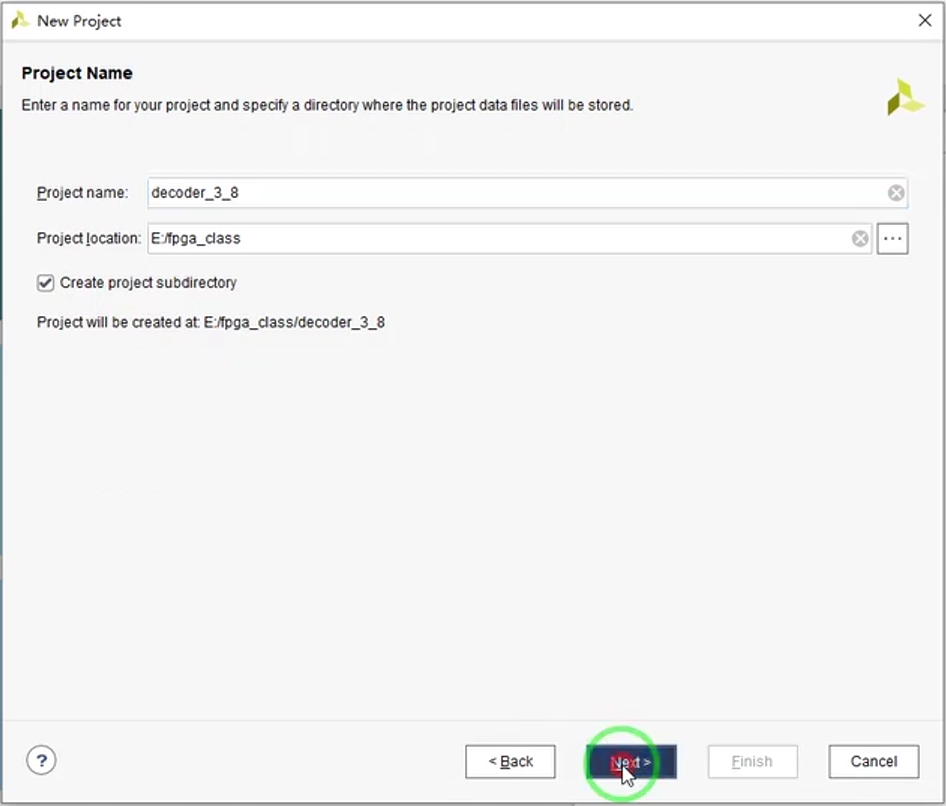

输入工程文件名,选择好保存路径,点击Next

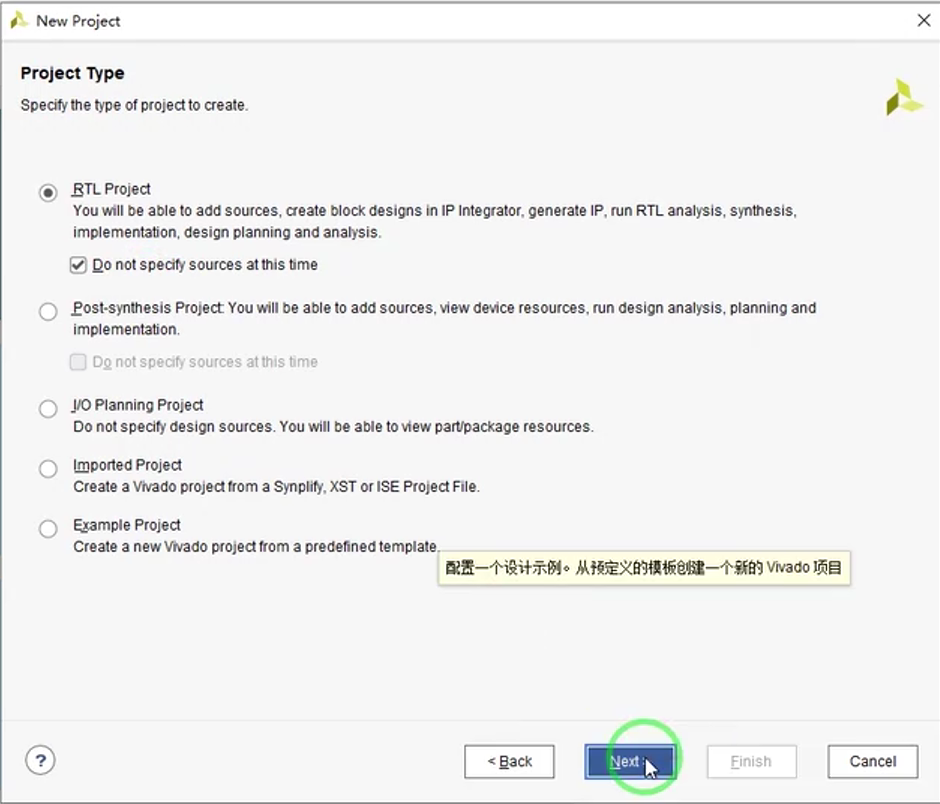

选择第一个并勾选选项,点击Next

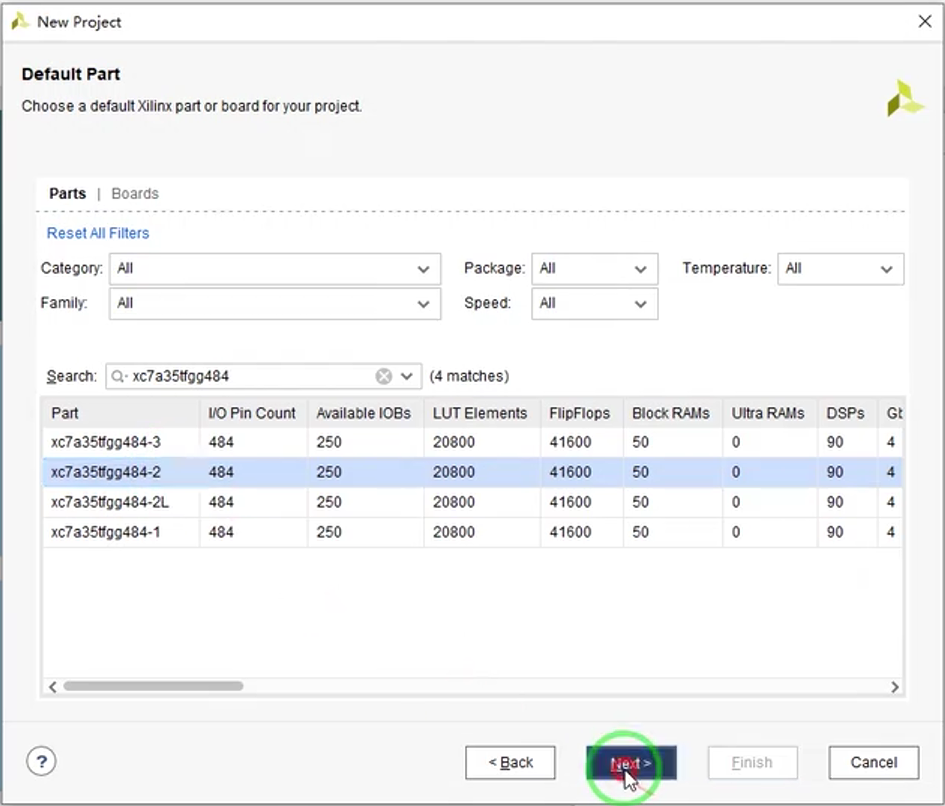

选择好芯片型号后,点击Next

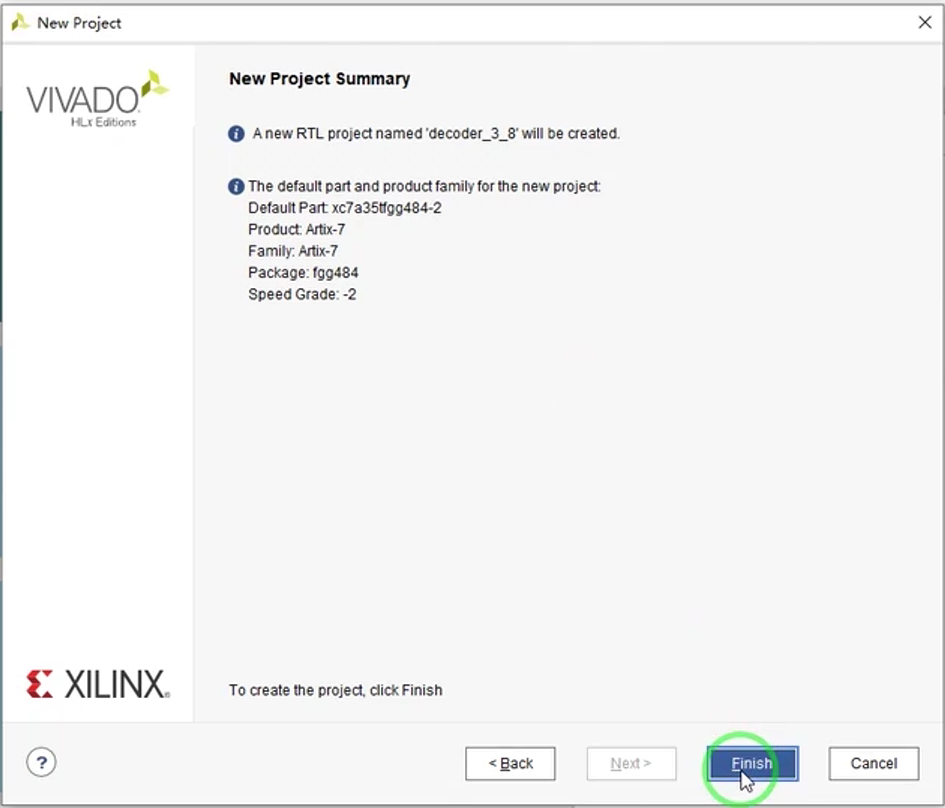

点击Finish

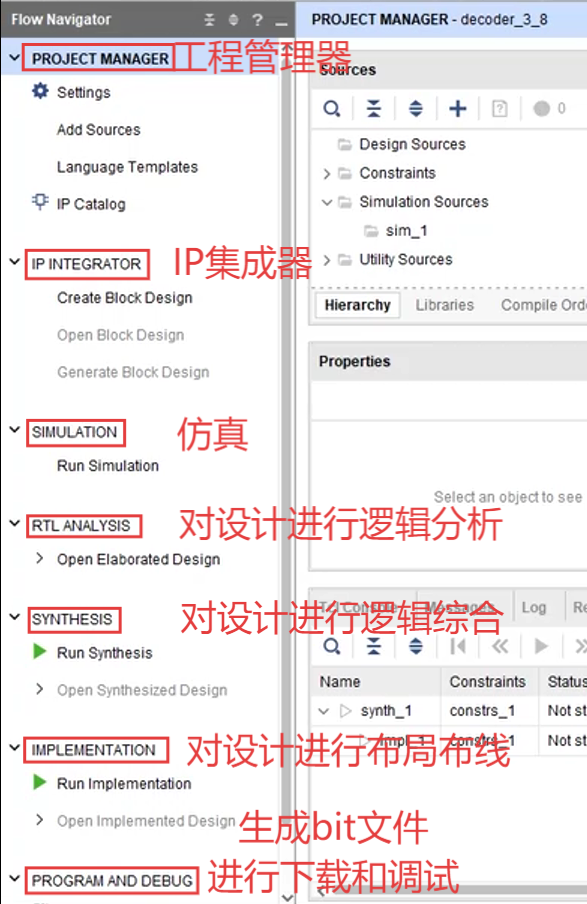

2.设计定义

设计定义就是实现了上面介绍的三八译码器功能,所以这里的设计定义可以忽略,这是已经被定义好的典型功能。

3.设计输入

这里仍使用Verilog语言来进行,也就是用HDL来设计。

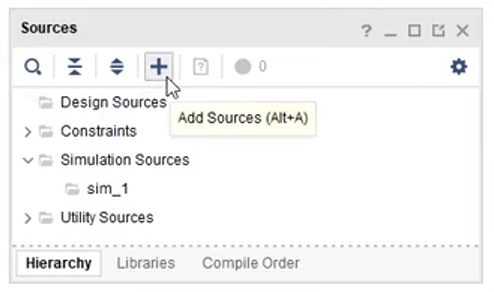

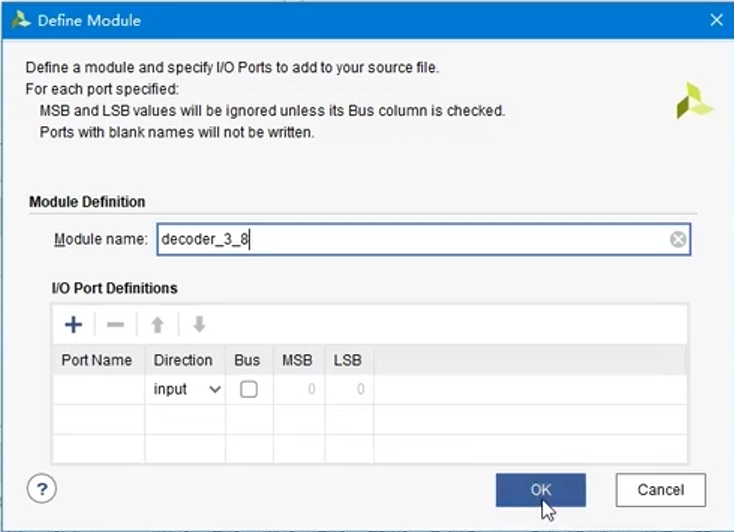

先创建一个Verilog源文件

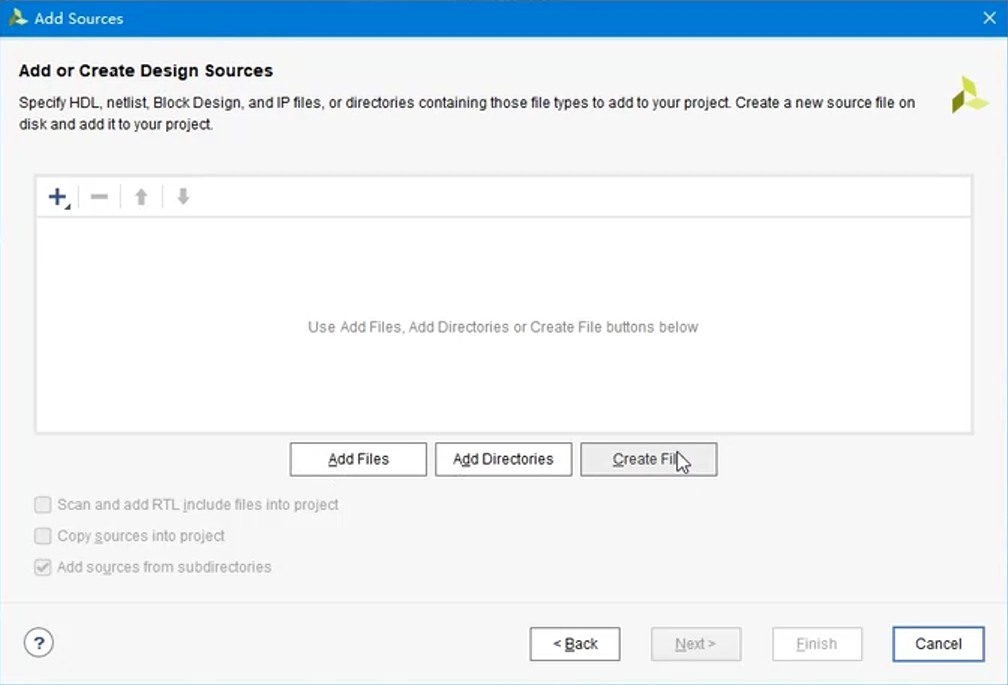

点击加号+或组合键Alt+A

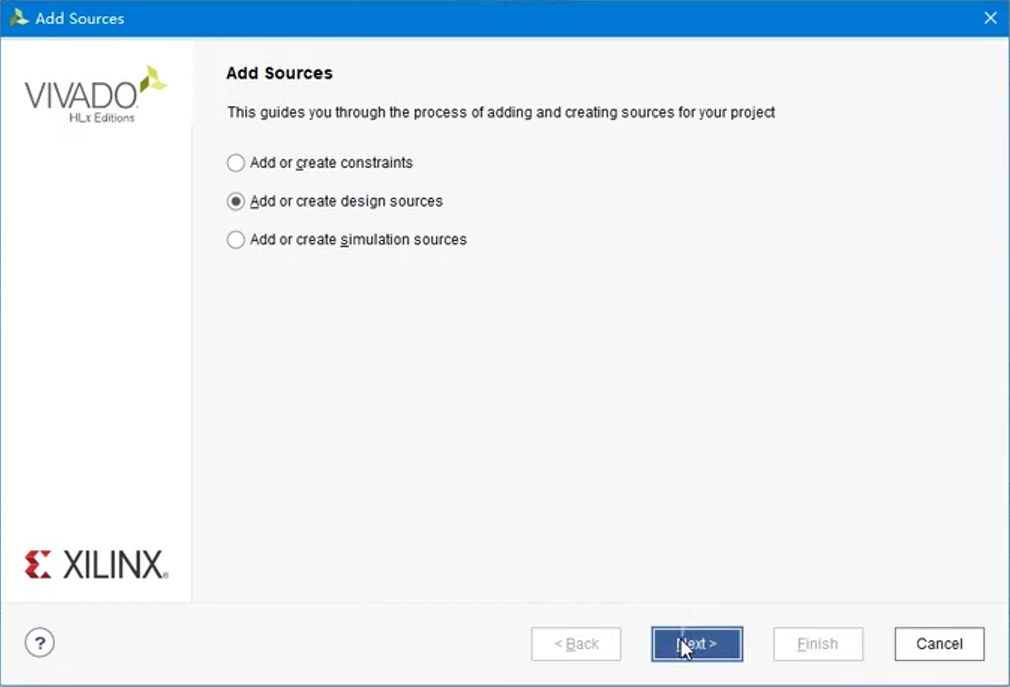

选第二个,点击Next

点击Create File

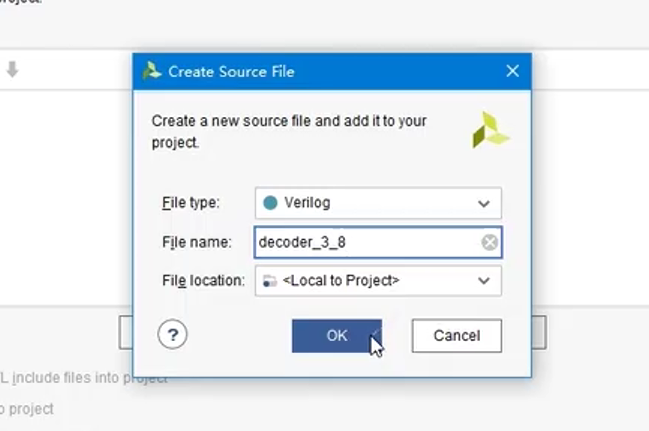

输入文件名称,点击OK

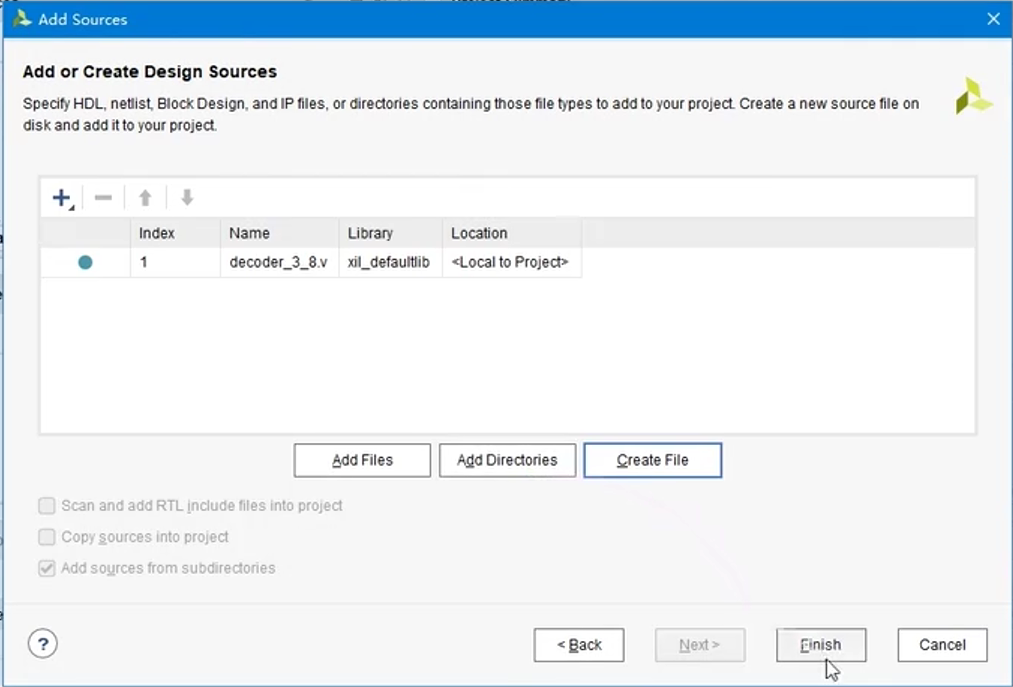

接着点击Finish

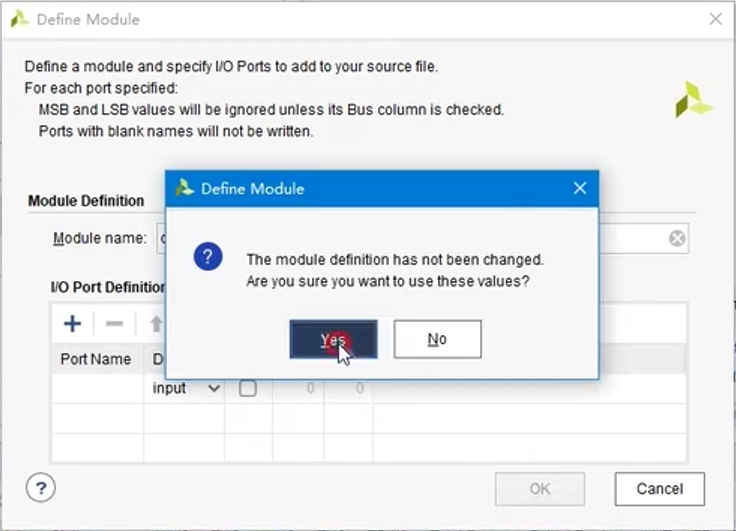

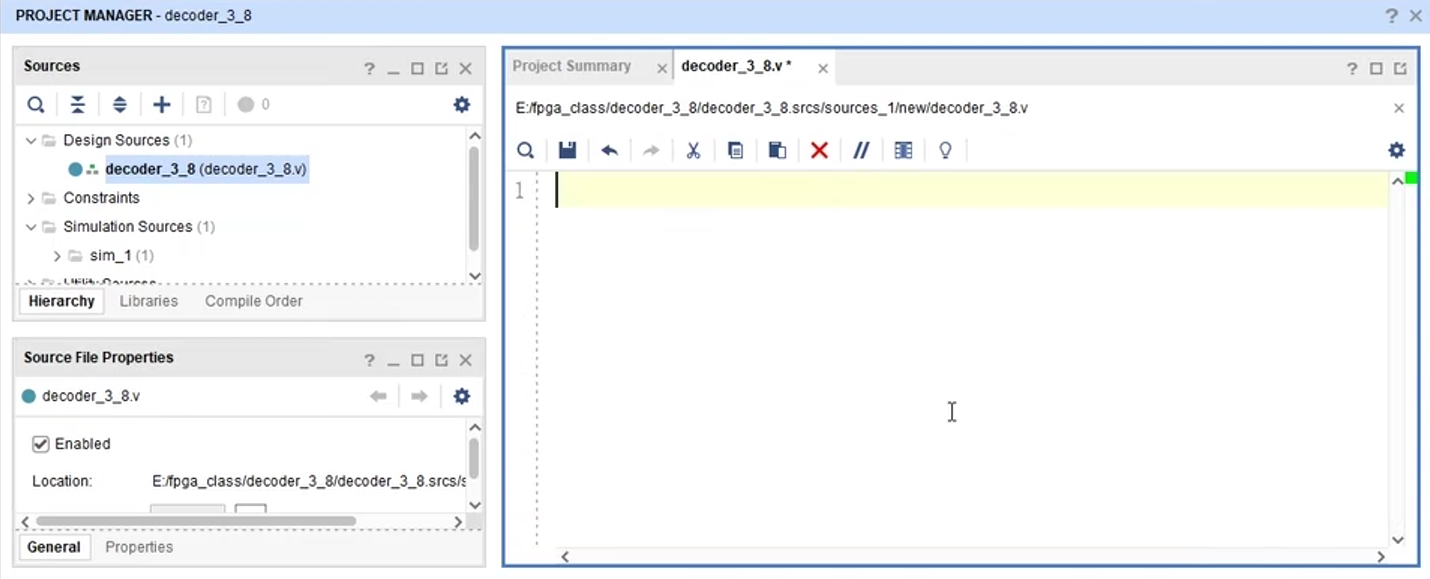

点击OK,点击Yes

打开创建好的文件,删除所有内容

4.程序编写

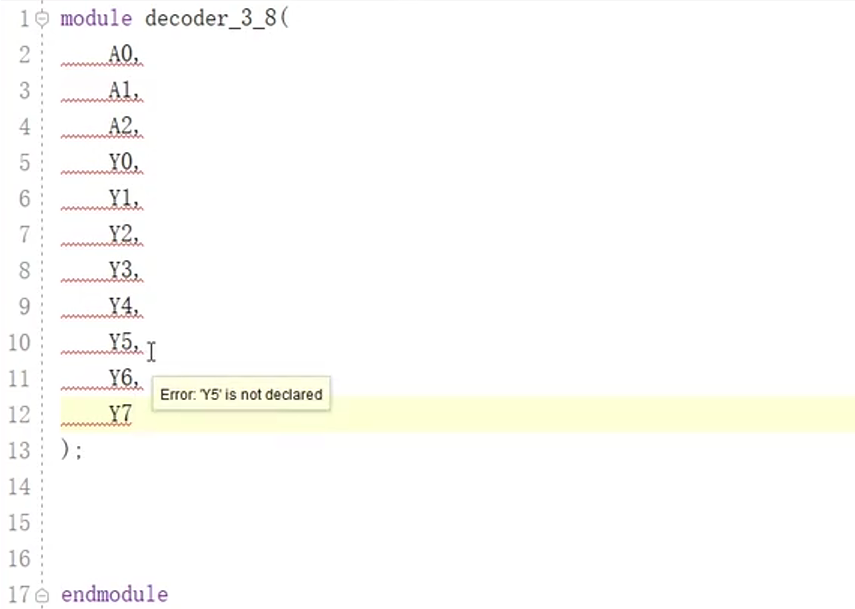

输入module 和endmodule

输入模块名称

写入端口列表(括号后要有分号,每个端口写完用逗号隔开)

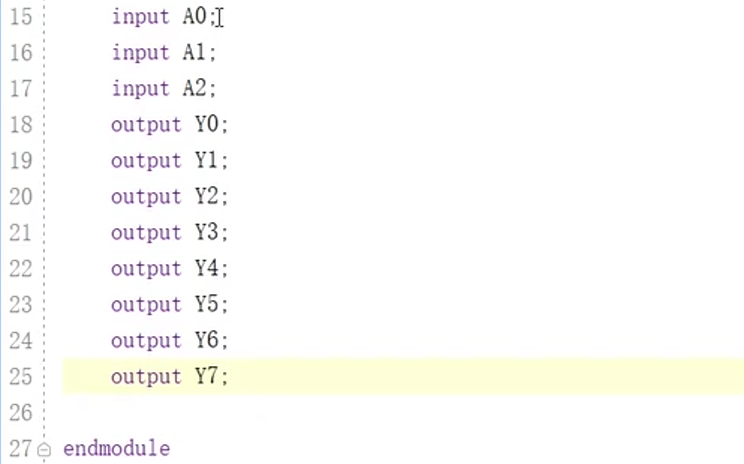

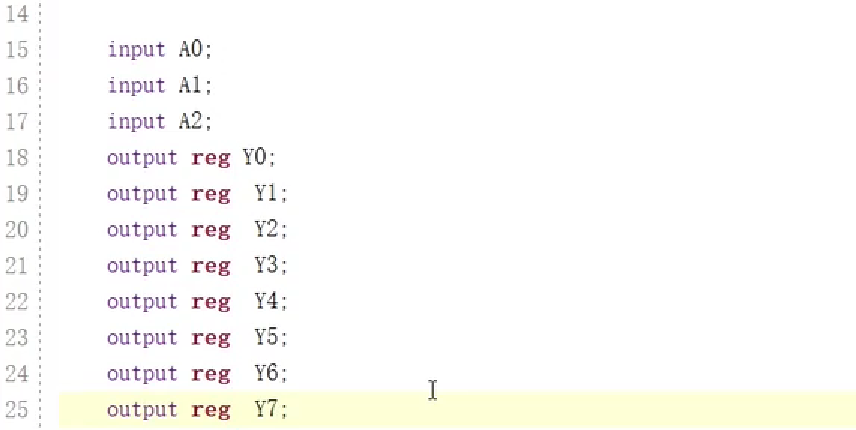

定义端口类型(复制端口列表中的所有端口,粘贴,定义类型后还需将逗号均改为分号)

描述三八译码器的输入和输出逻辑关系

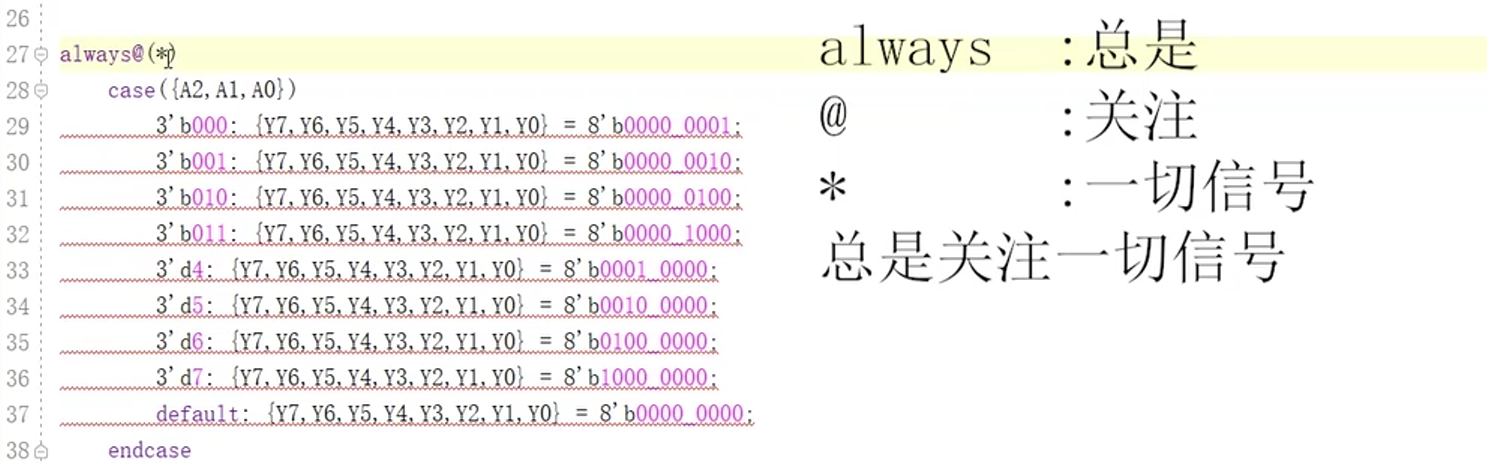

按照上述真值表中的内容,用Verilog语言进行描述

注意:在真值表中的输出端口是经过取非的,而刚才定义的八个输出信号没有经过取反,所以这里写的代码与真值表的三八译码器芯片输出的电平是相反的

always@(*)是过程赋值语句的声明

"一切"表示后续的赋值语句中所有需要进行判断的信号,例如代码中的A2,A1,A0

A2,A1,A0都是单比特信号,即一位的信号,该信号能够表示的值是0或1

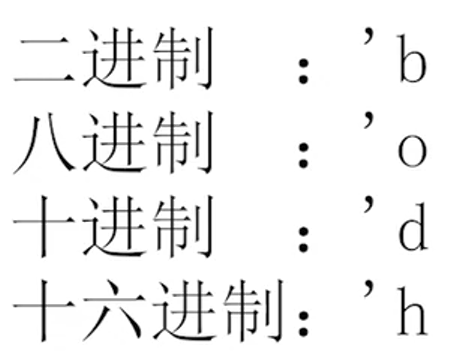

(在Verilog中 8'h5e 与C语言中的0x5e是同一个意思,但在数据类型的表示方式上有细微的区别,C语言用0x表示16进制数,Verilog用 'h 来表示,另外,Verilog在表示数据时,可以在类型前面加上一个数字来表示该数据占多少位宽)

位拼接,{A2,A1,A0}代表将A2,A1,A0的值按照从左到右的顺序依次拼接,得到一个新的三位位宽的信号

case 表示判断,判断括号里内容的值是多少,该代码中列出了八种情况,每个情况后面跟着一个冒号,冒号后面的内容是该情况下需要执行的具体操作,也就是赋值,这里也使用了位拼接的语法,占位符_是为了使代码更容易读懂,没有实际意义

case结束后需要有endcase 表示该语法块的结束

如果代码中没有将case括号中的所有可能出现的值全部列举出来,则还需要使用一个default来指明,在未列举出来的情况下,被赋值对象应该为什么值,避免程序因为时序异常出现未列举出的值的情况时,将被赋值对象赋上不可预料的值

在Verilog中用什么进制来表示一个数并不会改变这个值本身的内容,具体使用哪种表示方式需要根据实际情况而定

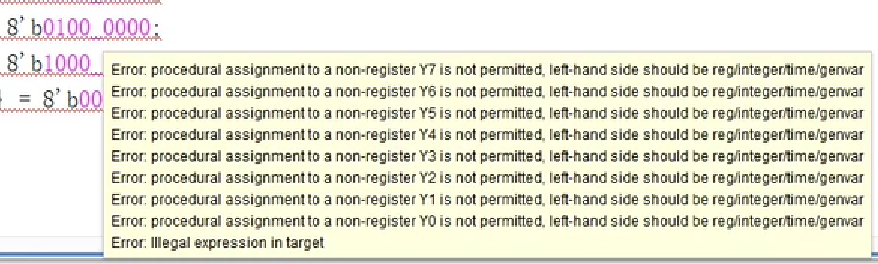

这里出现的错误是说,在always块中向非寄存器类型 或reg型 的信号上赋值是语法所不允许的

也就是说对Y0到Y7在过程赋值语句中赋值了,这些信号就必须被定义为reg类型

凡是在包括always这种过程块中语句中被赋值的信号都需要定义为reg类型

直接在端口定义时,在output后加reg 就可以了

5.对设计进行分析

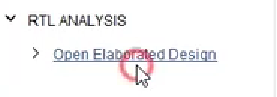

点击Open Elaborated Design

点击OK

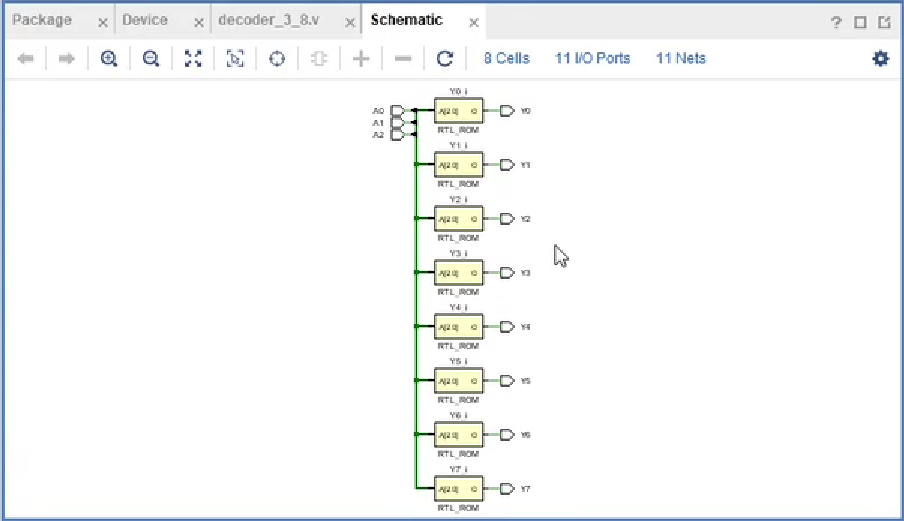

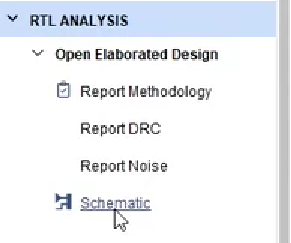

打开Schematic

可以看到所生成的三八译码器不像二选一多路器能够看到一个典型的二选一多路器的数字逻辑模型,这是因为二选一多路器属于数字逻辑电路中的基本单元,而三八译码器更为复杂,软件本身是没有三八译码器模型的,所以只能将三八译码器分解后再进行显示。