- FPGA开发板 : Genesys2

- USB转串口线 : CMSIS-DAP

- CPU主频90MHz,串口波特率115200bps

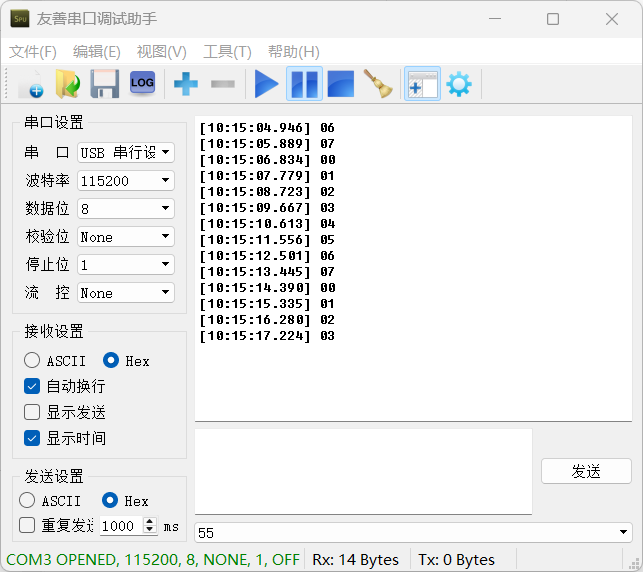

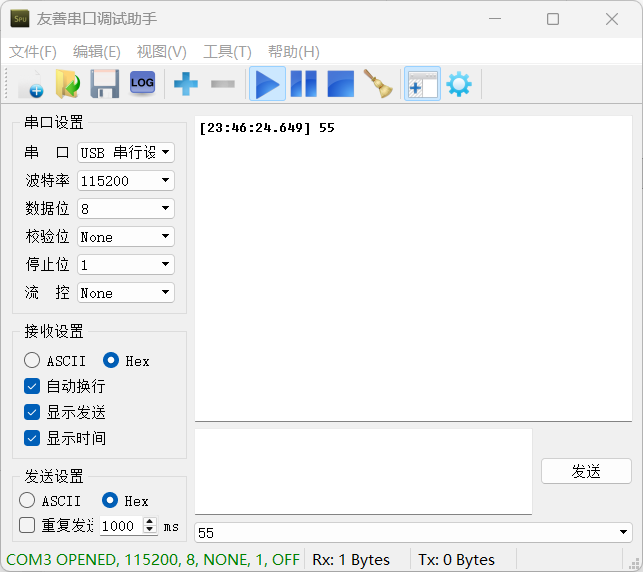

串口参数设置:

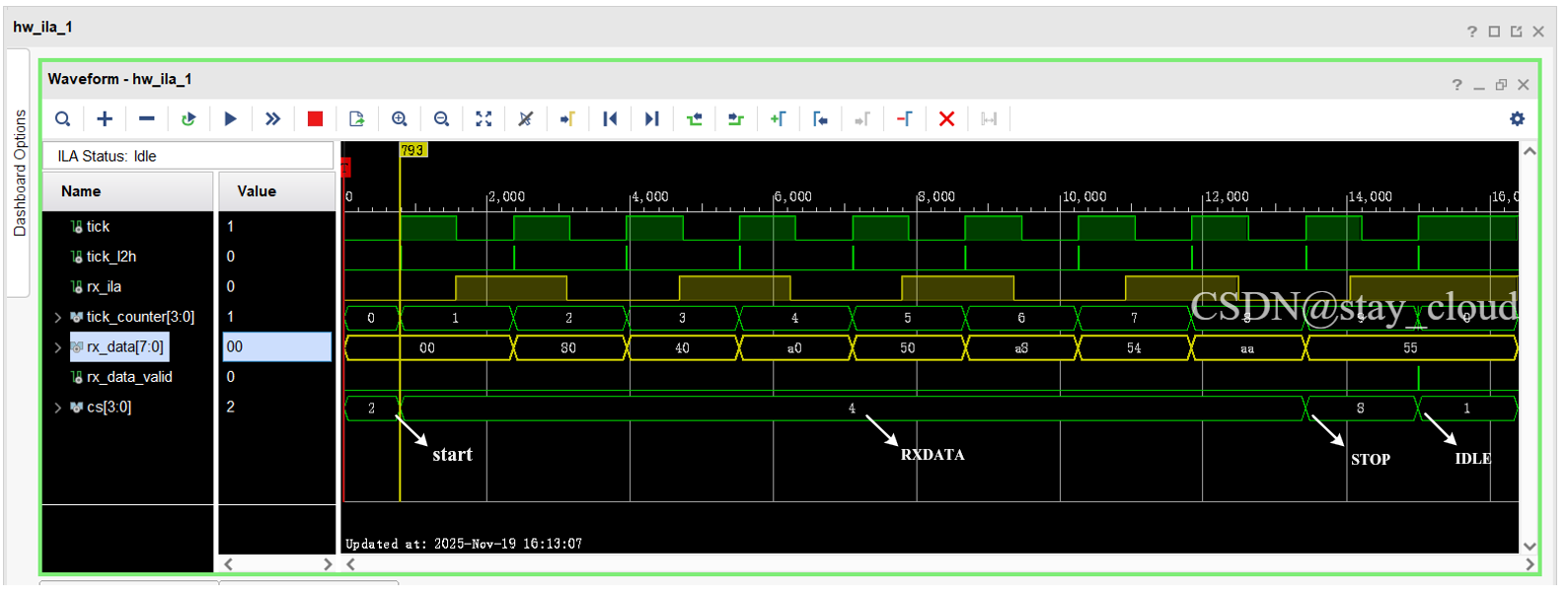

对于115200波特率,发送一位的时间为1/115200=8680ns,对于100MHz主频为868个时钟周期,对于90MHz主频约为781个时钟周期,这里设置baudrate计数最大值为781,计数每达该值时波特率时钟tick进行翻转,在tick上升沿采样(rx)或发送(tx)数据。

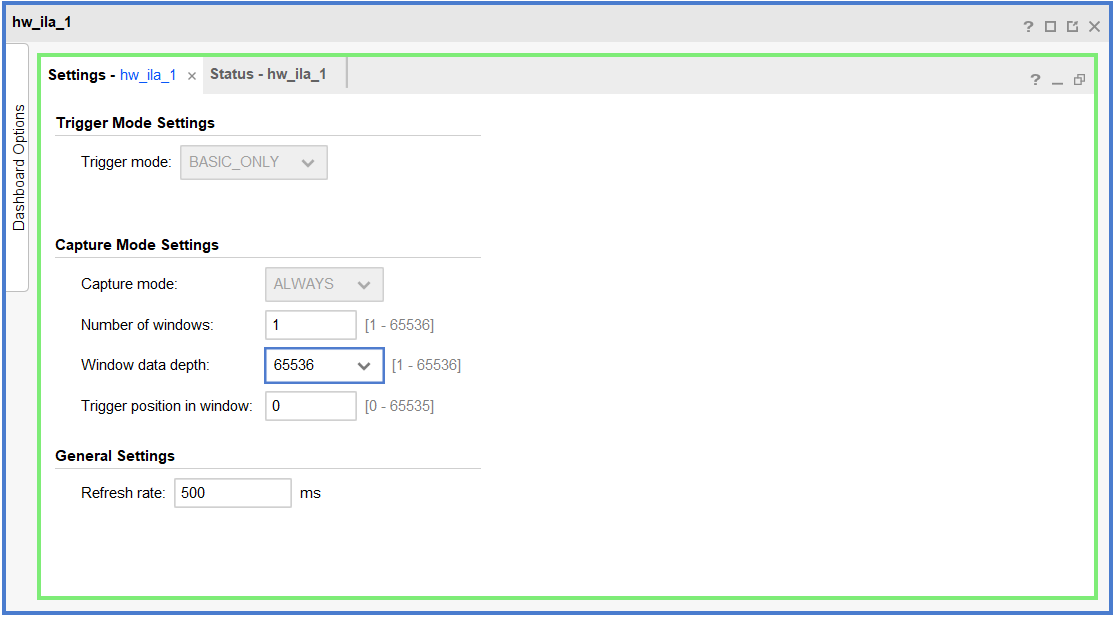

使用ILA观察信号:

可参考:【RISC-V Debug】学习笔记(三)借助 ILA 在线查看调试信号-icspec

在Settings窗口设置采样深度,并设置触发条件为 rx != 1:

- 串口向CPU发送数据0x55,CPU在tick上升沿采样并接收数据:

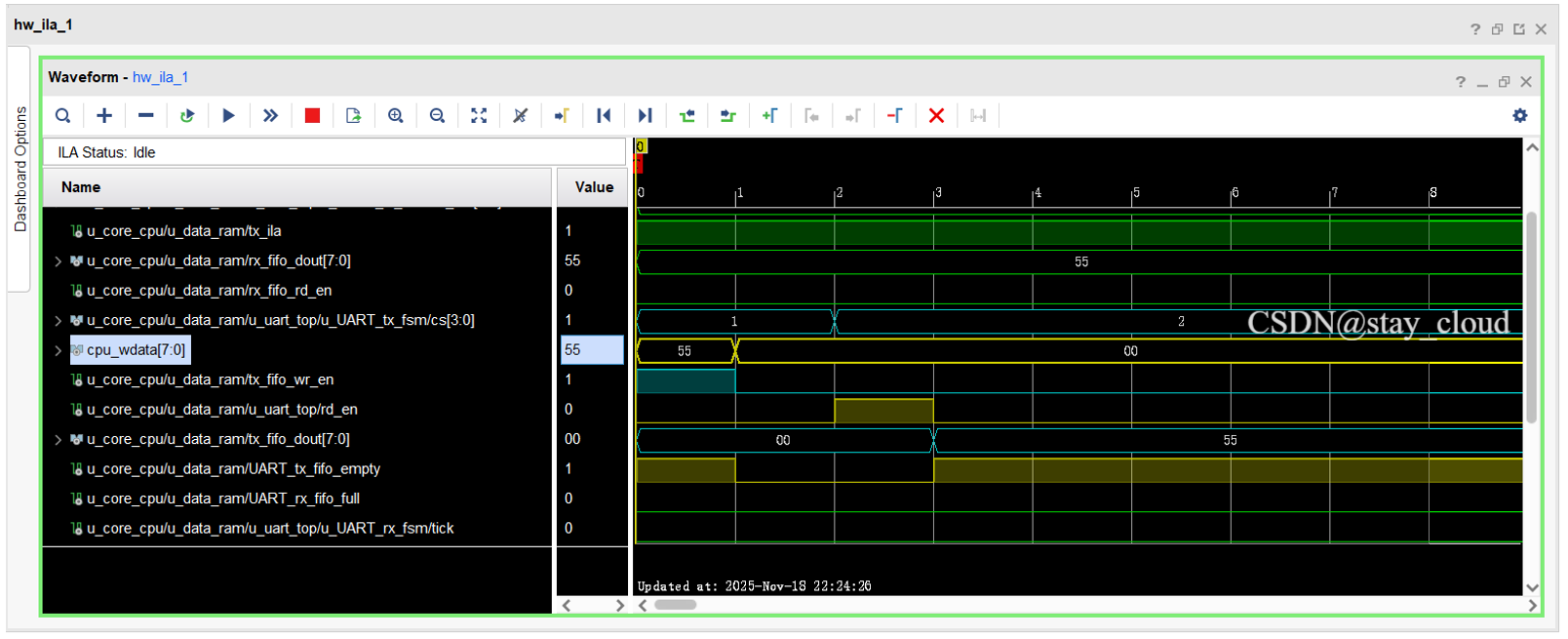

- CPU向串口发送数据,对tx_fifo发起写使能,给出写数据,检测到fifo非空后,tx_fifo读出数据:

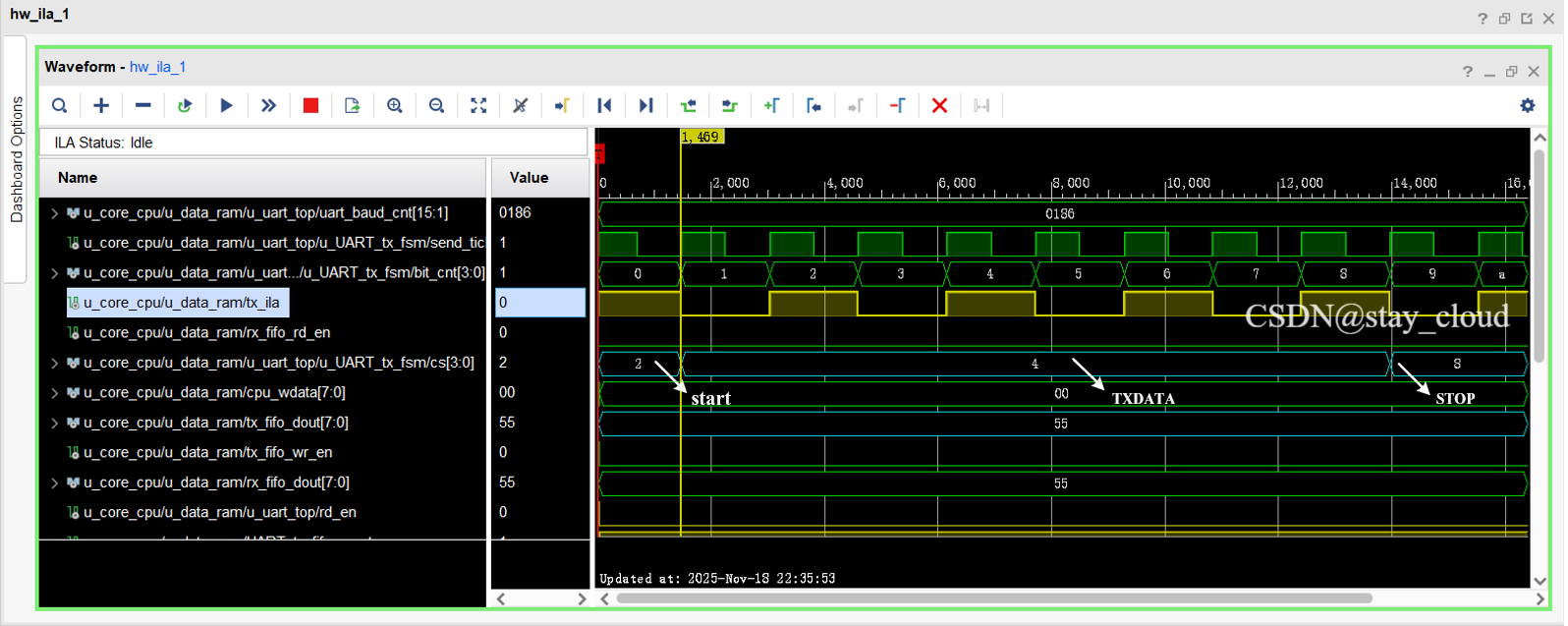

tx_fsm开始发送数据:

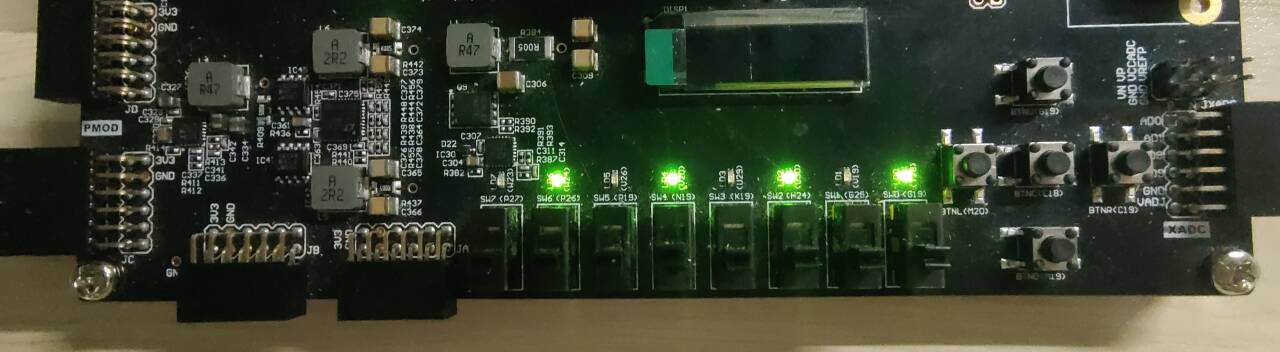

上板测试:

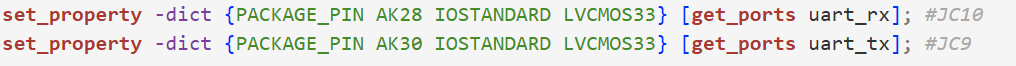

Genesys2开发板集成了uart的micro-USB接口,但是和我的电脑不太兼容,因此选择了JC9和JC10管脚作为tx和rx :

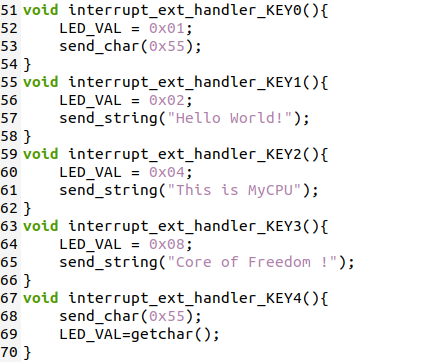

按键的中断服务函数如下,CPU目前共有五个外部中断:

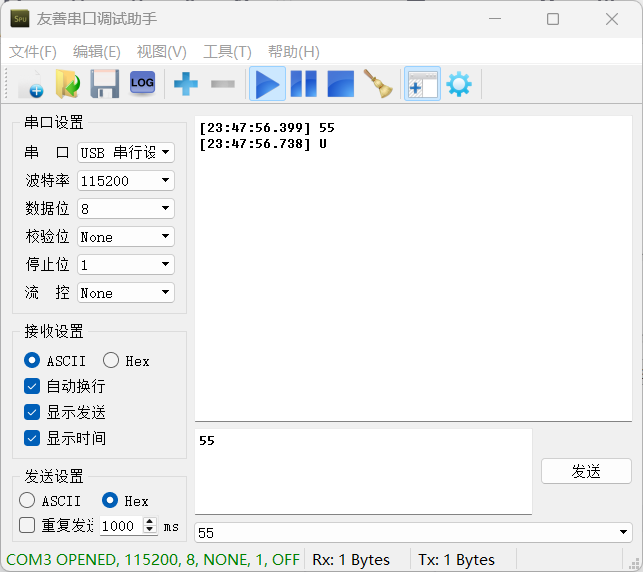

- 按下KEY0,CPU向串口发送数据 0x55 (Hex显示),若为ASCII,则接收数据为字符U(十六进制0x55对应的ASCII码) :

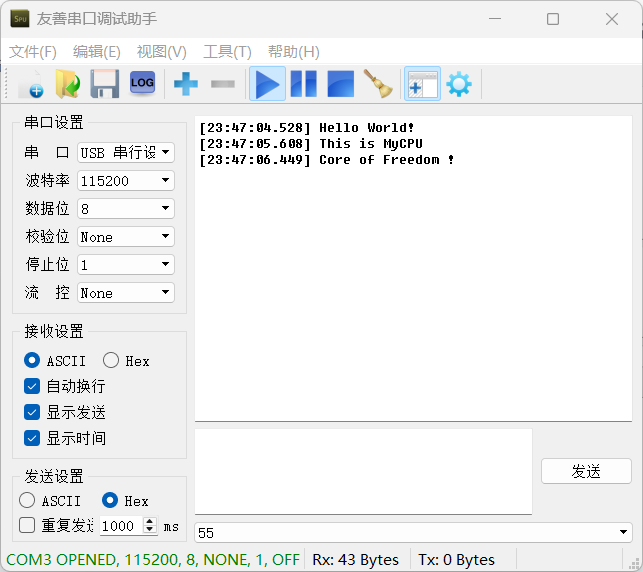

- 将接收设置改为ASCII,依次按下KEY1、KEY2,KEY3,CPU向串口发送字符串:

- 串口向CPU发送hex数据0x55,按下KEY4,LED显示CPU接收到的数据:

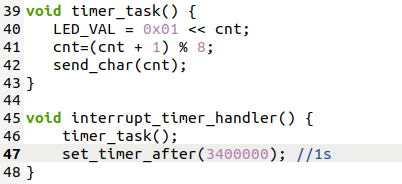

定时器中断的ISR如下,每隔1s触发一次定时器中断,向串口发送LED的当前位置:

串口接收数据如图所示,cnt从0到7循环,且间隔约为1秒: