高性能伺服驱动,纯verilog语言编写,FPGA电流环,包含坐标变换,电流环,速度环,位置环,电机反馈接口,SVPWM,编码器协议,电流环和编码器协议全部在FPGA中实现的,具有很大的参考学习意义。

在硬件开发的领域中,高性能伺服驱动一直是一个令人瞩目的话题。今天就来聊聊用纯Verilog语言在FPGA上实现的高性能伺服驱动,这里面涉及到诸多关键模块,包括FPGA电流环、坐标变换、速度环、位置环、电机反馈接口、SVPWM以及编码器协议,而且电流环和编码器协议完全在FPGA中实现,对于想深入学习相关技术的朋友,有着极大的参考价值。

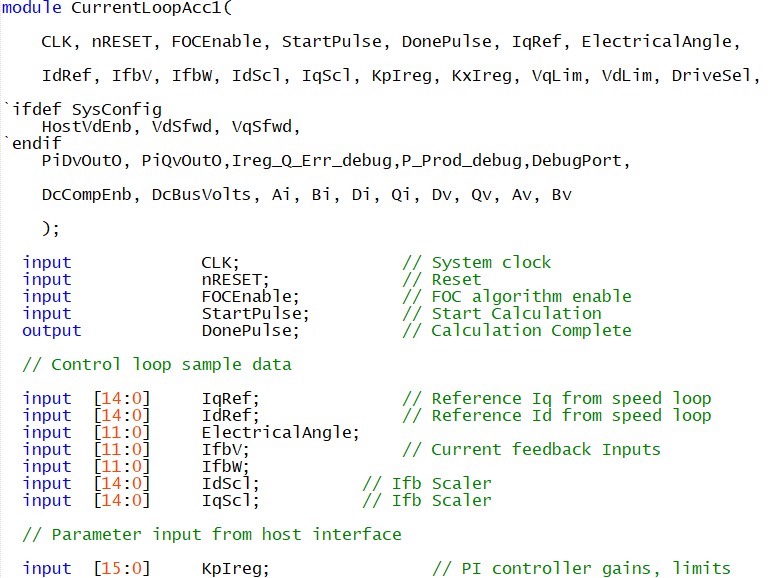

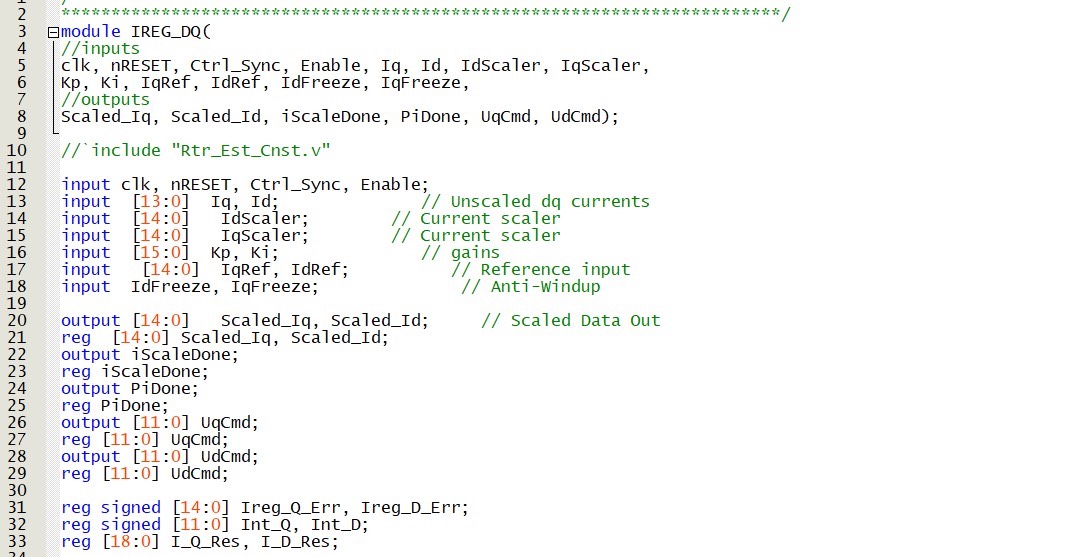

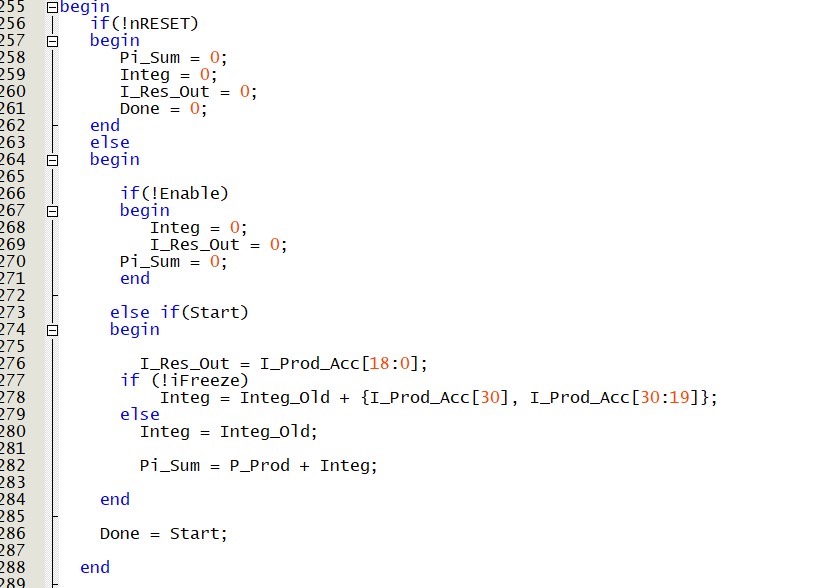

FPGA电流环

电流环在整个伺服驱动系统中起着至关重要的作用,它能够快速响应电流的变化,保证电机的稳定运行。

verilog

module current_loop (

input wire clk,

input wire rst,

input wire [15:0] current_ref,

input wire [15:0] current_fb,

output reg [15:0] voltage_out

);

reg [15:0] error;

always @(posedge clk or posedge rst) begin

if (rst) begin

error <= 16'b0;

voltage_out <= 16'b0;

end else begin

error = current_ref - current_fb;

// 简单的比例控制示例,实际可能需要更复杂的PI控制

voltage_out = error * 16'd10;

end

end

endmodule在这段代码中,currentloop**模块接收时钟信号clk、复位信号rst、电流参考值current ref和电流反馈值currentfb*。通过计算两者的差值error,然后基于简单的比例控制算法(实际应用中多采用PI控制),得到输出电压voltage* out,以此来调整电机的电流。

坐标变换

坐标变换是将电机在不同坐标系下的物理量进行转换,便于控制。常见的是从三相静止坐标系(ABC坐标系)转换到两相旋转坐标系(dq坐标系)。

verilog

module coordinate_transformation (

input wire clk,

input wire rst,

input wire [15:0] ia,

input wire [15:0] ib,

input wire [15:0] ic,

output reg [15:0] id,

output reg [15:0] iq

);

reg [15:0] alpha;

reg [15:0] beta;

always @(posedge clk or posedge rst) begin

if (rst) begin

alpha <= 16'b0;

beta <= 16'b0;

id <= 16'b0;

iq <= 16'b0;

end else begin

alpha = ia;

beta = (2 * ib + ic) / 3;

// 假设已知转子角度theta,这里简单模拟,实际需获取准确角度

reg [15:0] cos_theta = 16'd10000;

reg [15:0] sin_theta = 16'd0;

id = alpha * cos_theta + beta * sin_theta;

iq = -alpha * sin_theta + beta * cos_theta;

end

end

endmodule在上述代码里,首先通过简单的运算将ABC坐标系下的电流ia、ib、ic转换到静止的αβ坐标系下,得到alpha和beta。然后结合假设的转子角度(实际应用需准确测量),将αβ坐标系下的量进一步转换到旋转的dq坐标系下,得到id和iq,为后续的控制提供基础。

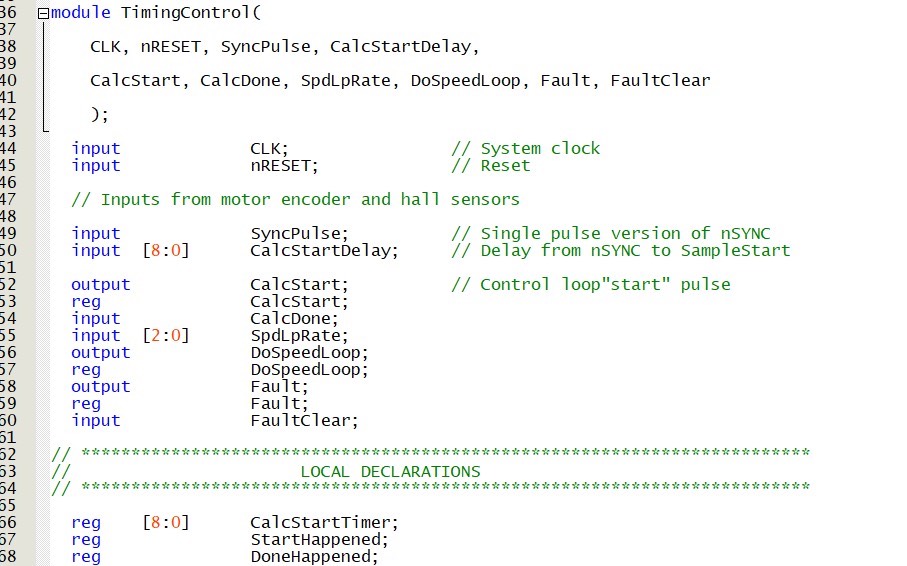

速度环与位置环

速度环和位置环用于实现对电机速度和位置的精确控制,这两个环通常基于比例积分微分(PID)控制算法。

verilog

module velocity_loop (

input wire clk,

input wire rst,

input wire [15:0] velocity_ref,

input wire [15:0] velocity_fb,

output reg [15:0] current_ref

);

reg [15:0] error;

reg [15:0] integral;

always @(posedge clk or posedge rst) begin

if (rst) begin

error <= 16'b0;

integral <= 16'b0;

current_ref <= 16'b0;

end else begin

error = velocity_ref - velocity_fb;

integral = integral + error;

// 简单的PID示例,实际需调整参数

current_ref = error * 16'd10 + integral * 16'd1;

end

end

endmodule

module position_loop (

input wire clk,

input wire rst,

input wire [15:0] position_ref,

input wire [15:0] position_fb,

output reg [15:0] velocity_ref

);

reg [15:0] error;

reg [15:0] integral;

always @(posedge clk or posedge rst) begin

if (rst) begin

error <= 16'b0;

integral <= 16'b0;

velocity_ref <= 16'b0;

end else begin

error = position_ref - position_fb;

integral = integral + error;

velocity_ref = error * 16'd10 + integral * 16'd1;

end

end

endmodule在velocityloop**模块中,通过比较速度参考值velocity ref和速度反馈值velocityfb**得到误差error,并对误差进行积分integral,结合简单的PID算法得到电流参考值current ref,为电流环提供输入。而positionloop**模块类似,通过比较位置参考值position ref和位置反馈值positionfb*,经PID运算得到速度参考值velocity* ref,传递给速度环。

电机反馈接口与编码器协议

电机反馈接口负责接收电机编码器反馈的信息,编码器协议则定义了如何解析这些信息。

verilog

module encoder_interface (

input wire clk,

input wire rst,

input wire encoder_a,

input wire encoder_b,

output reg [31:0] position

);

reg encoder_a_last;

reg encoder_b_last;

always @(posedge clk or posedge rst) begin

if (rst) begin

encoder_a_last <= 1'b0;

encoder_b_last <= 1'b0;

position <= 32'b0;

end else begin

if (encoder_a!= encoder_a_last) begin

if (encoder_b!= encoder_a) begin

position = position + 1;

end else begin

position = position - 1;

end

end

encoder_a_last = encoder_a;

encoder_b_last = encoder_b;

end

end

endmodule此encoderinterface**模块通过对编码器的A相和B相信号encoder a、encoder_b进行监测,利用AB相之间的相位关系来判断电机的旋转方向,从而更新电机的位置position。在实际应用中,编码器协议可能更复杂,如绝对值编码器协议等,但这里展示的是基本的增量式编码器解析思路。

SVPWM(空间矢量脉宽调制)

SVPWM用于生成驱动电机的三相PWM波,以实现对电机的高效控制。

verilog

module svpwm (

input wire clk,

input wire rst,

input wire [15:0] valpha,

input wire [15:0] vbeta,

output reg [9:0] pwm_a,

output reg [9:0] pwm_b,

output reg [9:0] pwm_c

);

// 计算扇区等复杂逻辑省略,这里简单模拟

always @(posedge clk or posedge rst) begin

if (rst) begin

pwm_a <= 10'b0;

pwm_b <= 10'b0;

pwm_c <= 10'b0;

end else begin

// 简单根据电压分量生成PWM,实际需复杂计算

pwm_a = valpha[15:6];

pwm_b = vbeta[15:6];

pwm_c = (valpha + vbeta)[15:6];

end

end

endmodule在这个svpwm模块中,根据输入的αβ坐标系下的电压分量valpha和vbeta,简单地生成三相PWM波pwma*、pwm* b、pwm_c。实际的SVPWM算法要复杂得多,需要计算扇区、作用时间等,但这里给出一个基本的实现框架。

通过以上各个模块的协同工作,基于Verilog语言在FPGA上构建起了高性能伺服驱动系统。每个模块都有其独特的功能和作用,相互配合实现对电机精确、高效的控制。希望这篇文章能为你在相关领域的学习和研究带来一些启发。