数字IC经典电路(6)---Ring Oscillator(环形振荡器)与工艺角监控

前言

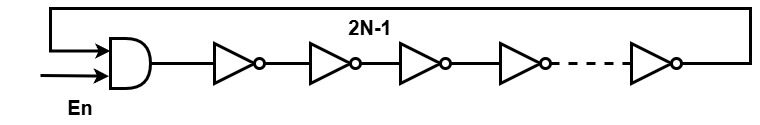

环形振荡器的核心结构非常简单,它由奇数个反相器首尾相连,形成一个闭合的环形正反馈环路。

基本构成:N级反相器串联(N为奇数,如3、5、7...),最后一级的输出直接连接回第一级的输入。

工作原理:

Figure 1: Ring Oscillator

Figure 1: Ring Oscillator

- 假设在某一时刻,某个节点的电压为高电平。

- 这个高电平经过第一个反相器后变为低电平,再经过第二个反相器变为高电平...以此类推。

- 由于反相器的数量是奇数,信号每环绕一圈,其逻辑电平都会发生一次翻转(例如,从高变低)。

- 这种不间断的、自激的翻转过程就产生了周期性的方波振荡。

- 振荡频率:其频率公式可以简化为 Freq = 1 / (2 * N * Td),其中 N 是反相器级数,Td 是每一级反相器的平均延迟时间。

- 级数N越多,频率越低。

7. 延迟Td受电源电压、温度、工艺制程影响很大。

环形振荡器的使用场景

环形振荡器因其结构简单、面积小、可集成度高,在数字IC中有着广泛的应用,但其频率稳定度和精度较差,因此通常不用于需要高精度时钟的场合。

** 主要使用场景包括:**

- 片上时钟生成:

用于对时钟精度要求不高的模块内部时钟,例如某些数字逻辑电路的局部时钟。在系统主时钟启动之前,作为简单的启动时钟。 - 传感器:

温度传感器:利用环形振荡器的振荡频率会随温度变化的特性(由于载流子迁移率变化)。通过测量频率,可以推算出芯片的结温。 - 电源噪声传感器:

将环形振荡器作为"探针",放置在芯片的不同位置,其频率抖动可以反映当地电源网络的稳定性。 - 工艺角监控:

在芯片制造后,由于工艺偏差,不同芯片的速度会有快慢之分(分为快工艺角、典型工艺角、慢工艺角)。通过测试片上环形振荡器的频率,可以快速、非侵入性地判断该芯片属于哪种工艺角,用于芯片分级或内部参数调优。 - 性能测量:

用于测量在特定电压、温度下电路的实际延迟性能,是DVFS(动态电压频率调整)技术中常用的一个辅助电路。

1. 环形振荡器测试结构

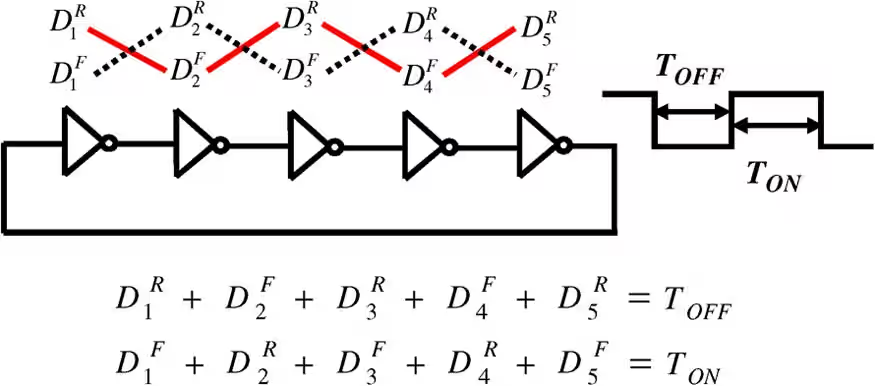

自动化参数测试(APT)系统通过测量环形振荡器测试结构,使测试工程师能够实时监控半导体制造质量并诊断生产问题。环形振荡器测试结构已沿用数十年,至今仍在先进技术的过程监控中发挥关键作用。

为监控制造中的局部工艺变异,芯片设计需引入环形振荡器测试结构。该变异会致使振荡器内各反相器的门延迟产生差异。通过增加反相器级数并计算其平均延迟,可以削弱个别变异的影响,从而提高测量精度。

Figure 2: Ring Oscillator Frequency

Figure 2: Ring Oscillator Frequency

2. 工艺角监控

环形振荡器通过巧妙的结构设计,能够高效、低成本地嵌入芯片内部,实现对半导体制造工艺角的有效监控和诊断。随着技术发展,环形振荡器在工艺角监控方面的应用正朝着更精细的区分能力(如独立监测NMOS/PMOS)、更高的抗环境干扰(如温度补偿)以及更高的面积效率方向演进,持续为提升芯片制造质量和性能稳定性提供关键支持。。

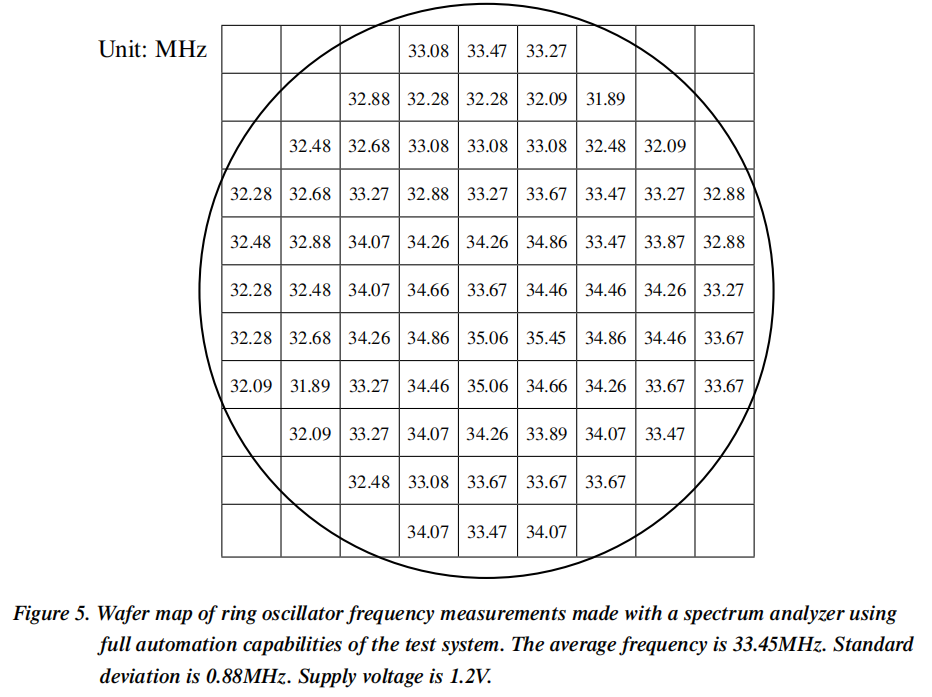

图3显示了跨越整个300mm晶圆的环形振荡器频率测量的晶圆图。整个晶圆的平均振荡频率为33.45MHz,标准偏差为0.88MHz。结果表明了生产晶圆的均匀性。

Figure 3: Wafer map of ring osc

Figure 3: Wafer map of ring osc

环形振荡器在工艺角监控中的应用原理,是利用其振荡频率对晶体管门延迟的高度敏感性,将难以直接测量的微观工艺参数(如载流子迁移率、阈值电压等)转化为易于测量的宏观电学参数(频率)。通过将实测频率与基于工艺角模型的仿真预期进行比对,即可快速、有效地判断芯片制造的工艺角,为芯片的性能分级、良率分析和可靠性评估提供关键数据。

3. 核心工艺角简介

在先进的集成电路设计中,为了更精确地覆盖制造变异,工艺角模型从基本的五个(TT, FF, SS, FS, SF)扩展到了更完整的九个。这九个角是通过将NMOS和PMOS分别固定在三种状态(Typical, Fast, Slow),并组合另一管的典型值而得到的,它们构成了一个更全面的二维工艺变异空间。

下表详细列出了这九个工艺角:

| 工艺角 | NMOS 状态 | PMOS 状态 | 别称/描述 | 主要特征与影响 |

|---|---|---|---|---|

| TT | Typical | Typical | 典型角 | 设计的中心目标。所有参数均为标称值,代表在理想制造条件下的性能。 |

| FF | Fast | Fast | 全局快角 | 所有晶体管速度都快。导致: • 最高性能 (频率) • 最大功耗 (静态和动态) • 最严格的保持时间检查场景 |

| SS | Slow | Slow | 全局慢角 | 所有晶体管速度都慢。导致: • 最低性能 (频率) • 最低功耗 (静态) • 最严格的建立时间检查场景 |

| FS | Fast | Slow | 混合角 | NMOS快,PMOS慢。导致: • 下降沿快,上升沿慢 • 对PMOS负载电路性能影响大 • 关键用于检查传输门、特定逻辑门的时序 |

| SF | Slow | Fast | 混合角 | NMOS慢,PMOS快。导致: • 上升沿快,下降沿慢 • 对NMOS负载电路性能影响大 • 关键用于检查传输门、特定逻辑门的时序 |

| FT | Fast | Typical | NMOS快角 | NMOS速度快,PMOS为典型值。导致: • NMOS相关的下拉路径变快 • 用于分析NMOS主导电路的性能边界 |

| ST | Slow | Typical | NMOS慢角 | NMOS速度慢,PMOS为典型值。导致: • NMOS相关的下拉路径变慢 • 用于分析NMOS主导电路的性能边界 |

| TF | Typical | Fast | PMOS快角 | PMOS速度快,NMOS为典型值。导致: • PMOS相关的上拉路径变快 • 用于分析PMOS主导电路的性能边界 |

| TS | Typical | Slow | PMOS慢角 | PMOS速度慢,NMOS为典型值。导致: • PMOS相关的上拉路径变慢 • 用于分析PMOS主导电路的性能边界 |

4. 工艺角深入解析与应用场景

- TT - 典型角

TT角是所有设计和仿真的参考基准点。它代表了工艺参数的标称值,是SPICE模型中最精确、最接近设计目标的点。然而,在实际制造中,几乎没有任何芯片会精确地落在TT角上,它更像是一个统计中心值。

应用场景:

功能验证:作为初始设计和功能仿真的首选环境。

性能基准:用于建立芯片性能(频率、功耗)的黄金参考。

学术研究:在比较不同电路架构时,提供一个公平的、标准的比较平台。 - FF - 全局快角

FF角模拟了最乐观的制造结果,通常由较低的晶体管阈值电压和较高的载流子迁移率导致。这会导致更小的门延迟和更高的漏电流。在此角下,芯片动态功耗和静态功耗都达到峰值。

应用场景:

保持时间检查:这是分析保持时间违例的最关键场景。因为数据路径延迟最小,数据可能过早地到达下一个寄存器,破坏其保持时间。

峰值功耗分析:用于评估电源网络和封装能否承受最坏情况下的电流需求。

可靠性分析:评估电迁移和热效应在最坏功耗条件下的影响。 - SS - 全局慢角

SS角模拟了最悲观的制造结果,通常由较高的阈值电压和较低的迁移率导致。此角下,电路速度最慢,但静态功耗最低。它是决定芯片最高工作频率的关键角。

应用场景:

建立时间检查:这是分析建立时间违例的最关键场景。因为时钟路径和数据路径延迟都最大,数据可能无法在下一个时钟沿之前稳定建立。

最低性能保障:用于定义芯片产品规格中的最低工作频率。

低功耗模式验证:由于静态功耗最低,常用于验证深度休眠模式下的功耗是否满足要求。 - FS - 快NMOS/慢PMOS角

此角反映了NMOS和PMOS工艺步骤独立变异的不对称性。它导致电路的下拉能力强于上拉能力。对于以PMOS为上拉管的电路路径,其性能会显著恶化。

应用场景:

传输门:传输门由NMOS和PMOS并联。在FS角下,NMOS导通良好,但PMOS导通很差,可能导致高电平无法有效传输,造成逻辑电平退化。

PMOS主导路径:对于上拉网络由PMOS构成的电路(如某些与门、或非门),此角会暴露出最慢的上升时间。

模拟电路:对CMOS运算放大器的摆率、输出驱动能力等不对称性能指标进行边界验证。 - SF - 慢NMOS/快PMOS角

与FS角相反,SF角导致电路的上拉能力强于下拉能力。对于以NMOS为下拉管的电路路径,其性能会显著恶化。

应用场景:

传输门:在SF角下,PMOS导通良好,但NMOS导通很差,可能导致低电平无法有效传输。

NMOS主导路径:对于下拉网络由NMOS构成的电路(如某些与非门、或门),此角会暴露出最慢的下降时间。

读/写冲突检查:在SRAM设计中,SF角可能影响读稳定性和写能力,是需要重点关注的场景之一。 - FT - 快NMOS角

此角描述了NMOS发生正向变异而PMOS保持典型的情况。它提供了从TT到FF的过渡视图,帮助定位对NMOS速度特别敏感的电路模块。

应用场景:

NMOS下拉路径分析:用于精确分析那些下拉网络是关键时序路径的电路(例如,大型NOR门)。

边际验证:当全局FF角过于悲观时,FT角可以提供一个更现实的性能上限边界,帮助提供设计的合理区间。 - ST - 慢NMOS角

此角描述了NMOS发生负向变异而PMOS保持典型的情况。它提供了从TT到SS的过渡视图。

应用场景:

NMOS下拉路径分析:用于精确分析下拉路径的最坏情况延迟。

建立时间检查的细化:对于NMOS主导的关键路径,ST角可能比全局SS角更能准确反映其建立时间边界。 - TF - 快PMOS角

此角描述了PMOS发生正向变异而NMOS保持典型的情况。它提供了从TT到FF的另一个维度的视图。

应用场景:

PMOS上拉路径分析:用于精确分析那些上拉网络是关键时序路径的电路(例如,大型NAND门)。

电源网络完整性:在PMOS快速开启时,评估电源网络的瞬时电流供应能力。 - TS - 慢PMOS角

此角描述了PMOS发生负向变异而NMOS保持典型的情况。它提供了从TT到SS的另一个维度的视图。

应用场景:

PMOS上拉路径分析:用于精确分析上拉路径的最坏情况延迟。

建立时间检查的细化:对于PMOS主导的关键路径,TS角可能比全局SS角更能准确反映其建立时间边界。

5. 工艺角设计总结

现代SoC设计流程中,对这九个工艺角的分析和验证构成了静态时序分析 和功耗完整性签核 的基础。

一个典型的设计策略是:

- 功能正确性:

在所有九个角下都必须保证逻辑功能正确。

2. 性能签核:

建立时间:主要在SS角下签核,并辅以ST和TS角进行关键路径的细化验证。

保持时间:主要在FF角下签核,并辅以FT和TF角进行关键路径的细化验证。

3. 功耗签核:

静态功耗:在FF角下的高温高压场景进行最坏情况分析。

动态功耗:在FF角下的高活动率场景进行分析。

4. 可靠性签核:

在FF角下进行电迁移和IR Drop分析。

5. 特殊电路:

对于模拟模块、SRAM、I/O和PLL,需要根据其拓扑结构选择最相关的混合角(如FS、SF)进行专门验证。

通过这种系统性的多角分析,设计团队可以确保芯片在面临不可避免的制造变异时,依然能保持高良率和可靠性。

项目简介

项目基于28nm工艺,完成24种pvt下的ring_oscillator 的综合及仿真实践验证, 基于VCS 完成post仿真验证。并完成自动化脚本开发,实现综合、ring oscillator仿真及频率收集。

项目难度:⭐

项目推荐度:⭐⭐

项目推荐天数:1~2天1)cfg_mux

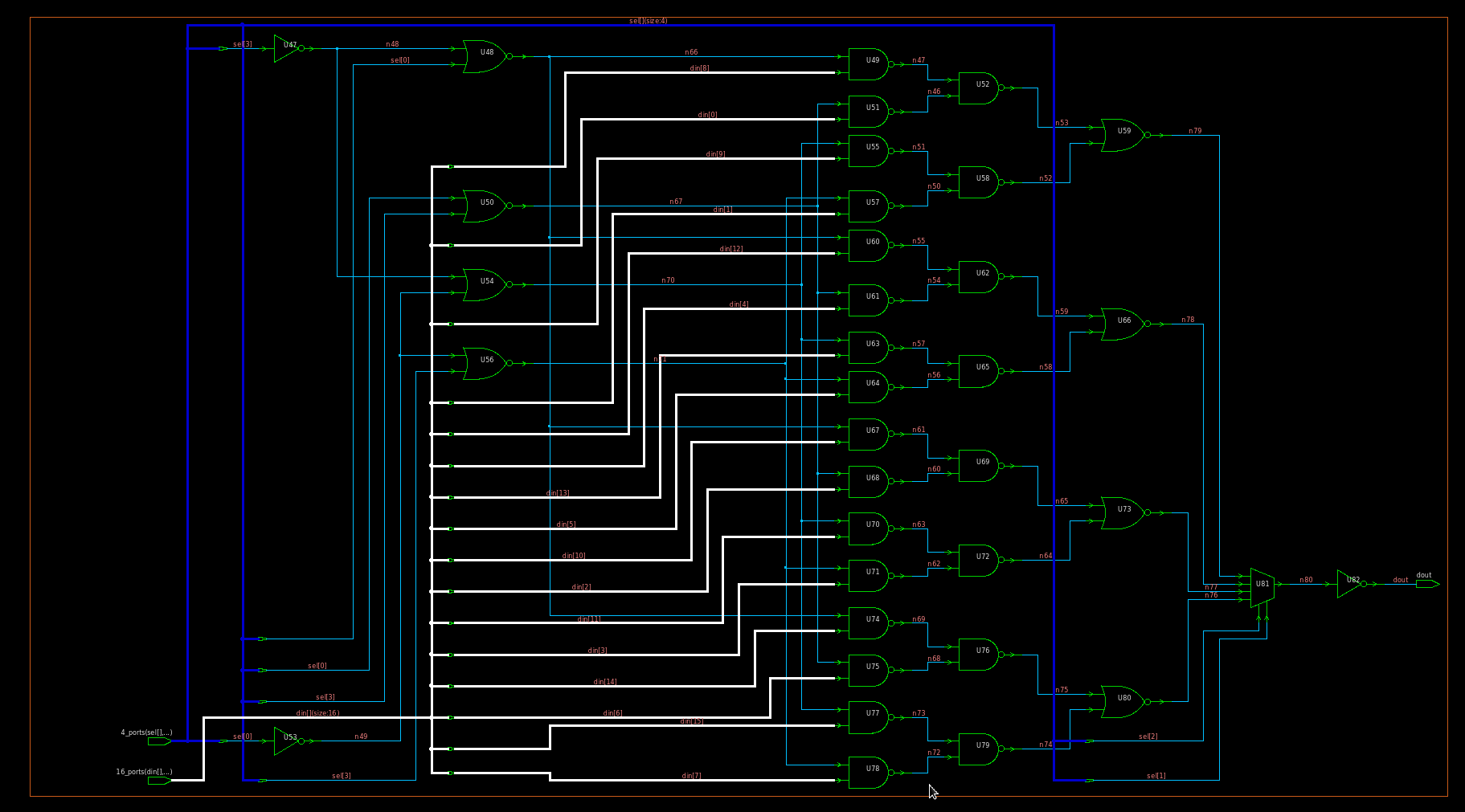

项目设计了一种可配置的多路选择器,用于实现ring osc 2^N级的选择器,是ring osc频率的主要组成电路,用于选择反相器链的级数,电路结构如下:

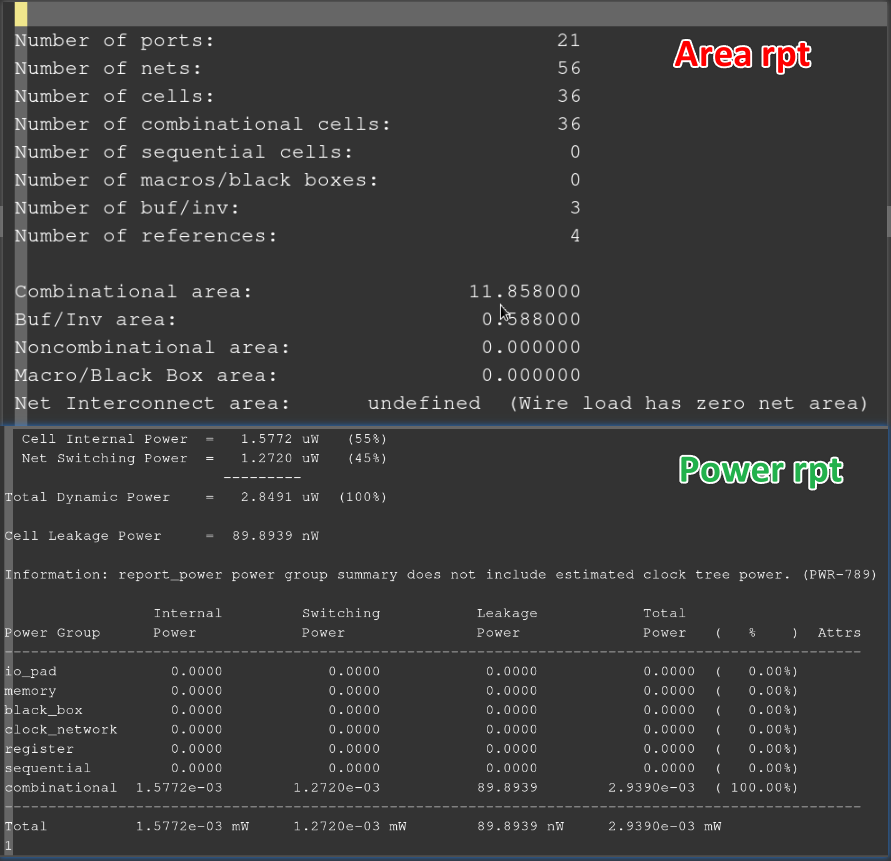

其中限制器件使用INV,NAND,NOR以及MUX4,用于实现每通道延迟相同,在TT1V25C条件下综合的power和area报告截图如Fig5所示。

Figure 4: cfg_mux schematic

Figure 4: cfg_mux schematic  Figure 5: cfg_mux area/power rpt

Figure 5: cfg_mux area/power rpt

2)cfg_inv_chain

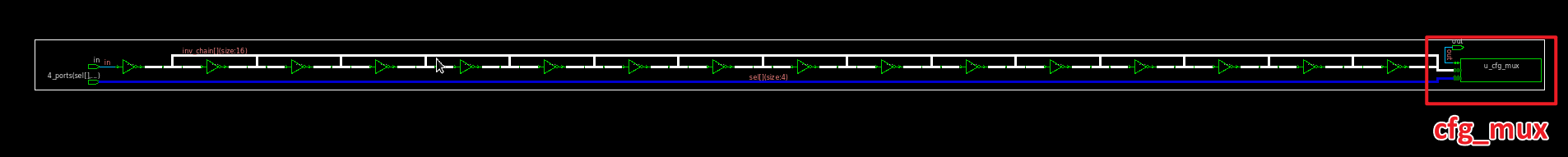

项目设计了一种可配置的反相器链,用于实现ring osc 2N-1级的反相器,是ring osc频率的主要组成电路,电路结构如下,红色框中为cfg_mux:

Figure 6: cfg_inv_chain

Figure 6: cfg_inv_chain

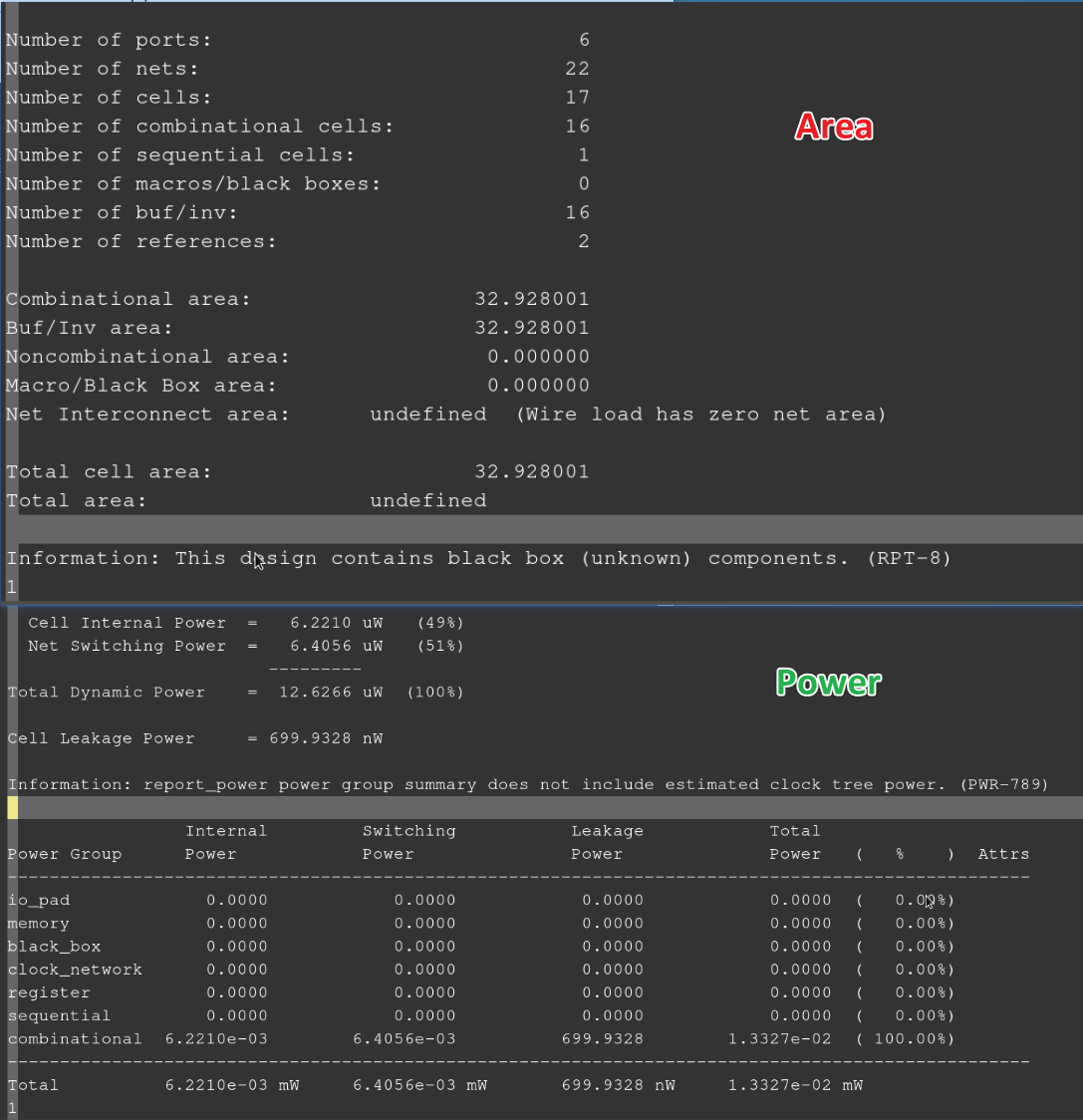

在TT1V25C条件下综合的power和area报告截图如Fig7所示。

Figure 7: cfg_inv_chain area/power rpt

Figure 7: cfg_inv_chain area/power rpt

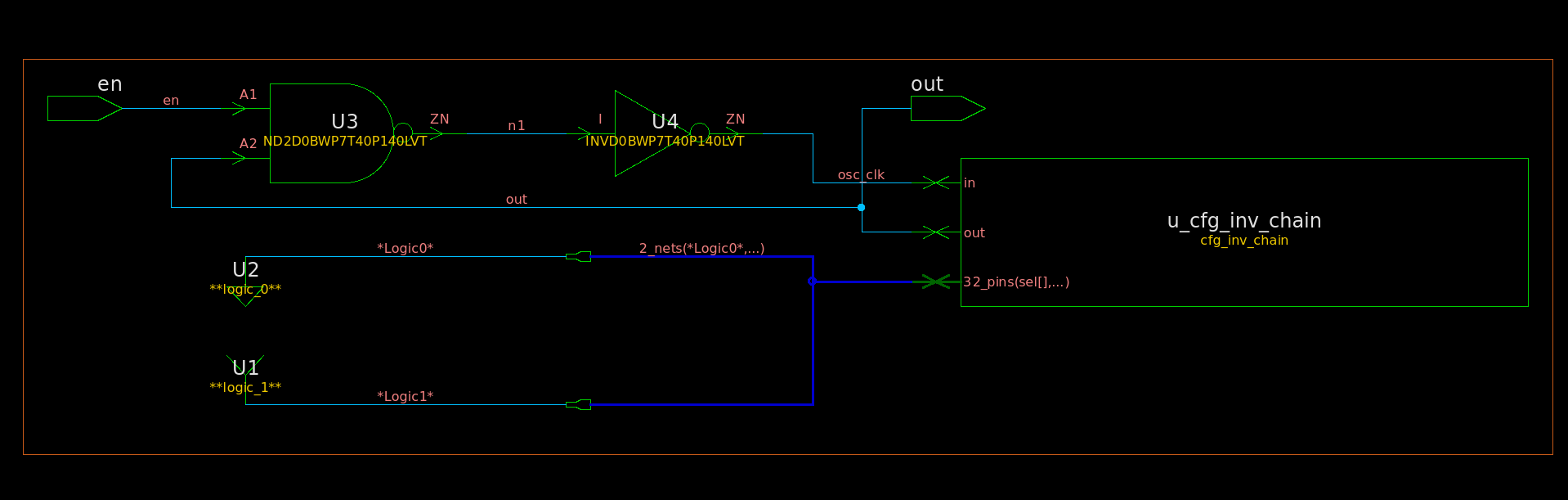

3)and_ring_osc

项目设计的ring_osc如下,enable信号和奇数级反相器链的输出经过and门后作为反相器链的输入,通过利用ring_osc在不同corner下的综合的时钟频率,可以在silicon后获取对应的corner,帮助debug。

Figure 8: and_ring_osc

仿真结果

1)仿真环境需求

- 测试平台包括VCS/DC/Verdi;

- 仿真包含DC综合后SDF反标仿真/post;

2)仿真波形

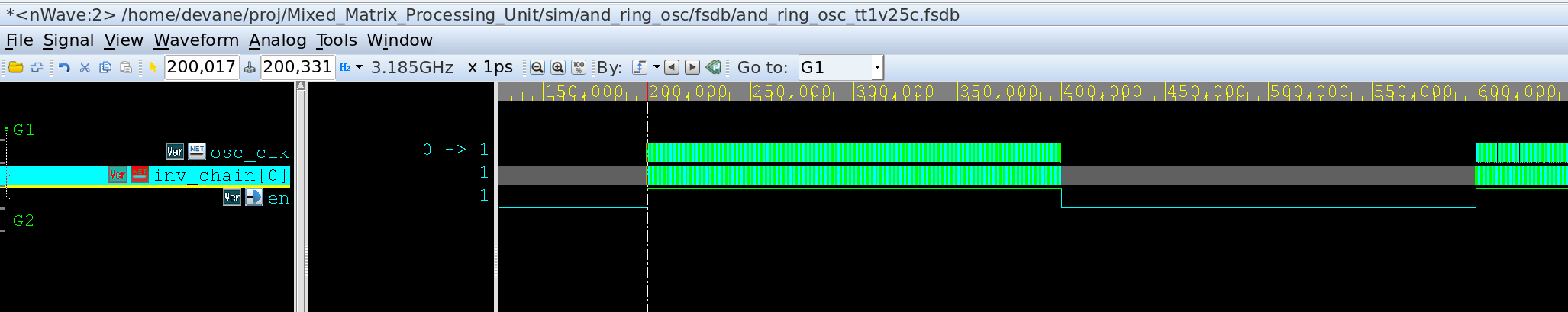

项目采用28nm工艺库,完成了DC综合后仿/post,完成上述ring_osc设计,TT1V25C条件下的osc波形如下,可以看到在该条件下,ring_osc的频率为3.185Ghz。

Figure 9: and_ring_osc [tt1v25c]

3)仿真结果

Auto measure testbench

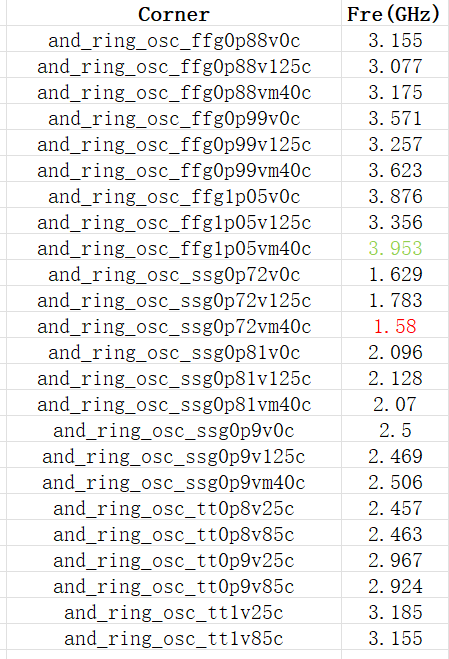

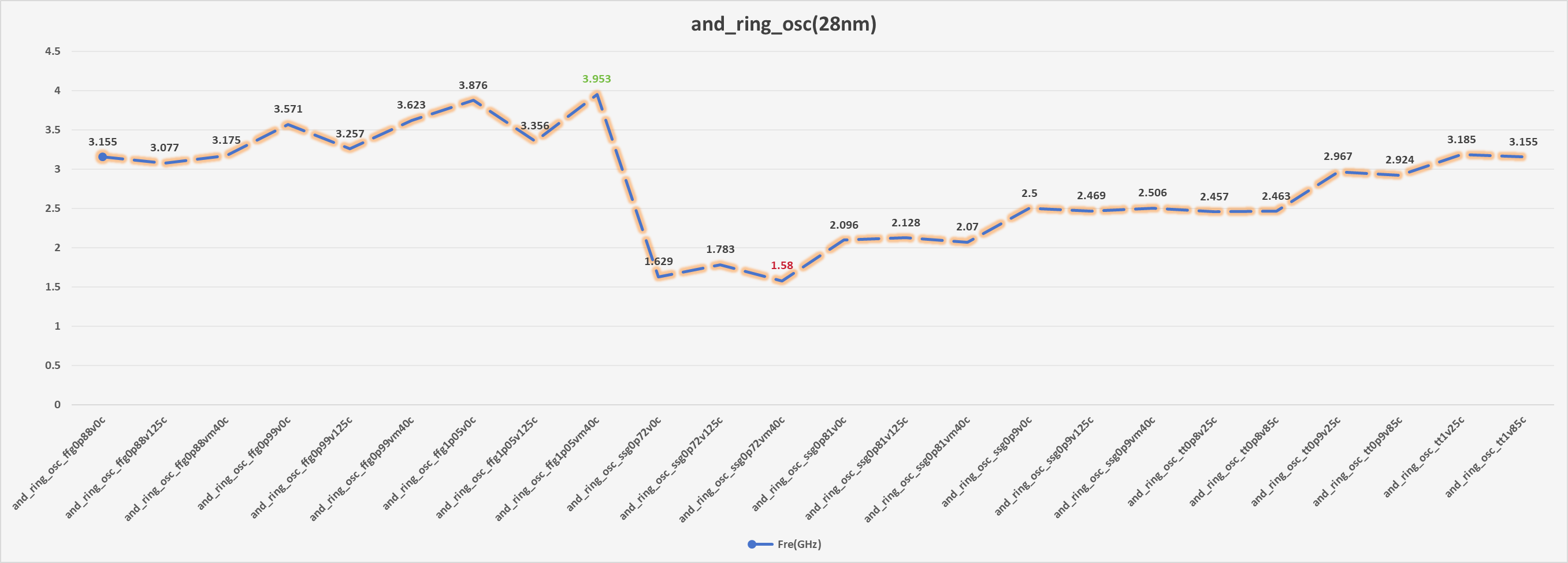

顶层testbench举例如下,通过获取ring_osc的上升沿来计算时钟频率。将24个Corner收集汇总为csv文件如图Figure 10所示:

csharp

/*========================================FILE_HEADER=====================================

# Author: Devane

# Last modified: 2025-10-19 23:53

# Filename: and_ring_osc_tb.v

# Description: and_ring_osc_tb.v

# VERSION V1.0

=========================================FILE_HEADER=====================================*/

// Auto-generated Verilog code

// Generated from folders in 'merged' directory

// Date: 1760842076.9686973

`timescale 1ns/1ps

module and_ring_osc_tb();

parameter DELAY_LEVELS = 16;

parameter WIDTH = 1;

reg [($clog2(DELAY_LEVELS)):0] sel;

reg [WIDTH-1:0] en;

reg pass_flag;

reg stop_flag;

wire [WIDTH-1:0] out;

// Frequency measurement variables

real first_edge_time = 0;

real second_edge_time = 0;

bit first_edge_detected = 0;

real measured_freq = 0;

real period_ns;

// Instantiate DUT

and_ring_osc u_ring_osc(

.en(en),

.out(out)

);

// Detect edges and calculate frequency

always @(posedge out) begin

if (en) begin

if (!first_edge_detected) begin

// Capture first rising edge time

first_edge_time = $realtime;

first_edge_detected = 1;

$display("@%0t ns: First rising edge detected", $time);

end else begin

// Capture second rising edge time and calculate frequency

second_edge_time = $realtime;

period_ns = second_edge_time - first_edge_time;

if (period_ns > 0) begin

measured_freq = 1.0 / period_ns; // Frequency in GHz

$display("@%0t ns: Second rising edge detected", $realtime);

$display("=== Frequency Measurement ===");

$display("Period: %0.3f ns", period_ns);

$display("Frequency: %0.3f GHz", measured_freq);

$display("==============================");

end

// Disable further measurements

first_edge_detected = 0;

end

end

end

// Reset measurement when en goes low

always @(negedge en) begin

first_edge_detected = 0;

end

// Test sequence

initial begin

// Initialize

sel = 15;

stop_flag = 0;

en = 0;

$display("=== Starting AND Ring Oscillator Testbench ===");

// Test sequence 1

#200;

en = 1;

#200;

en = 0;

// Test sequence 2

#200;

en = 1;

#200;

en = 0;

// Final

#200;

stop_flag = 1;

#200;

$display("=== Testbench completed ===");

$finish;

end

`ifdef ffg0p88v0c

initial begin

$fsdbDumpfile("./fsdb/and_ring_osc_ffg0p88v0c.fsdb");

$fsdbDumpvars(0,and_ring_osc_tb,"+all");

end

`endif

`ifdef ffg0p88v0c

initial

begin

$sdf_annotate("./merged/ffg0p88v0c/mapped/and_ring_osc_post_dc.sdf",and_ring_osc,,"./log/and_ring_ffg0p88v0c_sdf.log",);

$sdf_annotate("./merged/ffg0p88v0c/mapped/cfg_inv_chain_post_dc.sdf",and_ring_osc.u_cfg_inv_chain,,"./log/cfg_inv_chain_ffg0p88v0c_sdf.log",);

$sdf_annotate("./merged/ffg0p88v0c/mapped/cfg_mux_post_dc.sdf",and_ring_osc.u_cfg_inv_chain.u_cfg_mux,,"./log/cfg_mux_ffg0p88v0c_sdf.log",);

end

`endif

endmodule Figure 10: and_ring_osc [24 corners]

Figure 10: and_ring_osc [24 corners]

- 其中,ffg1p05vm40c 条件下频率最高,为3.953Ghz,ssg0p72vm40c条件下频率最低,为1.58Ghz。

Figure 11: ring_osc frequency compare [24 corner]

Figure 11: ring_osc frequency compare [24 corner]

总结

项目学习目的:

(1)熟练掌握ring_osc以及工艺角的基本原理;

(2)熟悉 Verilog HDL仿真以及相关流程工具;