FPGA教程系列-番外篇Model Composer初探

某些原因,接触到这个东西,感觉还挺有用的,就本着记录下的原则,进行一个学习的记录。

早期应该是叫System Generator ,后来应该是改名成Model Composer,其实名字不重要,重要的是功能。

System Generator是Xilinx公司进行数字信号处理开发的一种设计工具,它通过将Xilinx开发的一些模块嵌入到Simulink的库中,可以在Simulink中进行定点仿真,可以设置定点信号的类型,这样就可以比较定点仿真与浮点仿真的区别。并且可以生成HDL文件,或者网表,可以在ISE中进行调用。或者直接生成比特流下载文件。能够加快DSP系统的开发进度。

安装

Xilinx出品,安装过程自行百度,但是。。。版本的兼容性真的要吐槽一下,每个版本对应一定范围内的Matlab,安装前一定要做好工作,否则。。。重装吧,少年。

Simulink

其实也不只是对Model Composer的学习,顺便看看Simulink的一些基本的操作和功能,技多不压身吧。

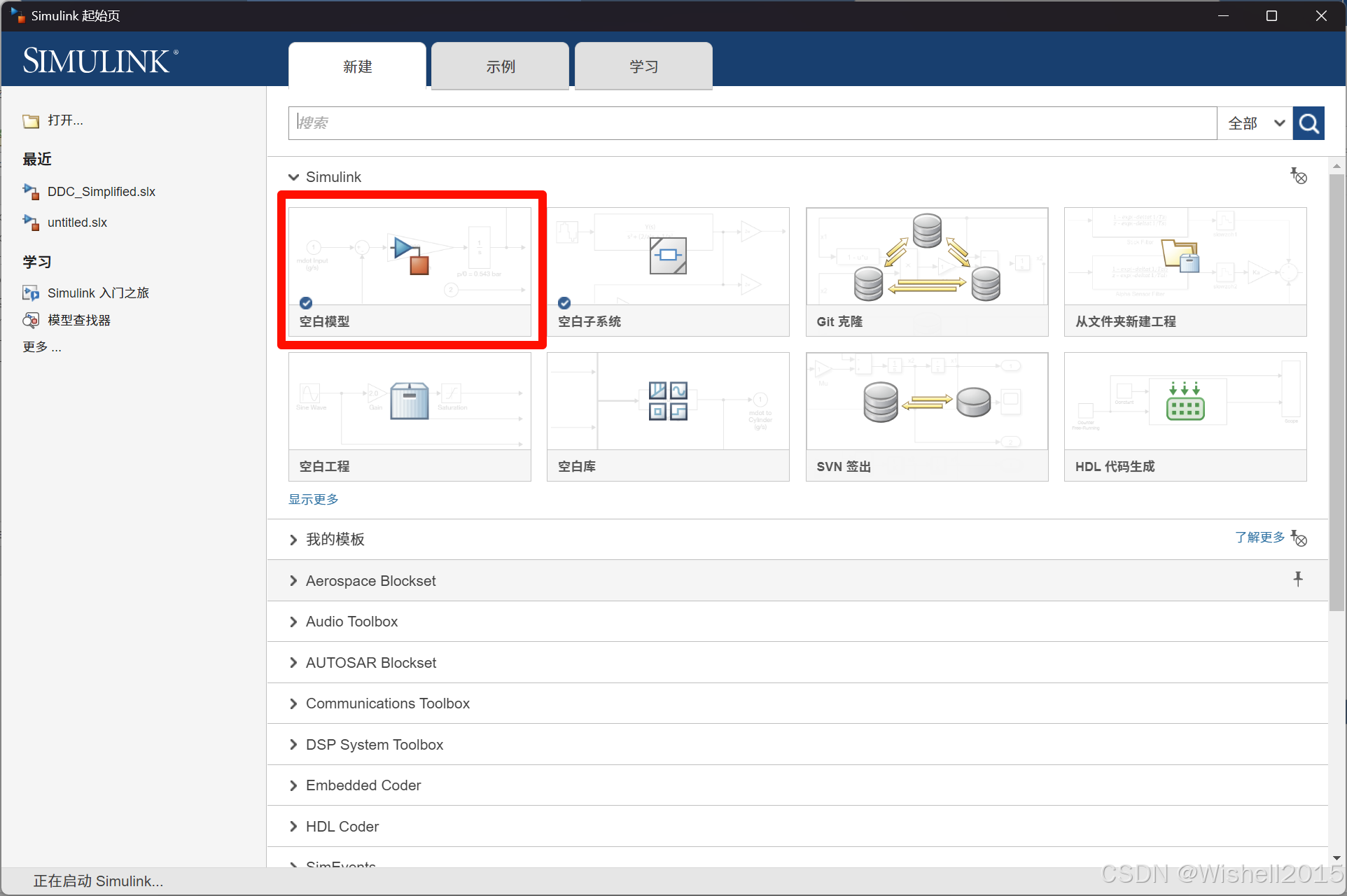

新建一个空白的模型

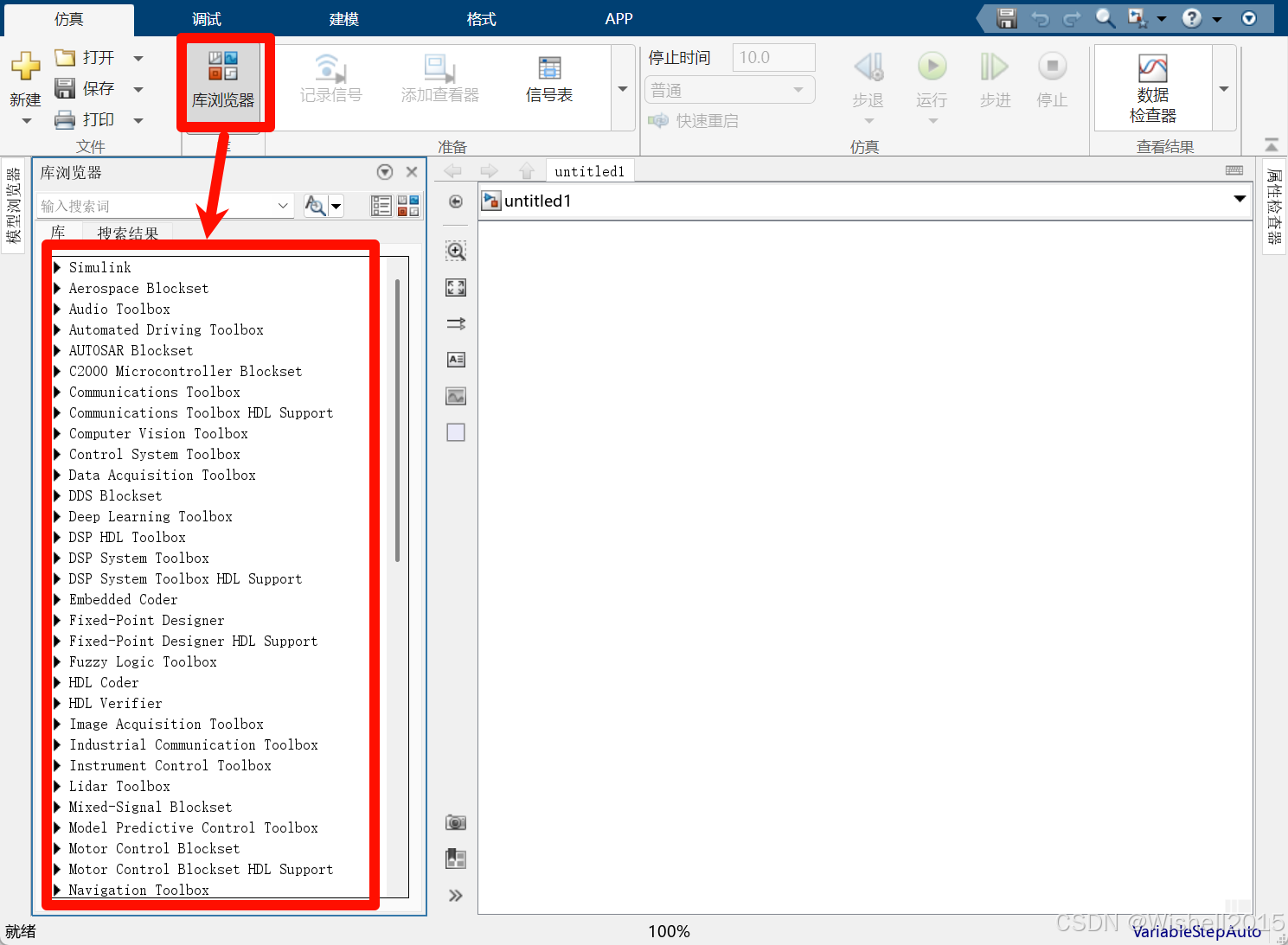

可以从库浏览器中,添加相应的模块。

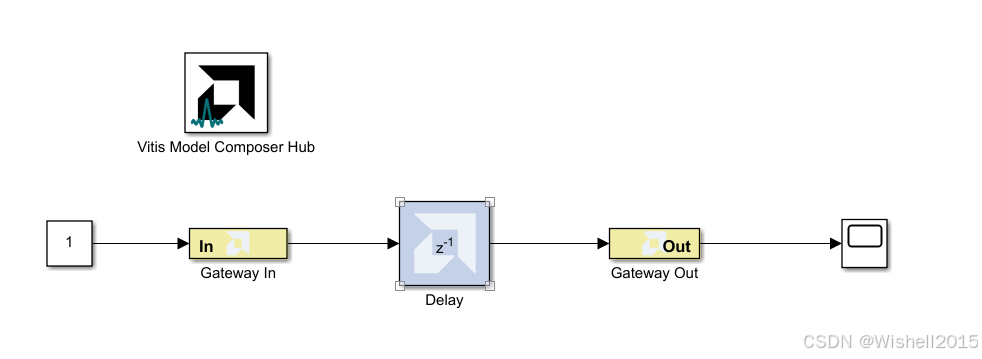

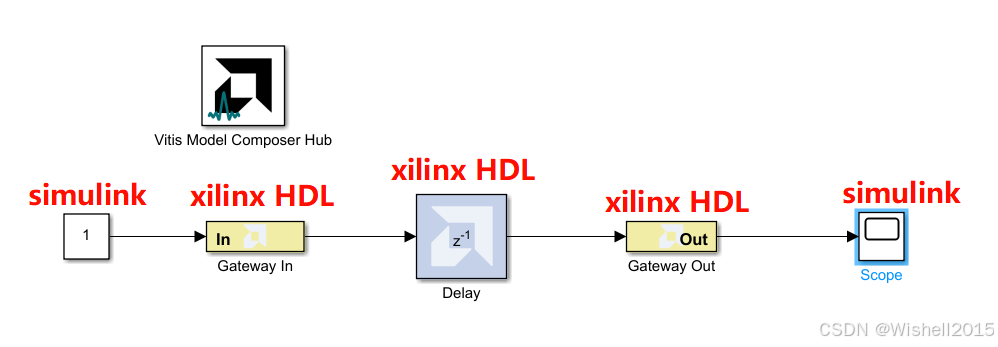

简单测试

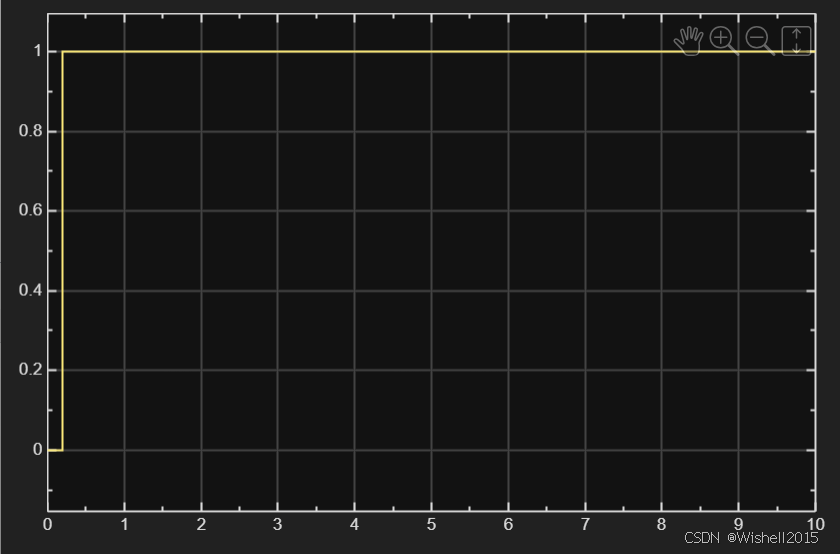

做一个简单的延迟。Z变换代表了延迟一个单位时间,具体的为什么Z变换代表延迟,后边懂了再具体说说吧。

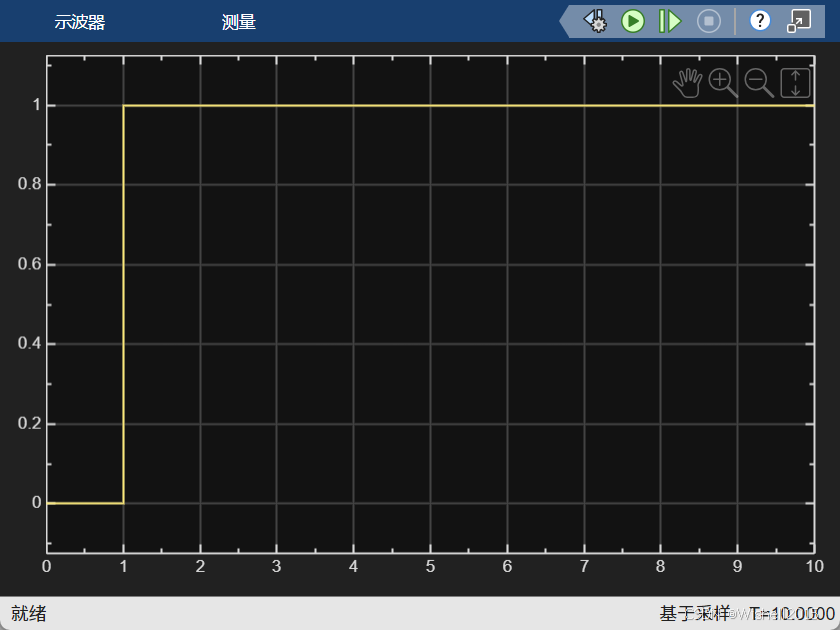

先贴结果:

与预计的结果一致,再谈谈几个注意点:

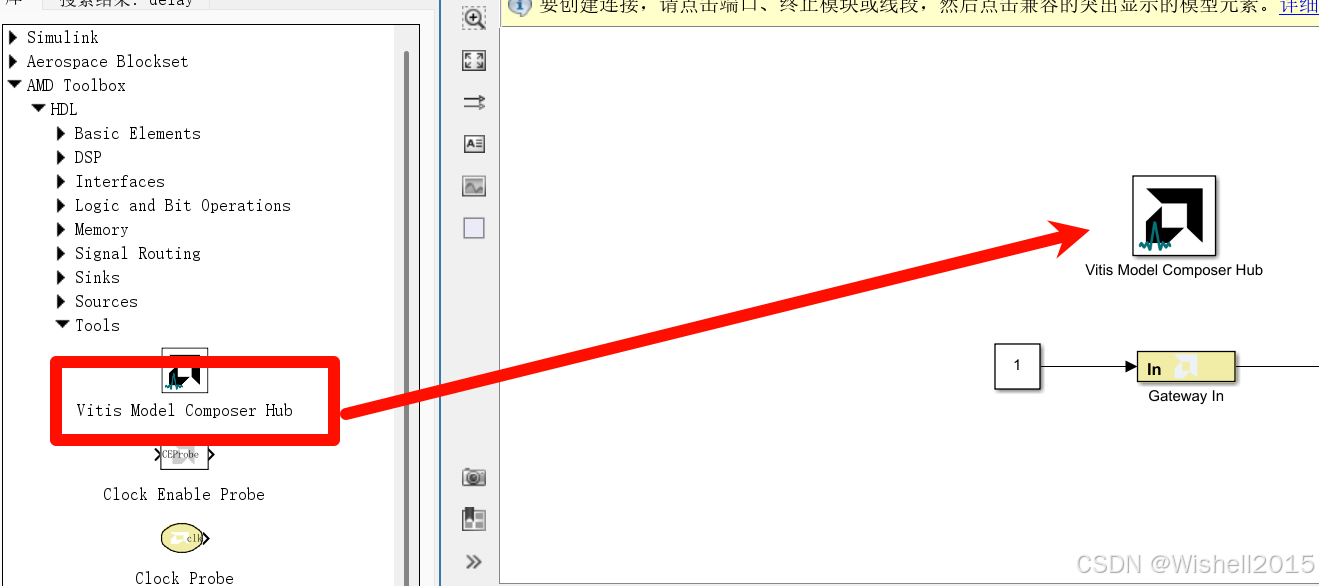

1、这玩意必须要有,没有的话报错,而且要设定对应的器件,不做ip核的话,随便选。

2、不要觉得模块随便选就OK,这些东西都要对应,否则的话,继续报错。

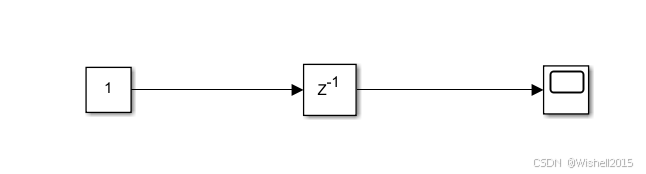

3、如果只是仿真的话。。。。全部用simulink模块好像也可以。延时的时间可能得看看具体是什么个情况。

综上,基本的仿真好像就是这样,可以稍后深入研究一点。