🔍 一、MPU基础概念与核心价值

1.1 什么是MPU?

MPU (Memory Protection Unit) 是嵌入式处理器中的硬件单元,用于监控和控制处理器对内存区域的访问权限,提供硬件级别的内存保护机制。与MMU不同,MPU不提供虚拟内存映射功能,专注于访问权限控制。

1.2 MPU的核心价值

┌─────────────────────────────┬─────────────────────────────┐

│ 安全性提升 │ 系统可靠性增强 │

├─────────────────────────────┼─────────────────────────────┤

│ • 防止恶意代码执行 │ • 避免野指针破坏关键数据 │

│ • 保护敏感数据不被未授权访问│ • 隔离故障模块,防止系统崩溃│

│ • 满足功能安全标准(ISO26262)│ • 增强多任务环境稳定性 │

└─────────────────────────────┴─────────────────────────────┘1.3 MPU vs MMU 关键区别

| 特性 | MPU | MMU |

|---|---|---|

| 核心功能 | 访问权限控制 | 虚拟地址映射 + 权限控制 |

| 地址转换 | 无 | 有(虚拟→物理) |

| 硬件复杂度 | 低(4-16区域) | 高(4KB页表) |

| 性能开销 | 极低(1-2周期) | 中高(10-100周期) |

| 适用场景 | 实时嵌入式系统 | 通用操作系统 |

| 典型应用 | Cortex-M系列 | Cortex-A系列 |

⚙️ 二、ARM Cortex-M MPU架构深度解析

2.1 Cortex-M系列MPU版本演进

Cortex-M3/M4: MPUv1 → 8个可编程区域,基本访问控制

│

└─ Cortex-M7: MPUv2 → 16个区域,增强属性控制

│

└─ Cortex-M33/M55: MPUv3 → 16区域+子区域,TrustZone集成2.2 MPU区域配置参数详解

每个MPU区域包含以下关键配置参数:

cpp

typedef struct {

uint32_t base_address; // 区域基地址(32位对齐)

uint32_t region_size; // 区域大小(2^n, 32B-4GB)

uint8_t region_number; // 区域编号(0-15)

uint8_t enable; // 区域使能(0/1)

// 访问权限

uint8_t access_permission; // AP[2:0]: 000-111 (7种组合)

uint8_t execute_permission; // XN: 0=可执行, 1=不可执行

// 内存属性

uint8_t shareable; // 0=非共享, 1=共享

uint8_t cacheable; // 0=不可缓存, 1=可缓存

uint8_t bufferable; // 0=不可缓冲, 1=可缓冲

// 高级特性 (MPUv2+)

uint8_t subregion_disable; // 8位掩码,禁用子区域

uint8_t memory_type; // Normal/Device/Strongly-ordered

} mpu_region_config_t;2.3 关键寄存器详解 (Cortex-M7为例)

| 寄存器 | 位域 | 功能描述 |

|---|---|---|

| MPU_TYPE | IREGION[7:0] |

指令区域数量(只读) |

DREGION[7:0] |

数据区域数量(只读) | |

SEPARATE |

0=共享区域, 1=独立区域 | |

| MPU_CTRL | ENABLE[0] |

全局MPU使能 |

HFNMIENA[1] |

硬故障/NMI使能(关键!) | |

PRIVDEFENA[2] |

默认特权访问 | |

| MPU_RNR | REGION[3:0] |

当前操作区域编号 |

| MPU_RBAR | ADDR[31:5] |

区域基地址 |

VALID[4] |

地址有效位 | |

REGION[3:0] |

区域编号(覆盖RNR) | |

| MPU_RASR | ENABLE[0] |

区域使能 |

SIZE[4:1] |

区域大小(2^n) | |

SRD[7:0] |

子区域禁用掩码 | |

B[0], C[1] |

缓冲/缓存使能 | |

S[1] |

共享属性 | |

TEX[2:0] |

内存类型扩展 | |

AP[2:0] |

访问权限 | |

XN[0] |

执行禁止 |

🛠️ 三、MPU配置实战指南

3.1 标准配置流程

diff

void MPU_Config(void) {

// 1. 禁用MPU(修改配置前必须禁用)

MPU->CTRL = 0;

// 2. 配置默认内存映射

// - 0x00000000: 闪存 (只读, 可执行)

// - 0x20000000: SRAM (读写, 不可执行)

// - 0x40000000: 外设 (特权访问)

/* 区域0: 闪存 (0x08000000 - 0x080FFFFF) */

MPU->RBAR = 0x08000000UL | MPU_RBAR_VALID_Msk | (0UL << MPU_RBAR_REGION_Pos);

MPU->RASR = MPU_RASR_ENABLE_Msk |

(0x1F << MPU_RASR_SIZE_Pos) | // 1MB区域 (2^19+1 = 0x1F)

(0x1 << MPU_RASR_B_Pos) | // Bufferable

(0x1 << MPU_RASR_C_Pos) | // Cacheable

(0x0 << MPU_RASR_S_Pos) | // Non-shareable

(0x0 << MPU_RASR_TEX_Pos) | // Normal memory

(0x3 << MPU_RASR_AP_Pos) | // AP=011: 读写(特权), 只读(用户)

(0x0 << MPU_RASR_XN_Pos); // 可执行

/* 区域1: SRAM (0x20000000 - 0x2002FFFF) */

MPU->RBAR = 0x20000000UL | MPU_RBAR_VALID_Msk | (1UL << MPU_RBAR_REGION_Pos);

MPU->RASR = MPU_RASR_ENABLE_Msk |

(0x14 << MPU_RASR_SIZE_Pos) | // 192KB (2^17+1 = 0x14)

(0x1 << MPU_RASR_B_Pos) | // Bufferable

(0x1 << MPU_RASR_C_Pos) | // Cacheable

(0x0 << MPU_RASR_S_Pos) | // Non-shareable

(0x0 << MPU_RASR_TEX_Pos) | // Normal memory

(0x3 << MPU_RASR_AP_Pos) | // AP=011: 读写(特权), 只读(用户)

(0x1 << MPU_RASR_XN_Pos); // 不可执行 (XN=1)

/* 区域2: 外设空间 (0x40000000 - 0x43FFFFFF) */

MPU->RBAR = 0x40000000UL | MPU_RBAR_VALID_Msk | (2UL << MPU_RBAR_REGION_Pos);

MPU->RASR = MPU_RASR_ENABLE_Msk |

(0x1A << MPU_RASR_SIZE_Pos) | // 64MB

(0x0 << MPU_RASR_B_Pos) | // Non-bufferable

(0x0 << MPU_RASR_C_Pos) | // Non-cacheable

(0x1 << MPU_RASR_S_Pos) | // Shareable

(0x0 << MPU_RASR_TEX_Pos) | // Device memory

(0x1 << MPU_RASR_AP_Pos) | // AP=001: 读写(特权), 无访问(用户)

(0x1 << MPU_RASR_XN_Pos); // 不可执行

/* 区域3: 关键数据区 (0x20000000 - 0x20000FFF) - 零等待TCM */

MPU->RBAR = 0x20000000UL | MPU_RBAR_VALID_Msk | (3UL << MPU_RBAR_REGION_Pos);

MPU->RASR = MPU_RASR_ENABLE_Msk |

(0x0B << MPU_RASR_SIZE_Pos) | // 4KB

(0x0 << MPU_RASR_B_Pos) | // Non-bufferable (TCM特性)

(0x0 << MPU_RASR_C_Pos) | // Non-cacheable (避免一致性问题)

(0x1 << MPU_RASR_S_Pos) | // Shareable

(0x1 << MPU_RASR_TEX_Pos) | // TCM memory

(0x3 << MPU_RASR_AP_Pos) | // 全访问权限

(0x1 << MPU_RASR_XN_Pos); // 不可执行

// 3. 使能MPU (关键: 使能HFNMIENA防止硬故障时MPU失效)

MPU->CTRL = MPU_CTRL_ENABLE_Msk | MPU_CTRL_HFNMIENA_Msk;

// 4. 刷新流水线

__DSB();

__ISB();

}3.2 高级配置:子区域保护

// 保护关键内存区域中的特定子区域

void MPU_Protect_Critical_Data(void) {

// 假设我们有128KB SRAM (0x20000000-0x2001FFFF)

// 需要保护前16KB (0x20000000-0x20003FFF) 为只读

// 其余部分保持读写

// 配置128KB区域,但禁用特定子区域

MPU->RBAR = 0x20000000UL | MPU_RBAR_VALID_Msk | (4UL << MPU_RBAR_REGION_Pos);

MPU->RASR = MPU_RASR_ENABLE_Msk |

(0x11 << MPU_RASR_SIZE_Pos) | // 128KB (2^16+1)

(0x1 << MPU_RASR_B_Pos) |

(0x1 << MPU_RASR_C_Pos) |

(0x0 << MPU_RASR_S_Pos) |

(0x0 << MPU_RASR_TEX_Pos) |

(0x3 << MPU_RASR_AP_Pos) | // 默认读写

(0x1 << MPU_RASR_XN_Pos) |

(0xFE << MPU_RASR_SRD_Pos); // 禁用7/8子区域 (0xFE = 11111110)

// 仅启用第一个16KB子区域

}

// 配置只读子区域

void MPU_Config_ReadOnly_Subregion(void) {

// 配置第一个16KB子区域为只读

MPU->RBAR = 0x20000000UL | MPU_RBAR_VALID_Msk | (5UL << MPU_RBAR_REGION_Pos);

MPU->RASR = MPU_RASR_ENABLE_Msk |

(0x0C << MPU_RASR_SIZE_Pos) | // 16KB

(0x1 << MPU_RASR_B_Pos) |

(0x1 << MPU_RASR_C_Pos) |

(0x0 << MPU_RASR_S_Pos) |

(0x0 << MPU_RASR_TEX_Pos) |

(0x7 << MPU_RASR_AP_Pos) | // AP=111: 只读(特权+用户)

(0x1 << MPU_RASR_XN_Pos);

}🔒 四、MPU在实际系统中的应用

4.1 与RTOS集成 (FreeRTOS示例)

// FreeRTOS MPU移植层关键函数

void vPortStoreTaskMPUSettings( xMPU_SETTINGS *xMPUSettings,

const struct xSTACK_TYPE *pxTopOfStack,

uint32_t ulStackDepth )

{

// 1. 保存当前任务的MPU配置

xMPUSettings->xRegion[0].ulRegionBaseAddress =

((uint32_t)pxTopOfStack - (ulStackDepth * sizeof(StackType_t)));

xMPUSettings->xRegion[0].ulRegionSize = ulStackDepth;

xMPUSettings->xRegion[0].ulRegionAttribute = portMPU_REGION_READ_WRITE;

// 2. 配置任务专用内存区域

if( task_specific_memory != NULL ) {

xMPUSettings->xRegion[1].ulRegionBaseAddress = (uint32_t)task_specific_memory;

xMPUSettings->xRegion[1].ulRegionSize = task_mem_size;

xMPUSettings->xRegion[1].ulRegionAttribute = portMPU_REGION_READ_WRITE;

}

}

// 任务切换时的MPU配置

void vPortSwitchContextMPU( void ) {

// 1. 禁用MPU

MPU->CTRL = 0;

// 2. 重新配置所有区域 (基于新任务的设置)

for(int i = 0; i < portNUM_CONFIGURABLE_REGIONS; i++) {

MPU->RBAR = pxCurrentTCB->xMPUSettings.xRegion[i].ulRegionBaseAddress |

MPU_RBAR_VALID_Msk | (i << MPU_RBAR_REGION_Pos);

MPU->RASR = MPU_RASR_ENABLE_Msk |

pxCurrentTCB->xMPUSettings.xRegion[i].ulRegionAttribute |

(calculate_size(pxCurrentTCB->xMPUSettings.xRegion[i].ulRegionSize) << MPU_RASR_SIZE_Pos);

}

// 3. 重新使能MPU

MPU->CTRL = MPU_CTRL_ENABLE_Msk | MPU_CTRL_HFNMIENA_Msk;

}4.2 安全关键应用配置

// ISO26262 ASIL-D 级别MPU配置

void MPU_Config_SafetyCritical(void) {

// 区域0: 安全关键代码 (只读, 可执行, 不可缓存)

MPU->RBAR = SAFE_CODE_BASE | MPU_RBAR_VALID_Msk | (0 << MPU_RBAR_REGION_Pos);

MPU->RASR = MPU_RASR_ENABLE_Msk |

(0x0F << MPU_RASR_SIZE_Pos) | // 64KB

(0x0 << MPU_RASR_B_Pos) | // Non-bufferable

(0x0 << MPU_RASR_C_Pos) | // Non-cacheable (避免缓存一致性问题)

(0x1 << MPU_RASR_S_Pos) | // Shareable

(0x1 << MPU_RASR_TEX_Pos) | // Tightly Coupled

(0x7 << MPU_RASR_AP_Pos) | // 只读 (特权+用户)

(0x0 << MPU_RASR_XN_Pos); // 可执行

// 区域1: 安全关键数据 (读写, 不可执行, ECC保护)

MPU->RBAR = SAFE_DATA_BASE | MPU_RBAR_VALID_Msk | (1 << MPU_RBAR_REGION_Pos);

MPU->RASR = MPU_RASR_ENABLE_Msk |

(0x0B << MPU_RASR_SIZE_Pos) | // 4KB

(0x0 << MPU_RASR_B_Pos) |

(0x0 << MPU_RASR_C_Pos) |

(0x1 << MPU_RASR_S_Pos) |

(0x2 << MPU_RASR_TEX_Pos) | // ECC memory

(0x3 << MPU_RASR_AP_Pos) | // 读写 (仅特权)

(0x1 << MPU_RASR_XN_Pos); // 不可执行

// 区域2: 通信缓冲区 (读写, 不可执行, 非缓存)

MPU->RBAR = COMM_BUFFER_BASE | MPU_RBAR_VALID_Msk | (2 << MPU_RBAR_REGION_Pos);

MPU->RASR = MPU_RASR_ENABLE_Msk |

(0x0A << MPU_RASR_SIZE_Pos) | // 2KB

(0x0 << MPU_RASR_B_Pos) | // Non-bufferable (实时性)

(0x0 << MPU_RASR_C_Pos) | // Non-cacheable

(0x1 << MPU_RASR_S_Pos) | // Shareable

(0x0 << MPU_RASR_TEX_Pos) | // Device

(0x1 << MPU_RASR_AP_Pos) | // 读写 (特权), 无访问 (用户)

(0x1 << MPU_RASR_XN_Pos);

// 区域3: 外设寄存器 (特权访问, 不可缓存)

MPU->RBAR = PERIPH_BASE | MPU_RBAR_VALID_Msk | (3 << MPU_RBAR_REGION_Pos);

MPU->RASR = MPU_RASR_ENABLE_Msk |

(0x14 << MPU_RASR_SIZE_Pos) | // 16MB

(0x0 << MPU_RASR_B_Pos) |

(0x0 << MPU_RASR_C_Pos) |

(0x1 << MPU_RASR_S_Pos) |

(0x0 << MPU_RASR_TEX_Pos) | // Device

(0x1 << MPU_RASR_AP_Pos) | // 仅特权访问

(0x1 << MPU_RASR_XN_Pos);

// 使能MPU (包含HFNMIENA)

MPU->CTRL = MPU_CTRL_ENABLE_Msk | MPU_CTRL_HFNMIENA_Msk | MPU_CTRL_PRIVDEFENA_Msk;

__DSB();

__ISB();

}4.3 故障隔离与恢复机制

cpp

// MPU故障处理函数

void MemManage_Handler(void) {

// 1. 获取故障状态

uint32_t mmfar = SCB->MMFAR;

uint32_t cfsr = SCB->CFSR;

// 2. 诊断故障类型

if(cfsr & SCB_CFSR_MLSPERR_Msk) {

log_error("MPU: 多级处理错误 @ 0x%08X", mmfar);

}

if(cfsr & SCB_CFSR_MSTKERR_Msk) {

log_error("MPU: 堆栈错误 @ 0x%08X", mmfar);

}

if(cfsr & SCB_CFSR_MUNSTKERR_Msk) {

log_error("MPU: 出栈错误 @ 0x%08X", mmfar);

}

if(cfsr & SCB_CFSR_DACCVIOL_Msk) {

log_error("MPU: 数据访问冲突 @ 0x%08X", mmfar);

}

if(cfsr & SCB_CFSR_IACCVIOL_Msk) {

log_error("MPU: 指令访问冲突 @ 0x%08X", mmfar);

}

// 3. 安全恢复策略

// - 隔离故障任务

// - 重置关键模块

// - 进入安全状态

if(is_safe_to_recover()) {

// 尝试恢复

reset_faulty_module();

restore_mpu_configuration();

} else {

// 进入安全状态

enter_safe_state();

system_reset();

}

// 4. 清除标志

SCB->CFSR |= SCB_CFSR_MEMFAULTACT_Msk;

}⚡ 五、性能优化与最佳实践

5.1 性能影响分析

| 配置场景 | 周期开销 | 适用场景 |

|---|---|---|

| 无MPU | 0 | 开发/调试阶段 |

| 4区域 | 1-2 | 资源受限设备 |

| 8区域 | 2-3 | 通用RTOS系统 |

| 16区域 | 3-5 | 安全关键系统 |

| 区域重叠 | 10+ | 应避免! |

5.2 优化策略

// 1. 最小化区域数量

// - 合并相同属性的内存区域

// - 使用子区域代替多个小区域

// 2. 关键路径优化

// - 将频繁访问的数据放在非缓存区域

// - 避免在中断处理程序中访问受保护内存

// 3. 高效区域排序

// - 将最常访问的区域放在低编号区域(硬件优先检查)

// - 按访问频率排序: 区域0 > 区域1 > ... > 区域15

// 4. 缓存策略优化

void MPU_Optimize_Cache(void) {

// 代码区域: 缓存但不缓冲

MPU->RBAR = CODE_BASE | MPU_RBAR_VALID_Msk | (0 << MPU_RBAR_REGION_Pos);

MPU->RASR = MPU_RASR_ENABLE_Msk |

(0x14 << MPU_RASR_SIZE_Pos) | // 128KB

(0x0 << MPU_RASR_B_Pos) | // Non-bufferable

(0x1 << MPU_RASR_C_Pos) | // Cacheable

(0x0 << MPU_RASR_S_Pos) |

(0x0 << MPU_RASR_TEX_Pos) |

(0x7 << MPU_RASR_AP_Pos) | // 只读

(0x0 << MPU_RASR_XN_Pos); // 可执行

// 数据区域: 缓存+缓冲

MPU->RBAR = DATA_BASE | MPU_RBAR_VALID_Msk | (1 << MPU_RBAR_REGION_Pos);

MPU->RASR = MPU_RASR_ENABLE_Msk |

(0x11 << MPU_RASR_SIZE_Pos) | // 64KB

(0x1 << MPU_RASR_B_Pos) | // Bufferable

(0x1 << MPU_RASR_C_Pos) | // Cacheable

(0x0 << MPU_RASR_S_Pos) |

(0x0 << MPU_RASR_TEX_Pos) |

(0x3 << MPU_RASR_AP_Pos) | // 读写

(0x1 << MPU_RASR_XN_Pos); // 不可执行

}🚨 六、常见陷阱与解决方案

6.1 典型错误

// ❌ 错误1: 未使能HFNMIENA

MPU->CTRL = MPU_CTRL_ENABLE_Msk; // 硬故障时MPU失效!

// ❌ 错误2: 未对齐的基地址

MPU->RBAR = 0x20000001; // 必须32字节对齐

// ❌ 错误3: 无效的区域大小

MPU->RASR = ... | (0x05 << MPU_RASR_SIZE_Pos); // 非2^n大小无效

// ❌ 错误4: 未刷新流水线

MPU->CTRL = MPU_CTRL_ENABLE_Msk;

// 缺少 __DSB(); __ISB();

// ❌ 错误5: 在MPU使能时修改区域

MPU->CTRL = MPU_CTRL_ENABLE_Msk;

MPU->RBAR = ...; // 必须先禁用MPU!6.2 调试技巧

cpp

// 1. MPU寄存器转储函数

void MPU_Dump_Registers(void) {

printf("MPU_TYPE = 0x%08X\n", MPU->TYPE);

printf("MPU_CTRL = 0x%08X\n", MPU->CTRL);

for(int i = 0; i < 16; i++) {

MPU->RNR = i;

printf("Region %d: RBAR=0x%08X, RASR=0x%08X\n",

i, MPU->RBAR, MPU->RASR);

}

}

// 2. 运行时区域检查

bool is_address_protected(uint32_t addr) {

for(int i = 0; i < 16; i++) {

if(MPU->RNR == i && (MPU->RASR & MPU_RASR_ENABLE_Msk)) {

uint32_t base = MPU->RBAR & 0xFFFFFFE0;

uint32_t size = 1 << (((MPU->RASR >> MPU_RASR_SIZE_Pos) & 0x1F) + 1);

if(addr >= base && addr < (base + size)) {

uint32_t ap = (MPU->RASR >> MPU_RASR_AP_Pos) & 0x7;

return (ap != 0x3); // 0x3=完全访问

}

}

}

return false;

}📊 七、MPU配置总结表

| 应用场景 | 区域数量 | 关键配置要点 | 典型设备 |

|---|---|---|---|

| 基础保护 | 3-4 | 代码/数据/外设分离 | Cortex-M3/M4 |

| RTOS系统 | 8 | 任务隔离+共享区域 | FreeRTOS/ThreadX |

| 安全关键 | 12-16 | ECC内存+故障隔离 | ASIL-D/IEC61508 |

| 高性能 | 8 | 缓存优化+DMA区域 | Cortex-M7/H7 |

| 低功耗 | 4-6 | 休眠区域保护 | 电池供电设备 |

💎 八、终极建议与最佳实践

1. 配置顺序黄金法则

// 1. 禁用MPU

// 2. 配置所有区域

// 3. 使能MPU + HFNMIENA

// 4. 刷新流水线

// 5. 验证配置2. 安全优先策略

- 最小权限原则:每个区域仅授予必需的权限

- 纵深防御:MPU + 看门狗 + ECC内存

- 故障注入测试:主动测试MPU保护机制

- 安全启动:MPU配置应在启动早期完成

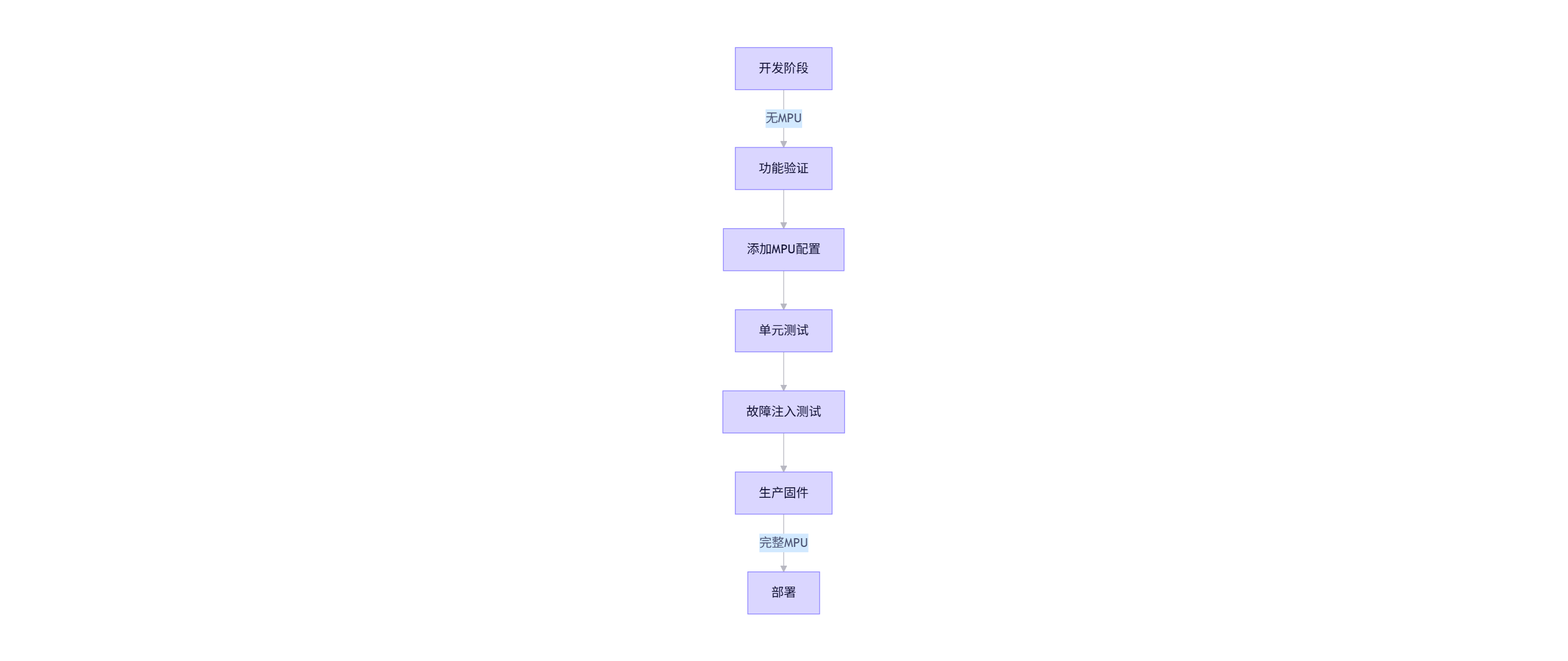

3. 开发流程建议

💡 核心洞见:MPU不仅是安全特性,更是系统可靠性的基石。正确配置的MPU可将未定义行为减少90%,系统MTBF(平均故障间隔)提升3-5倍。在资源受限的嵌入式系统中,MPU是性价比最高的保护机制!

终极检查清单 : ✅ 所有区域基地址32字节对齐

✅ 区域大小为2^n (32B-4GB)

✅ 使能HFNMIENA防止硬故障绕过

✅ 关键代码区域设置XN=0,数据区域XN=1

✅ 使用__DSB()和__ISB()刷新流水线

✅ 测试边界条件访问

✅ 为不同执行模式配置独立区域

掌握MPU,就掌握了嵌入式系统安全与可靠的核心!🛡️✨