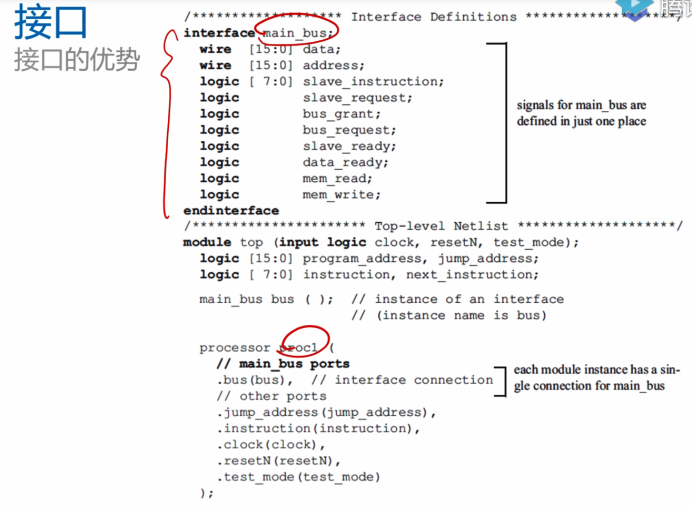

interface可以实现一定的逻辑。

interface信号端口变化,后期维护容易。

module的所有语法适合interface。

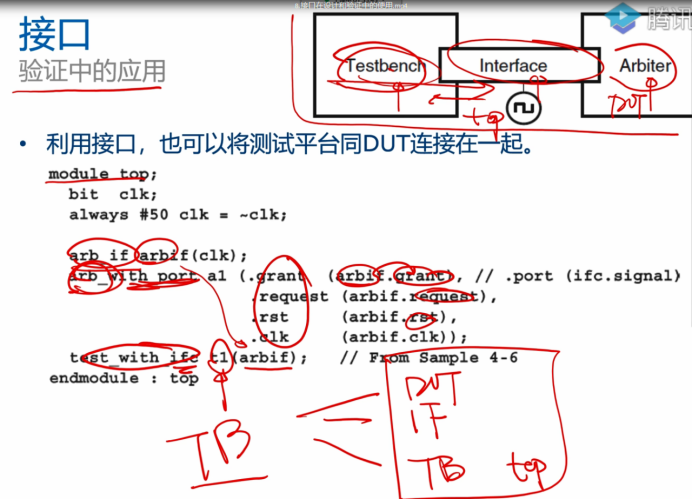

Modport设计用的多,验证常用clocking block。

bash

// TODO-1 understand how the interface is defined and instantied

// TODO-2 check how to define methods inside interface and call them internally or externally

// TODO-3 understand how to prepare transactions, drive them and monitor them

module interface_type;

typedef struct {

bit [7:0] addr;

bit [31:0] data;

bit write;

int id;

} trans_t;

//struct print utility function

function void trans_print(trans_t t, string name = "trans");

string s;

s = $sformatf("%s struct connect is as below \n", name);

s = $sformatf("%s\taddr = 'h%2x \n", s, t.addr);

s = $sformatf("%s\tdata = 'h%8x \n", s, t.data);

s = $sformatf("%s\twrite = 'b%0b \n", s, t.write);

s = $sformatf("%s\tid = 'h%8x \n", s, t.id);

$display("%s", s);

endfunction

//使用示例

initial begin

trans_t my_trans;

// 初始化结构体

my_trans.addr = 8'hA5;

my_trans.data = 32'h12345678;

my_trans.write = 1'b1;

my_trans.id = 32'hDEADBEEF;

// 使用打印函数

trans_print(my_trans, "my_trans");

// 使用默认名称

trans_print(my_trans);

end

//预期输出

my_trans struct content is as below

addr = 'ha5

data = 'h12345678

write = 'b1

id = 'hdeadbeef

trans struct content is as below

addr = 'ha5

data = 'h12345678

write = 'b1

id = 'hdeadbeef

/*格式说明符:

'h%2x: 十六进制显示,固定2位宽度

'h%8x: 十六进制显示,固定8位宽度

'b%0b: 二进制显示,自动宽度*/

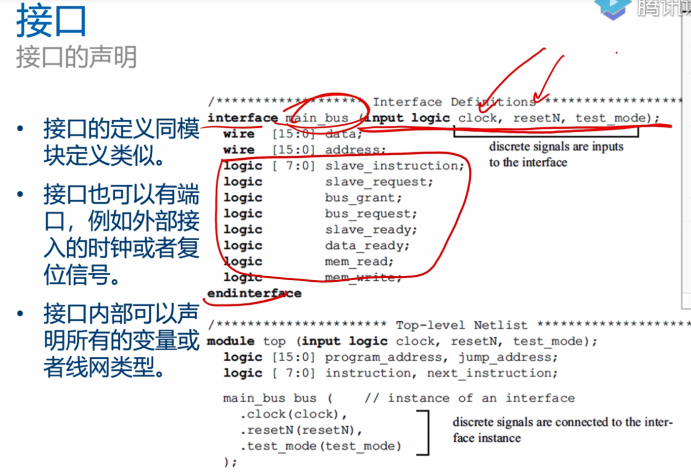

interface intf1;

logic [7:0] addr;

logic [31:0] data;

logic write;

int id;

// transaction drive task

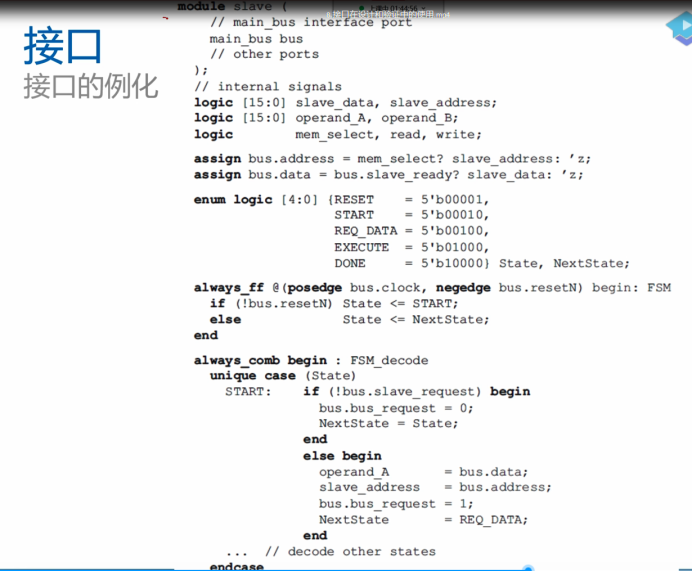

task drive_trans(trans_t t);

addr <= t.addr ;

data <= t.data ;

write <= t.write;

id <= t.id ;

endtask

// transaction monitor task

task mon_trans(output trans_t t);

t.addr = addr ;

t.data = data ;

t.write = write;

t.id = id ;

endtask

endinterface

intf1 if1();

initial begin

trans_t trans_in[3], trans_mon[3];//数组

// stimulus preparation

trans_in = '{'{'h10, 'h1122_3344, 'b1, 'h1000}

,'{'h14, 'h5566_7788, 'b0, 'h1001}

,'{'h18, 'h99AA_BBCC, 'b1, 'h1002}

};

foreach(trans_in[i]) begin

#10;

// stimulus drive

if1.drive_trans(trans_in[i]);

trans_print(trans_in[i], $sformatf("trans_in[%0d]",i));

#10;

// stimulus monitor

if1.mon_trans(trans_mon[i]);

trans_print(trans_mon[i], $sformatf("trans_mon[%0d]",i));

// transaction comparison

if(trans_in[i] === trans_mon[i])

$display("trans_in[%0d] === trans_mon[%0d]", i, i);

else

$error("trans_in[%0d] !== trans_mon[%0d]", i, i);

end

end

/*预期输出

trans_in[0] struct content is as below

addr = 'h10

data = 'h11223344

write = 'b1

id = 'h00001000

trans_mon[0] struct content is as below

addr = 'h10

data = 'h11223344

write = 'b1

id = 'h00001000

trans_in[0] === trans_mon[0]

// ... 重复对于索引1和2*/

添加断言检查:

// 在接口中添加断言

assert property (@(posedge clk) !$isunknown(addr)) else

$error("Address has unknown bits");

添加覆盖率收集:

// 在接口中添加覆盖组

covergroup trans_cg;

coverpoint addr { bins low = {[0:127]}; bins high = {[128:255]}; }

coverpoint write;

cross addr, write;

endgroup

endmodule