详细分析硬件纹波对DDR运行稳定性的影响及解决方案

文章目录

- 详细分析硬件纹波对DDR运行稳定性的影响及解决方案

-

- [1. 技术背景说明](#1. 技术背景说明)

-

- [1.1 DDR内存工作原理](#1.1 DDR内存工作原理)

- [1.2 硬件纹波定义](#1.2 硬件纹波定义)

- [2. 纹波影响机理](#2. 纹波影响机理)

-

- [2.1 电源纹波影响](#2.1 电源纹波影响)

-

- [2.1.1 VDD/VDDQ电源波动与时序裕量](#2.1.1 VDD/VDDQ电源波动与时序裕量)

- [2.1.2 纹波频率的谐波干扰](#2.1.2 纹波频率的谐波干扰)

- [2.2 信号完整性纹波](#2.2 信号完整性纹波)

-

- [2.2.1 传输线反射造成的振铃](#2.2.1 传输线反射造成的振铃)

- [2.2.2 串扰引起的纹波叠加](#2.2.2 串扰引起的纹波叠加)

- [3. 测试验证方法](#3. 测试验证方法)

-

- [3.1 实验室测量手段](#3.1 实验室测量手段)

-

- [3.1.1 示波器测试规范](#3.1.1 示波器测试规范)

- [3.1.2 关键测试点](#3.1.2 关键测试点)

- [3.2 量化评估指标](#3.2 量化评估指标)

-

- [3.2.1 纹波容忍度表格](#3.2.1 纹波容忍度表格)

- [3.2.2 误码率测试方案](#3.2.2 误码率测试方案)

- [4. 优化设计方案](#4. 优化设计方案)

-

- [4.1 电源设计](#4.1 电源设计)

-

- [4.1.1 多层板叠层建议](#4.1.1 多层板叠层建议)

- [4.1.2 去耦电容布局](#4.1.2 去耦电容布局)

- [4.2 布线规范](#4.2 布线规范)

-

- [4.2.1 阻抗控制要求](#4.2.1 阻抗控制要求)

- [4.2.2 等长匹配规则](#4.2.2 等长匹配规则)

- [5. 故障案例分析](#5. 故障案例分析)

-

- [5.1 典型故障波形图](#5.1 典型故障波形图)

- [5.2 整改前后对比](#5.2 整改前后对比)

- [6. 参考文献](#6. 参考文献)

1. 技术背景说明

1.1 DDR内存工作原理

DDR (Double Data Rate) SDRAM 是一种在时钟信号的上升沿和下降沿都能进行数据传输的同步动态随机存取存储器。其核心技术特征包括:

- 双沿触发 (Double Data Rate) :

DDR利用时钟信号(CLK)的上升沿和下降沿传输数据,从而在同等时钟频率下将数据传输速率翻倍。 - 预取机制 (Prefetch Architecture) :

DDR采用预取技术并行读取数据。例如,DDR3采用8n-prefetch,即内部核心频率是I/O频率的1/8,每次读写操作内部并行传输8位数据。

R a t e I O = R a t e C o r e × P r e f e t c h Rate_{IO} = Rate_{Core} \times Prefetch RateIO=RateCore×Prefetch - 突发传输 (Burst Transfer) :

一旦寻址完成,DDR可以连续读写多个数据(突发长度BL),减少寻址开销,提高总线利用率。

1.2 硬件纹波定义

硬件纹波是指叠加在直流电源或信号上的交流成分。

- 时域视角: 表现为电压随时间的周期性或随机波动(Peak-to-Peak Voltage)。主要由开关电源(DCDC)的开关动作、负载瞬态变化(Load Transient)引起。

- 频域视角: 包含开关频率基波及其高次谐波。信号完整性(SI)问题(如反射、串扰)也会在信号上引入高频纹波。

2. 纹波影响机理

2.1 电源纹波影响

DDR的电源网络(PDN)主要包括 VDD (核心电压)、VDDQ (IO电压) 和 VPP (泵浦电压)。

2.1.1 VDD/VDDQ电源波动与时序裕量

电源电压的波动直接改变了晶体管的翻转速度。

- 电压降低: 晶体管驱动能力下降,信号上升/下降沿变缓,导致 Setup Time (建立时间) 不足。

- 电压升高: 信号传输变快,可能导致 Hold Time (保持时间) 违例。

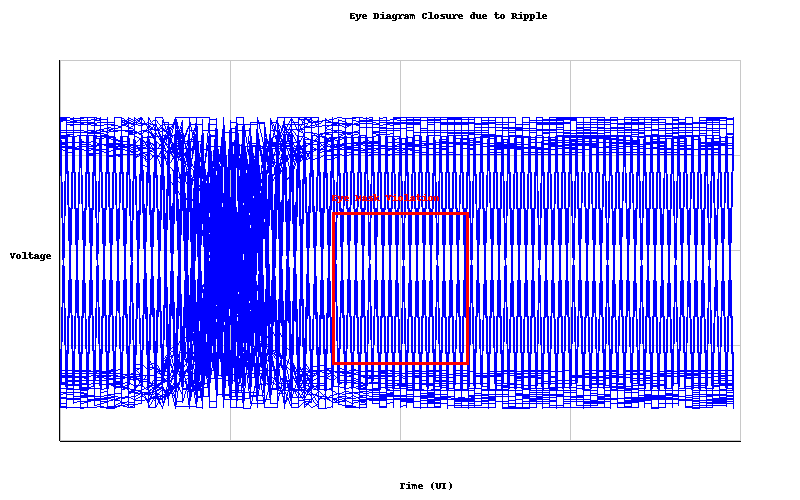

下图展示了电源噪声如何导致眼图闭合:

图2-1: 电源纹波导致的抖动与眼图闭合示意图

2.1.2 纹波频率的谐波干扰

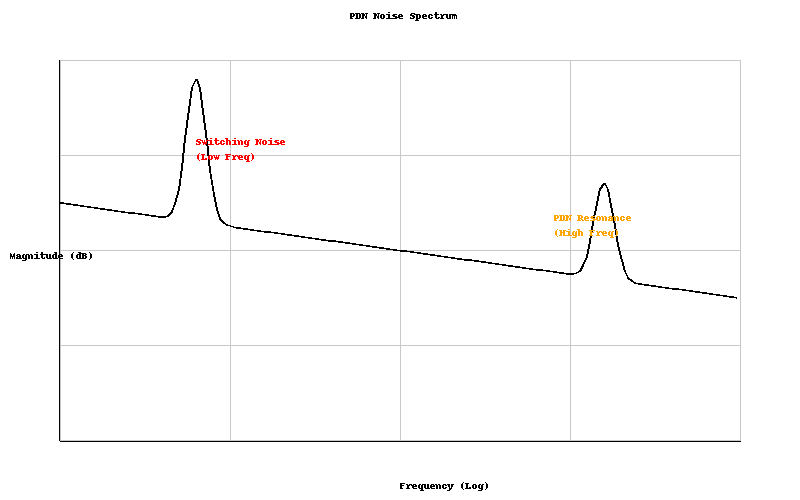

- 低频纹波 (<1MHz): 通常由电源环路响应慢导致,表现为长周期的电压跌落,可能引起突发性的读写错误。

- 高频纹波 (>100MHz): 通常由去耦电容不足引起,容易耦合到时钟或数据线上,形成抖动(Jitter)。

图2-2: 电源纹波频谱分析示例

2.2 信号完整性纹波

2.2.1 传输线反射造成的振铃

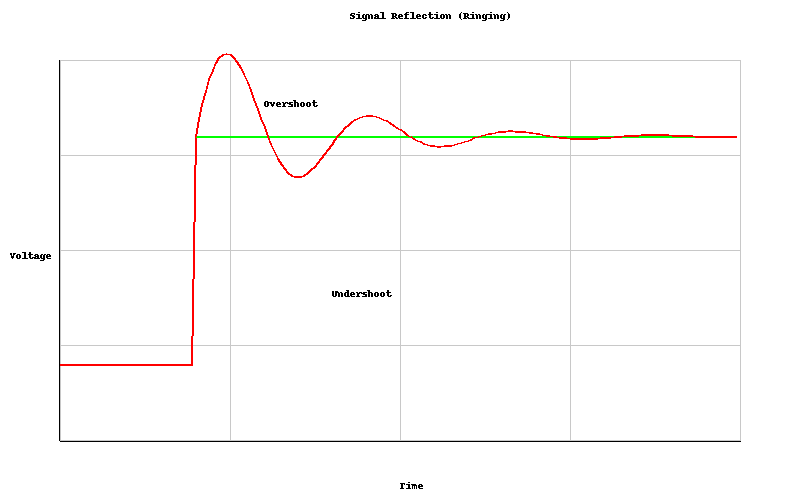

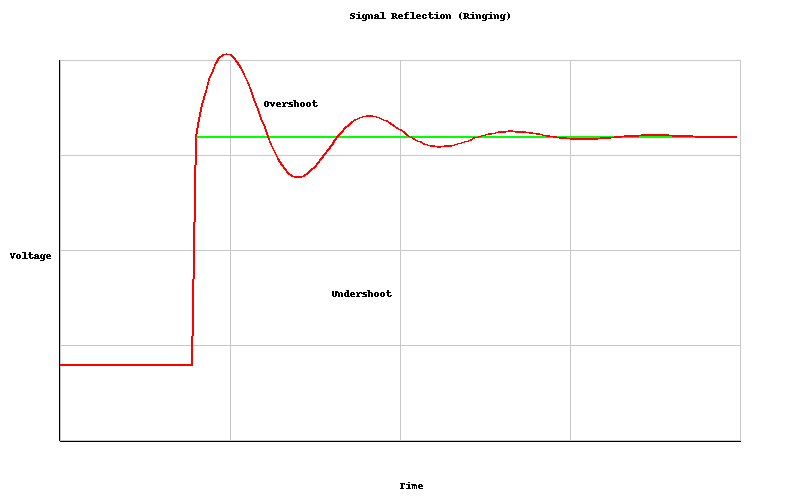

当PCB走线阻抗( Z 0 Z_0 Z0)与源端/终端阻抗不匹配时,信号会在传输线上来回反射,形成过冲(Overshoot)、下冲(Undershoot)和振铃(Ringing)。

- 过冲: 可能击穿IO缓冲器。

- 振铃: 导致逻辑电平在阈值附近波动,产生误触发。

图2-3: 阻抗不匹配导致的信号振铃波形

2.2.2 串扰引起的纹波叠加

当两条信号线靠得太近时,变化的电磁场会在相邻线上感应出噪声电压。

- 近端串扰 (NEXT): 在驱动端感应到的噪声。

- 远端串扰 (FEXT): 在接收端感应到的噪声,直接叠加在有效信号上,破坏信号完整性。

3. 测试验证方法

3.1 实验室测量手段

3.1.1 示波器测试规范

- 带宽要求 : 对于DDR4-3200,建议示波器带宽 ≥ 4 G H z \ge 4GHz ≥4GHz,探头带宽 ≥ 4 G H z \ge 4GHz ≥4GHz。

- 探头接地 : 必须使用短接地弹簧 或焊接探头,严禁使用长接地夹(会引入巨大的寄生电感,导致测量出的纹波虚高)。

3.1.2 关键测试点

- VDD/VDDQ: 在颗粒(DRAM)背面的去耦电容处测量,最接近负载端。

- VREF (参考电压) : 必须极其稳定,通常要求纹波 ≤ 1 % × V D D \le 1\% \times VDD ≤1%×VDD。

- DQ/DQS: 在DRAM颗粒引脚处进行探测(End-of-Line)。

3.2 量化评估指标

3.2.1 纹波容忍度表格

| 参数项 | DDR3 (1.5V) | DDR4 (1.2V) | DDR5 (1.1V) | 备注 |

|---|---|---|---|---|

| VDD 容差 (DC+AC) | ± 75 m V \pm 75mV ±75mV (5%) | ± 60 m V \pm 60mV ±60mV (5%) | ± 33 m V \pm 33mV ±33mV (3%) | 包含纹波峰峰值 |

| VREF 纹波 | ≤ 15 m V \le 15mV ≤15mV | ≤ 12 m V \le 12mV ≤12mV | N/A (Internal) | VREF极其敏感 |

3.2.2 误码率测试方案

使用压力测试软件验证稳定性:

- MemTest86: BIOS级内存测试,覆盖全地址空间。

- Stressapptest (Google): 模拟高负载随机读写,检测总线噪声引起的数据翻转。

4. 优化设计方案

4.1 电源设计

4.1.1 多层板叠层建议

电源平面(Power Plane)和地平面(Ground Plane)应紧耦合(相邻层),形成平板电容效应,提供优良的高频回路。

Signal (Top) GND Signal (Stripline) Power (VDD/VDDQ) GND Signal (Bottom)

图4-1: 推荐的6层板叠层结构

4.1.2 去耦电容布局

- 组合策略: 大容量电容(Bulk, 10uF+)滤除低频,小容量电容(0.1uF, 0.01uF)滤除高频。

- 布局原则: 电容应尽可能靠近DRAM颗粒的电源引脚,过孔打在焊盘侧边(Fanout),减小寄生电感(ESL)。

图4-2: 去耦电容布局示意图

4.2 布线规范

4.2.1 阻抗控制要求

| 信号类型 | 单端阻抗 ( Z 0 Z_0 Z0) | 差分阻抗 ( Z d i f f Z_{diff} Zdiff) | 备注 |

|---|---|---|---|

| Data (DQ/DQS/DM) | 50 Ω ± 10 % 50 \Omega \pm 10\% 50Ω±10% | 100 Ω ± 10 % 100 \Omega \pm 10\% 100Ω±10% | ODT匹配通常为 120 Ω 120\Omega 120Ω |

| Address/Command | 40 − 50 Ω 40-50 \Omega 40−50Ω | N/A | 采用Fly-by拓扑 |

| Clock (CK) | N/A | 100 Ω ± 10 % 100 \Omega \pm 10\% 100Ω±10% | 必须差分走线 |

4.2.2 等长匹配规则

- Byte Lane 内部 : DQ与DQS长度误差 ≤ 10 − 20 m i l \le 10-20 mil ≤10−20mil。

- Byte Lane 之间 : 组间误差可放宽至 ≤ 500 m i l \le 500 mil ≤500mil (DDR3/4有Write Leveling支持)。

- Clock与Addr/Cmd: 必须严格匹配,确保时钟沿能正确采样命令。

5. 故障案例分析

5.1 典型故障波形图

某工控板卡DDR3运行不稳定,经常死机。示波器测量VDDQ电源纹波发现异常尖峰。

- 现象 : VDDQ纹波高达 120 m V p p 120mV_{pp} 120mVpp,且伴随DCDC开关频率的振荡。

- 原因: DCDC电感选型偏小,且输出电容离DRAM颗粒太远。

图5-1: 整改前的异常纹波波形

5.2 整改前后对比

优化措施:

- 更换更大感值的功率电感。

- 在DRAM颗粒每个电源引脚处增加一颗 0.1 u F 0.1uF 0.1uF 0402电容。

- 优化PCB,加粗电源走线,缩短回流路径。

| 测试项 | 整改前 | 整改后 | 改善幅度 |

|---|---|---|---|

| VDDQ 纹波 | 120 m V 120 mV 120mV | 35 m V 35 mV 35mV | 70% |

| MemTest86 | 10分钟报错 | 24小时无错 | Pass |

6. 参考文献

- JEDEC Standard No. 79-4B, "DDR4 SDRAM Standard", 2017.

- Micron Technical Note TN-00-08, "Power Integrity Guidelines for DDR4 SDRAM".

- Eric Bogatin, "Signal and Power Integrity - Simplified", 3rd Edition.