摘要

近年来,将片上系统(SoC)拆分为多个更小的Chiplet并嵌入单个封装中,因在数字电路中得到更广泛应用而备受关注。尽管这种方式具备降低干扰、抵御环境影响以及突破 "互连鸿沟" 等优势,但其在集成模拟电路中的应用进度却无法与数字设计相媲美。造成这一现象的原因可能是行业过度依赖单芯片封装 ------ 这类封装优先考虑高频性能,而非集成密度。为此,本文展示了首个基于嵌入式晶圆级球栅阵列(eWLB)封装的模块化系统方案,该方案在集成密度和性能两方面均未做出妥协。仅受最大封装尺寸限制,通道数量可根据具体应用需求调整,这使得该系统既能针对低成本、低功耗应用场景进行小型化设计,也能支持大规模多输入多输出(MIMO)技术。作为示例,本研究制造了一款 4×4 雷达系统级封装(SiP),其尺寸仅为 7.8 毫米 ×8.8 毫米,内含五颗采用 130 纳米 B11HFC 硅锗(SiGe)工艺的Chiplet。该封装包含一个中央压控振荡器(VCO),为四个设计相同的收发器供电,这些收发器可通过封装布局配置为接收器或收发器。这种配置完全基于封装实现,使得芯片设计可重复利用,大幅缩短了研发周期。此外,还可根据现有制造条件和经济考量,对Chiplet进行同质或异质替换。该雷达系统配备 15.6 dBi 梳状线天线,经验证,在 76--77 GHz 频段内,可实现最远 36 米的测距范围和 ±30° 的方位角目标检测。与单芯片解决方案不同,这种新颖的Chiplet方案将温度热点分散为多个更小的局部高温区域。尽管这有助于散热,但也带来了额外的热机械和电磁方面的挑战。因此,本文通过详细研究焊球布局和封装与印刷电路板(PCB)的接口,解决了性能与可靠性之间的平衡问题。

1. 引言

数字工艺节点缩放陷入停滞,推动行业范式从单芯片解决方案转向多Chiplet封装。学术界(如美国国防高级研究计划局,DARPA)和工业界(如 AMD 的 Zen 处理器、英特尔的 Stratix-10 现场可编程门阵列)均积极研发系统级封装(SiP),借助英特尔的嵌入式多芯片互连桥接(EMIB)、台积电的集成扇出(InFO)、安靠的动态对称多球栅阵列(DSMBGA)以及英飞凌的 eWLB 等技术,整合已知合格芯片(KGD)和异质Chiplet。这些方案可根据应用场景选用不同技术或工艺节点来优化 SiP,或摆脱对单一供应商的依赖,从而丰富产品线。该方法不仅能通过复用成熟芯片降低成本,还能减小芯片尺寸,提升良率、可靠性和互连密度。

将这一理念拓展至混合信号领域,2.5D/3D SiP 可同时实现数字和模拟功能,且不牺牲隔离度、密度或性能。对多条重分布层(RDL)的精准控制,加之 RDL 包覆介质的高品质因数(Q 值),还能实现天线封装一体化(AiP)、线圈、耦合器或微机电系统(MEMS)等无源器件的集成。将这些元件(包括芯片和互连结构)嵌入封装,可使其免受环境损害,并提高Chiplet密度。与此同时,所采用的焊点简化了封装厂外的组装流程,且相比易脆的键合线连接,可靠性更高。这一点对高频接口尤为重要 ------ 高频接口的性能与反射和互连可预测性密切相关。键合线的长度不确定性会导致电感值难以确定,且需采用芯片腔体等昂贵制造工艺来缩短连接长度。而英飞凌的嵌入式晶圆级封装(eWLB)等高频封装技术,即便在 76--81 GHz 的车载频段下,也能克服上述问题,不过是以牺牲部分集成密度为代价换取更高性能。eWLB 技术自 2006 年开始发展,2008 年首次出现采用该封装的电路;2012 年,相关研究分别展示了首款基于 eWLB 的车载发射机、接收机和收发机芯片 - 封装协同设计方案。后续研究主要聚焦于提升工作频率、改善 AiP 性能以及研究封装可靠性。然而,与数字领域类似的多Chiplet方案却大多被忽视,Chiplet设计复用、输入 / 输出端口(如电源 / 地)共享、利用高 Q 值封装实现低损耗Chiplet接口,以及相比多芯片系统降低成本和尺寸等优势均未得到挖掘。本研究旨在弥补这一不足,提出一种可扩展的 4×4 雷达系统,其通道数量仅受封装技术最大尺寸限制。

本文第二节将介绍 SiP 中压控振荡器(VCO)和双馈电收发器(TRx)的Chiplet设计;第三节详细阐述封装的构成,并从信号分布和互连角度分析电磁与热机械考量因素;第四至五节介绍雷达系统前端和后端的设计;第六节给出实测性能;最后,第八节对全文进行总结。

2. 雷达单片微波集成电路(MMIC)

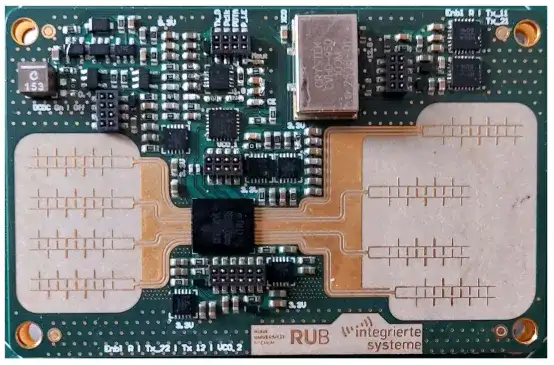

为最大化可扩展性并实现高频、低复杂度的封装设计,本研究选用仅包含单个 VCO 和一款 TRx 设计的芯片组。这些Chiplet功能独立,可单独测试,且能复用成熟的芯片设计(如本研究中参考的 [19]),这使得芯片与封装的设计可在很大程度上独立进行,简化了系统研发流程。不过,仍需进行少量兼容性调整,例如增加对准标记、增大焊盘尺寸(确保重分布层过孔可靠放置)以及设置芯片热接触点(在封装中通过焊球连接)。此外,本研究在 TRx Chiplet内部设计了一种新型本地振荡器(LO)馈电网络,通过从芯片不同边缘馈电,可基于封装布线对 TRx 进行重构。所有Chiplet均采用英飞凌 130 纳米 B11HFC 工艺制造,其特征频率fT=250 GHz,最大振荡频率fmax=370 GHz,可直接兼容 eWLB 封装,且工艺成熟度高。

2.1 压控振荡器(VCO)

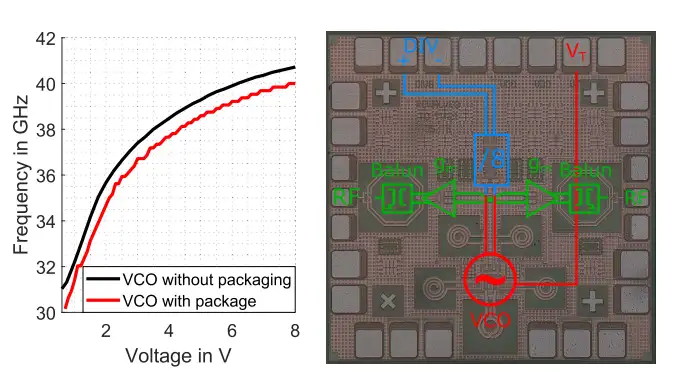

图 1 所示的 VCO Chiplet可在 1--8 V 调谐电压VT下产生 30--42 GHz 的本振(LO)信号,该频率与 VCO 谐振腔的 Q 值密切相关。变容二极管本身具有高 Q 值,但其位于芯片堆叠结构中,导致外露电感极易受外部因素影响。封装介质覆盖整个芯片表面,会改变有效介电常数,便是影响因素之一。如图 1 所示,介电常数的变化会导致约 0.7 GHz 的频率偏移。这些测量在 VCO 的分频输出端(图 1 中标注为 "/8")进行,该端口为锁相环(PLL)提供频率参考信号。

图1、930×930µm2压控振荡器(VCO)MMIC的封装和非封装调谐曲线和显微照片

为同时给多个 TRx 馈电,VCO 输出被分成两条对称路径,每条路径末端均设有缓冲级,可在 38 GHz 时将输出功率提升至 3.4 dBm,并为 TRx 提供固定阻抗。此外,还采用变压器巴伦以确保负载无关运行,并实现差分信号至单端信号的转换,这一点将在第三节进一步说明。由于缺乏分接电路,无法确定封装对输出功率以及 38 GHz 下−102 dBc/Hz 相位噪声的影响,但介质材料的低损耗角正切值不太可能导致输出功率大幅偏离。即便存在几 dB 的功率损耗,根据本振分配网络的仿真结果,仍有足够余量驱动多个 TRx 进入饱和状态。

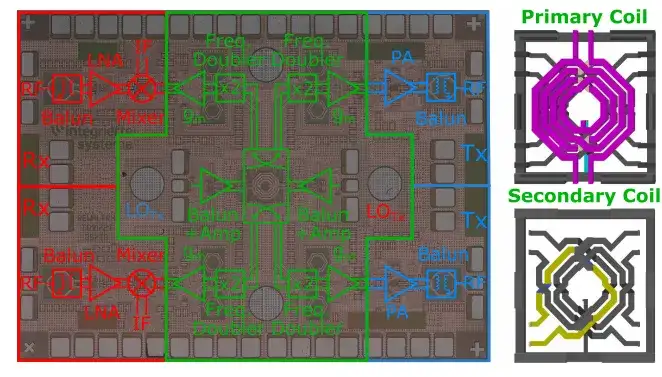

2.2 双馈电收发器(TRx)

图 2 所示的Chiplet集成了发射(Tx)和接收(Rx)通道,减少了所需设计的数量,兼具成本、灵活性和热性能优势。根据天线接口和封装布线能力,两个带单端输出的 Rx/Tx 通道分别位于Chiplet相对的边缘,由Chiplet中央的共用本振(LO)分配网络,以及功率放大器(Tx 通道)或下混频器与低噪声放大器(Rx 通道)组成。由于任一 TRx Chiplet仅使用一种通道类型(Tx/Rx),因此其供电被分离,以实现独立运行。未使用的通道部分被重新设计为输入 LO 信号,并通过焊点(与Chiplet顶层金属层大面积连接)实现热释放。这使得封装可通过馈电方向确定通道类型,具备可重构性。不过,两种馈电方向均需适配 VCO 的 38--40.5 GHz 信号,这一点通过图 2 所示的基于变压器的设计实现。变压器初级线圈延伸至两个差分输入端,其中一个输入端的布线长度多出一个绕组。为适配差分工作模式,封装的单端 LO 信号先通过有源巴伦转换为差分信号,再经缓冲级校正相位失衡,同时确保未使用输入端的反向隔离。

图2、1964×1448µm2 TRx MMIC的显微照片和拓扑结构

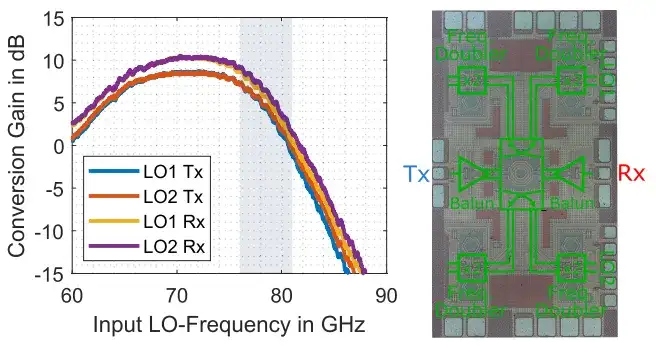

图 3 所示的分接芯片对整个 LO 分配网络的验证结果表明,无论通道(标注为 "LO1"/"LO2")如何,性能均相近,仅 Rx/Tx 模式间存在微小差异。该差异可归因于初级线圈绕组长度不同,导致其 Q 值降低,进而使倍频器的匹配特性失真。

对整个 Tx 链路的实测结果显示,在目标频段内,去嵌入后的最大输出功率为 8--8.8 dBm。由于缺乏 W 波段噪声源,无法对 Rx 链路进行类似实测;仿真结果表明,其噪声系数(NF)为 8.4--10 dB,电压增益为 34.2--31.7 dB。

图3、分析LO馈电的MMIC及其性能

3. 封装概述

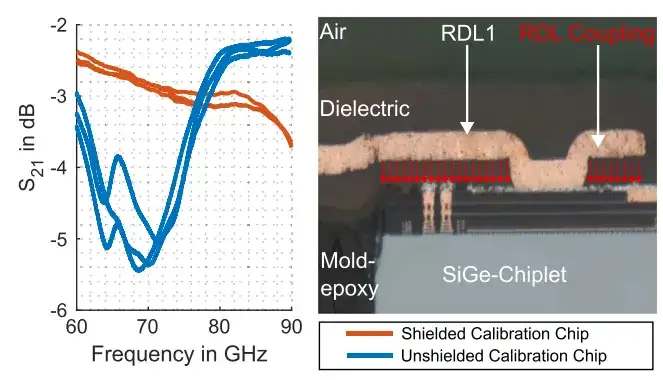

重分布层(RDL)与Chiplet顶层金属层间距较近,二者间的电容耦合可能导致封装性能下降,且下降程度与 LO 输入端距芯片边缘的距离成正比。图 4 通过评估共面(无屏蔽)和接地共面(有屏蔽)RDL 直通校准芯片的损耗,验证了这一现象:无屏蔽情况下,实测直通损耗偏差较大,而有屏蔽Chiplet则呈现出预期的单调损耗特性。尽管存在额外损耗,但第一节提及的功率余量足以避免对 TRx 性能造成显著影响。不过,为实现更可预测的 RDL 性能,仍建议对 RDL 进行屏蔽,使其与芯片表面隔离。

图4、带和不带GND平面屏蔽的测量校准芯片S21

如图 4 剖面图所示,Chiplet以倒装芯片形式嵌入英飞凌 eWLB 封装的环氧模塑化合物中。锥形过孔将芯片焊盘连接至两层重分布层(RDL)中的第一层,并实现各 RDL 之间的互连。均匀涂覆的介质作为各层之间的绝缘体,由于工艺未做平坦化处理,介质厚度会随 RDL 或Chiplet的分布情况局部变化,导致 RDL 呈现三维拓扑结构(见图 5),若设计时未明确考虑这一点,可能会改变预期的传导方式。以传输线为例,若选择第一层 RDL 作为信号层,上层 RDL 中的接地层会将其包裹(如 [24] 所述),使其特性近似接地共面波导(GCPW)。因此,设计时要么需考虑层叠结构,要么需利用共面波导(CPW)/ 差分波导的面内精度。后者还能减少翘曲、降低表面效应(如粗糙度或电容性线缩短)的影响,并整体减少制造过程中的故障点(如过孔偏移)。

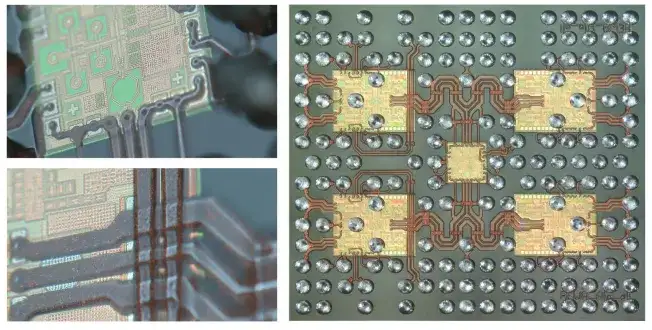

图5、整个7.8 mm×8.8 mm 4×4雷达封装的显微照片,突出显示芯片/RDL重叠

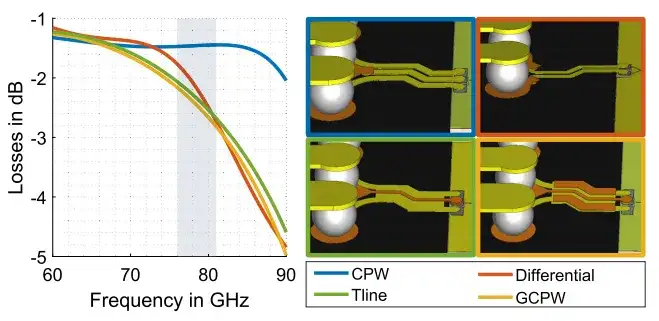

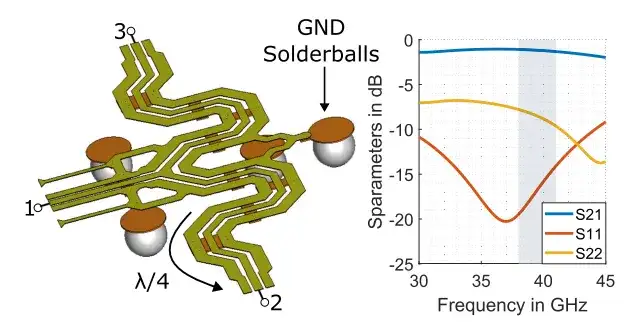

对比图 6 中相同长度的不同封装 - PCB 接口,共面波导(CPW)在高频段的性能优于其他方式;而在低频段,所有波导的损耗趋于一致,此时差分传输线因面积消耗降低 60% 而更具优势。因此,所有中频(IF)输出均采用差分设计,而高频接口则采用共面波导(CPW),这一设计也适用于 VCO 输出至 TRx 的信号分配。VCO 信号分配网络的设计与威尔金森功分器高度相似:初始为 50Ω 接口,随后分为两条 λ/4 长度的 70Ω 共面波导(CPW),并通过周期性短接 CPW 的两条接地线维持可靠接地。图 7 所示的最终设计损耗为 1.1 dB,在目标频段内的偏差仅约 0.25 dB。端口 2 和端口 3 的匹配性能下降,主要归因于省去了基于传输线的信号功分器中常用的 50Ω 终端电阻 ------ 出于对互连寄生效应的顾虑,且 TRx 变压器已提供高隔离度,因此未设置该电阻。由于缺乏封装分接结构,上述结果未通过实测验证。

图6、不同过渡段及其3D模型的损失

图7、带有颜色编码RDL的封装内信号分离器的3D模型及其3D模拟性能

威尔金森功分器还为 VCO 提供接地连接,这是因为封装中心空间有限。尽管采用更小的焊球和节距(而非本研究中使用的 C4 球栅阵列,节距 500 μm,直径 300 μm)可能缓解这一问题,但会降低工艺可靠性并增加成本。所有焊点的焊盘尺寸也略有增大,以确保回流焊后具备良好的附着力。

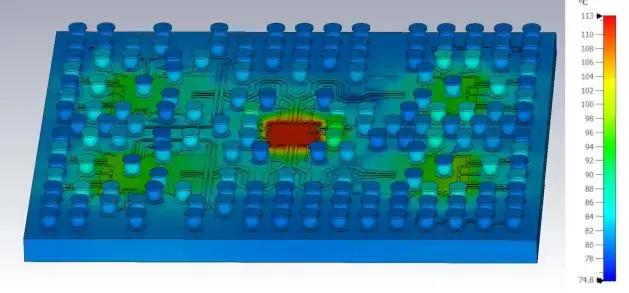

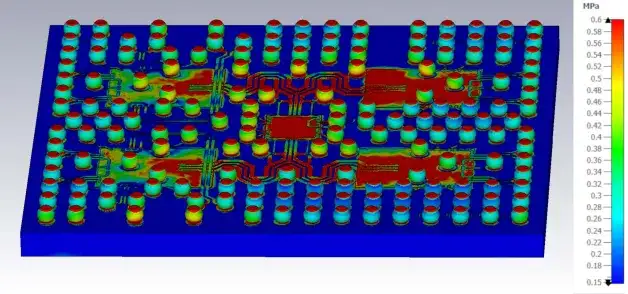

Chiplet被封装后,其直流功耗产生的热量可能难以有效散出。类似 PCB 在无主动冷却的情况下,基板温度经热像仪测量已超过 60℃。因此,本研究针对所有Chiplet同时耗电的最坏情况,对雷达封装进行了热稳态仿真(简化了 PCB 连接)。但在实际测量中,由于采用时分复用(TDM)技术且未使用的 TRx 处于关闭状态,这种最坏情况并不会出现。VCO 的功耗为 165 mW(3.3 V 供电,电流 50 mA),热仿真(图 8)显示其最高温度可达 113℃。尽管 Rx/Tx 的功耗(分别为 561 mW/891 mW)高于 VCO,但三个热接触点提升了散热效率,使其温度分别降至约 93.25℃/89.4℃。这些热接触点通过增大的过孔直接连接Chiplet顶层金属层(与接地端相连),并贯穿多个金属层和Chiplet衬底,助力热量传递。凸点下金属化层(UBM)进一步提升了封装的热导率和电导率,因其大尺寸垂直连接缩短了Chiplet与 PCB 之间的距离。

图8、使用CST MPhysics Studio对整个软件包进行热模拟

通过在封装上方增加散热鳍片扩大暴露面积,也可降低温度,但由于当前温度处于预期范围,本研究未开展相关探索。

应力是封装的另一主要失效点,尤其受模塑环氧树脂和介质厚度、扇入触点或凸点下金属化层(UBM)等因素影响。不同材料的温度诱导膨胀速率差异,可能导致封装变形、焊球开裂。大面积封装通过大量焊点与 PCB 连接,可抵抗这种膨胀,但将封装尺寸控制在 10 毫米 ×10 毫米以内,通常能确保在−40℃至 125℃温度范围内,封装互连具备较高的热机械可靠性。综合成本和射频连接长度考量,本研究将封装尺寸确定为 7.8 毫米 ×8.8 毫米,该尺寸主要由所有所需信号的扇出布局以及Chiplet间的间距决定。

为确保应力合理分布,本研究通过机械仿真优化焊球布局。图 9 的仿真结果表明,单个焊球的张力与其相邻焊球的布局相关:Chiplet或封装边缘的触点承受的载荷最大。尽管多Chiplet封装中,单个Chiplet产生的应力可分散至更多 PCB 触点,使得该现象有所缓解,但功分器周围焊球的缺失仍会影响应力分散效果。因此,本研究增加了功分器和Chiplet周围的触点数量。

图9、使用CST MPhysics Studio对整个软件包进行首次主应力模拟

电迁移是第三个主要应力源,因此应力最大的焊球未用于传输关键信号。若不遵守这一原则,重分布层(RDL)可能扩散到焊料凸点中,形成空洞并导致电阻增大,甚至开路。但将射频输出端进一步移至封装内部会损害射频性能,因此折中方案是将其布置在封装边缘(避开角落),并额外增加一排焊料凸点以支撑该布局,这也导致封装的长宽尺寸出现 1 毫米的差值。根据剩余焊球的应力严重程度,部分焊球未传输任何信号或直流电流(即虚设焊球),这一设计尤其用于封装边缘和功分器周围。

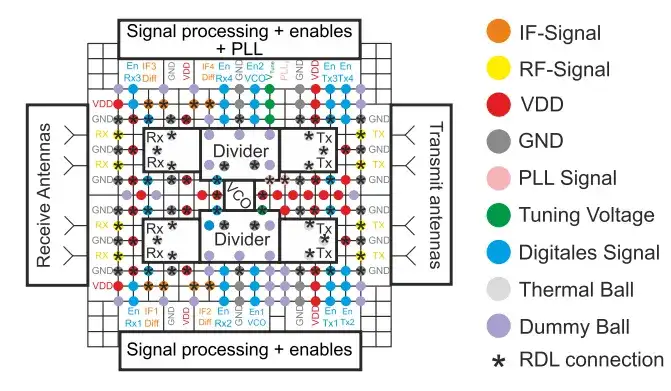

4. 射频前端

第三节所述的封装解决了芯片尺寸较小与 PCB 尺寸较大之间的互连鸿沟问题。该封装被安装在单层 127 μm 罗杰斯 RO3003 层压板 PCB 的 35 μm 覆铜焊盘上;为增强热传递、提升耐用性并保障接地供电,PCB 背面设有 1 毫米厚的铜芯。这使得 PCB 仅有顶层可用于布线,因此需进行封装 - PCB 协同设计,以合理连接控制信号、参考信号和中频(IF)信号。图 10 展示了最终的布局图,其中焊料凸点根据所传输信号进行颜色编码,连接Chiplet的焊球额外标注星号(∗)。尽管电源(VDD)标注为单一网络,但实际被拆分为四个独立子网,每个子网通过独立的低压差稳压器(LDO)连接至一个 TRx Chiplet,以减少供电波动;受封装中心空间限制,仅 VCO 与一个 Tx Chiplet共享供电。

图10、包装及其连接的平面图

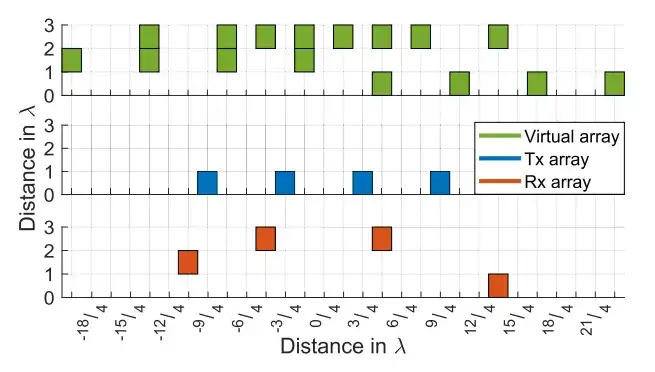

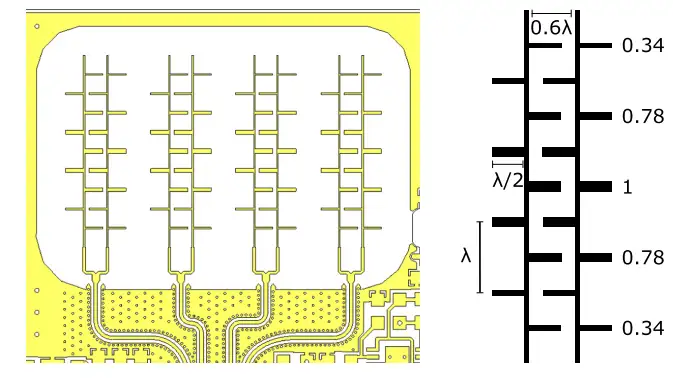

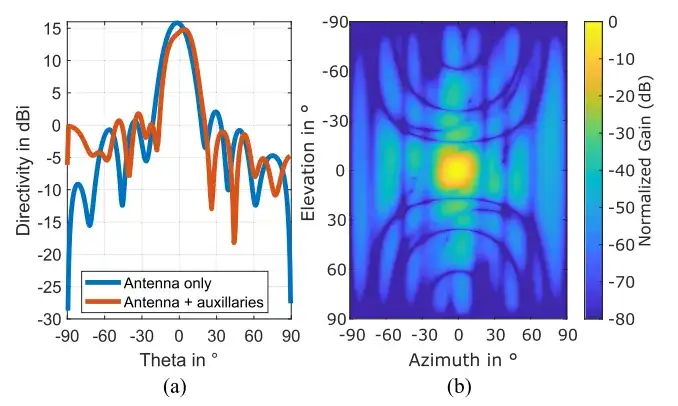

封装旁置天线的设计,决定了需采用高频罗杰斯 RT3003 基板。尽管自 2011 年起,业界就开始研发 eWLB 天线封装一体化(AiP)技术以降低材料成本,但在无封装叠层(PoP)的情况下,空间限制、增益降低以及波束成形能力有限等问题,使其在车载领域的应用受限。相比之下,本研究采用的图 11 所示 TRx 天线阵列,通过几何卷积形成稀疏虚拟阵列(天线间距dAnt>lambda2)。这种稀疏性通过最大化虚拟阵列孔径提升分辨率,但也带来了模糊度问题。窄波束宽度天线(如广泛使用的图 12 所示微带梳状线天线)可抑制 ±41° 方向的栅瓣。此类天线的开放式馈线中会形成驻波,其 λ/2 间距的短截线以交替方式排列,实现预期辐射方向图。在短截线宽度上应用泰勒分布,可进一步实现幅度调制,使波束集中在中心区域,同时向两侧逐渐衰减。由于单个天线单元无法充分限制视场(FoV)或提供足够增益,本研究将两个单元并联。图 13 (a) 展示了其组合辐射方向图,以及辅助结构(接地层、GCPW 馈线等)的影响。以图 12 中 GCPW 连接最短的第二个天线为例,PCB 导致辐射增益下降约 1 dB,加之 GCPW 路径损耗 0.7 dB;最远天线额外产生 1.2 dB 的损耗及相应相移,这些均通过校准测量以数字方式补偿。

图11、天线Rx、Tx和虚拟阵列配置

图12、利用天线短截线归一化泰勒系数的微带梳状线Tx天线阵列

对 Tx 和 Rx 阵列(采用上述天线)的仿真结果显示,当目标位于仰角 0°、方位角 0° 时,多输入多输出(MIMO)方向图如图 13 (b) 所示:Tx 功率主要集中在仰角方向,Rx 辐射主要集中在方位角方向,因此组合后的 MIMO 方向图聚焦于 ±16° 的窄视场范围内。旁瓣(图 13 (b) 中绿色区域)电平低于−30 dB,实现了高旁瓣抑制与高分辨率的设计目标。

图13、模拟(a)带/不带辅助设备的一个梳状天线的辐射方向图和(b)MIMO辐射方向图

图14、射频前端宏图

图 14 所示前端的其余部分,用于生成 76--77 GHz 频段内 82 μs 长的扫频信号(短距雷达),并与中频(IF)后端通信。设计中重点关注关键走线(4 GHz PLL 参考信号、100 MHz 晶体振荡器输出、中频输出)的间距和长度,以确保高信号完整性。此外,还配备了一个可旁路的直流 - 直流(DC-DC)转换器,用于扩展 VCO 的控制范围(见图 1),但因其 2.5 MHz 的开关频率,限制了前端的可探测距离。

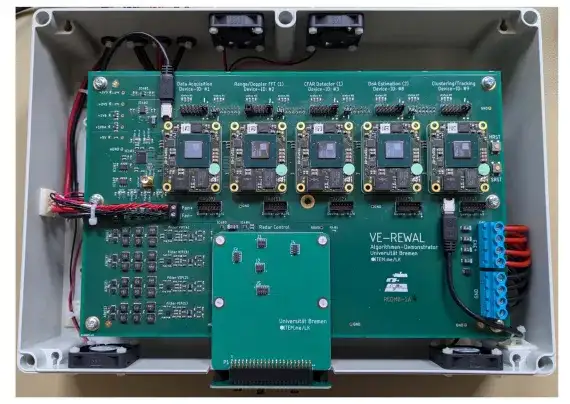

5. 后端

图 15 所示后端作为外设,连接前端、不同电源以及多个赛灵思现场可编程门阵列(FPGA)------ 这些 FPGA 各自承担部分数字信号处理(DSP)任务,形成额外的安全层。本研究聚焦硬件设计,仅使用 "数据采集" FPGA:该 FPGA 通过串行外设接口(SPI)设置前端配置和时分复用(TDM)使能,并对模数转换器(ADC)输出进行预处理,以供后续数字信号处理。为充分利用 ADC 采样范围,每个接收通道均配备专用的有源中频滤波器:初始带通滤波器衰减高频噪声和由 Rx 焊点反射 / 混响导致的低频虚假目标;恒增益放大器提升信号强度,同时根据弗里斯公式降低后续噪声影响。由于自由空间路径损耗(FSPL)呈现显著的低通特性,差分器将输出电压信号校正为 1/r 的衰减规律。后续的八阶无源切比雪夫滤波器(截止频率略低于采样频率fs的一半),可防止 12.5 MHz 的 ADC 时钟信号进入差分器反馈环路。与有源方案相比,该方案在去除高频寄生信号分量方面更具成本和空间优势。

图15、IF后端的照片

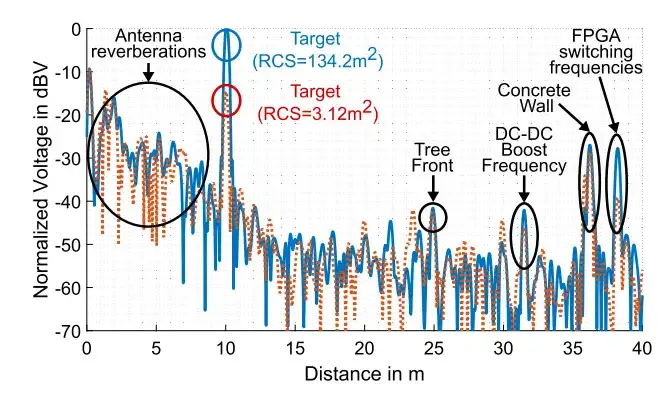

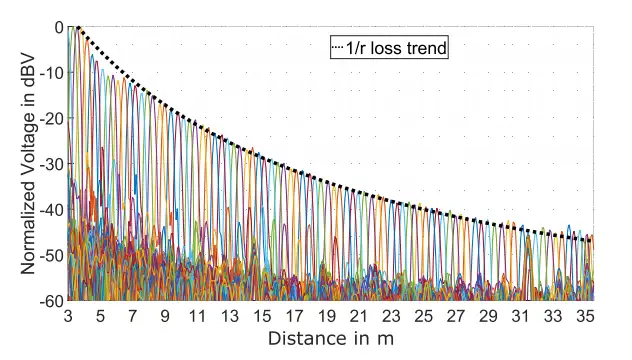

6. 雷达系统实测

本研究在波鸿鲁尔大学的混凝土封闭室外区域,对安装在 3D 打印支架(增强机械支撑)上的雷达系统进行验证。采用两种不同尺寸(边长 21 厘米 / 8.2 厘米)的角反射器,其雷达散射截面(RCS)分别为 134.2 平方米 / 3.12 平方米,确保即使在近距离测量时也不会出现饱和。图 16 所示为 10 米距离下的快速傅里叶变换(FFT)测距结果,可见 RCS 差异主要导致电压电平偏移。低频段的天线反射、31.5 米处的 DC-DC 转换器干扰(2.5 MHz)或 38.3 米处的 FPGA 开关频率干扰(3.1 MHz),是该雷达的系统性限制因素。通过增加扫频时长或降低带宽(减小线性调频斜率),可将目标移至更低中频,而系统性误差保持不变,从而突破最大测距限制;环境目标(如 36 米处的混凝土墙、25 米处的树木)也会随之移至低频段,配合更高的放大器增益,可提升其可探测性。这一点在图 17 所示的移动反射器渐变数据采集测量中尤为重要:该测量未进行平均处理,因此未利用雷达系统的相干性。与虚假目标和系统误差的波动相比,目标的幅度和相位稳定性带来的 FFT 增益较低,导致自由空间路径损耗的 1/r 衰减趋势所对应的电压电平,仅比升压频率干扰高至少 10 dB。此外,由于未使用吸波材料屏蔽后端,近距离目标的混响效应清晰可见。

图16、角反射器及其周围环境的测量

图17、移动角反射的非平均测量(RCS=134.2 m2)

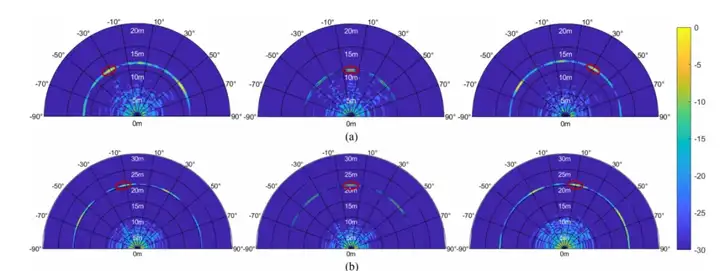

图18、RCS的距离-方位角谱=134.2 m2角反射器,(a)方位角=-30°/0°/30°,距离=10 m,(b)方位角=-10°/0℃/10°,距离=20 m

在三维空间扫描目标时,单个跟踪角度由方位角 / 仰角区间及其在虚拟天线阵列中的相对位置确定(见图 11)。车载应用中仰角天线数量较少,导致虚拟孔径小,限制了仰角方向的精准跟踪。为提升方位角分辨率,本研究舍弃所有仰角信息(假设仰角恒为 0°),以增大虚拟方位孔径(通道组合存在冗余)。图 18 汇总了同一环境下,RCS=134.2 平方米的角反射器在不同位置的二维距离 - 方位角 FFT 图谱:数据由 100 次测量平均得到,角反射器分别置于 10 米 / 20 米距离、方位角 ±6 米 /±4 米 / 0 米处。当反射器正对雷达时,首个栅瓣出现在预测的 + 41° 位置,该位置超出 ±30° 视场范围,因此不会导致雷达系统出现模糊度。但在长距离(自由空间路径损耗导致信号电平下降)且目标位于更大扫描角度(MIMO 方向图)的场景下,栅瓣可能进入视场,成为仅比真实目标弱 6 dB 的虚假目标 ------ 这也可能是大 RCS 角反射器与反射面共同作用的结果。尽管如此,该雷达系统仍可对 36 米范围内、±30° 方位角内的目标进行无模糊探测;对于更短距离,天线混响效应相较于增强的信号功率可忽略不计。

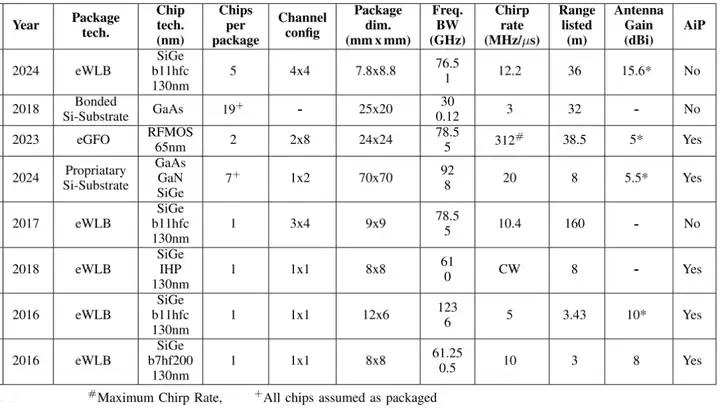

7. 新技术对比

表 1 汇总了已开展测距测试的主流系统级封装(SiP)方案。尽管已有研究尝试在玻璃或硅衬底上实现多Chiplet配置,但本研究首次在 eWLB 封装中成功实现该方案。此外,该方案在聚合物雷达封装中集成的Chiplet数量最多,同时封装面积处于较小水平(硅占比 17.8%)。其他 eWLB 相关研究中,天线封装一体化(AiP)是导致面积差异的主要原因:热机械面积限制使得封装设计需在多Chiplet集成与 AiP 之间取舍,这种权衡需在外形尺寸、射频衬底成本,与更高通道数、更高天线增益之间找到平衡。Chiplet尺寸是另一需权衡的因素:集成多个更小的芯片有助于提升雷达的可扩展性,但与扇入方案相比,多个热源被困在封装内,加剧了热管理挑战。线性调频斜率也是关键参数,其与最大可实现测距范围相关,但也对电路设计提出更高要求。与其他研究相比,本方案的线性调频斜率相近,因此测距范围也具有可比性。

表1、不同SiP的最新性能

8. 结论

本研究提出一种基于英飞凌 eWLB 技术的模块化系统级封装(SiP)方案,适用于 76--77 GHz 频段的车载短距雷达应用。该方案仅受最大封装尺寸限制,Chiplet数量、工艺类型以及通道数均可灵活选择。作为验证,本研究实现了一款自包含的 4×4 SiP,其尺寸仅为 7.8×8.8 mm²,内嵌五颗 B11HFC Chiplet。该 SiP 包含一个中央压控振荡器(VCO),为四个相同的收发器供电;借助新型双馈电本振(LO)分配网络,收发器的配置完全通过封装实现,使Chiplet设计可复用,大幅提升了系统可扩展性。未配置的芯片区域通过焊点直接实现热释放,高频信号、使能信号及供电则通过两层专用重分布层(RDL)布线,完成 LO 信号分配、Chiplet互连及与 PCB 的接口。本研究通过电磁和热机械分析,优化了所有过渡结构和焊球布局,实现了性能与可靠性的平衡。该雷达未采用天线封装一体化(AiP),而是通过 PCB 上的高稀疏天线阵列,在方位角和仰角方向实现模糊度消除与分辨率提升;15.6 dBi 天线形成 ±32° 的窄视场,有效抑制栅瓣影响。结合数据采集后端的实测结果表明,该系统可在真实环境中探测最远 36 米、方位角 ±30° 内的目标。

尽管仍存在系统性挑战,但本研究首次成功实现了面向车载应用的多Chiplet eWLB 雷达封装,将此前仅适用于数字电路的优势(如针对高性能或低功耗设备的产品细分、利用 RDL 无源结构实现高密度或灵活设计、通过不同工艺 / 节点的异质集成提升性能、效率并减小尺寸)拓展至射频Chiplet领域。