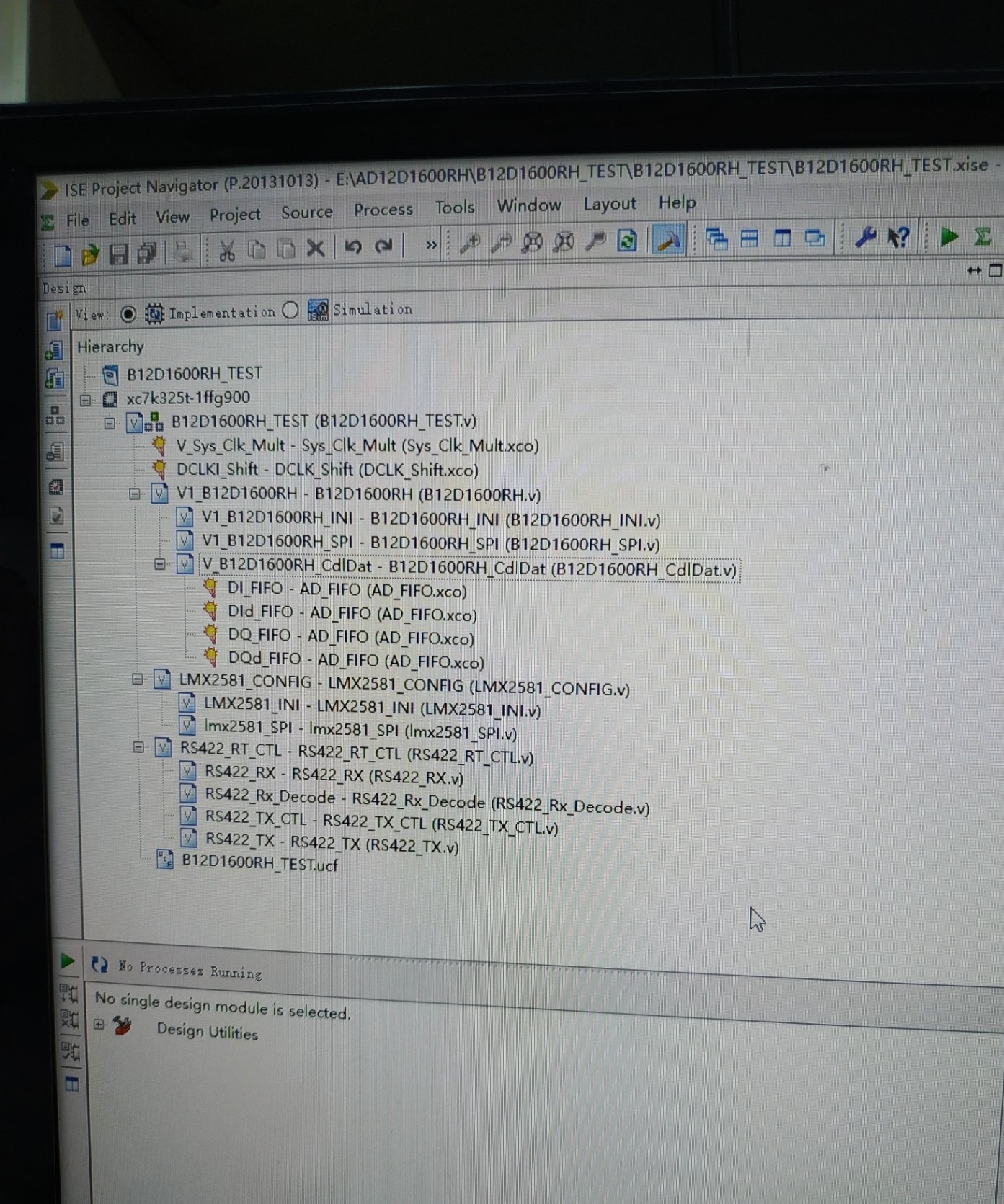

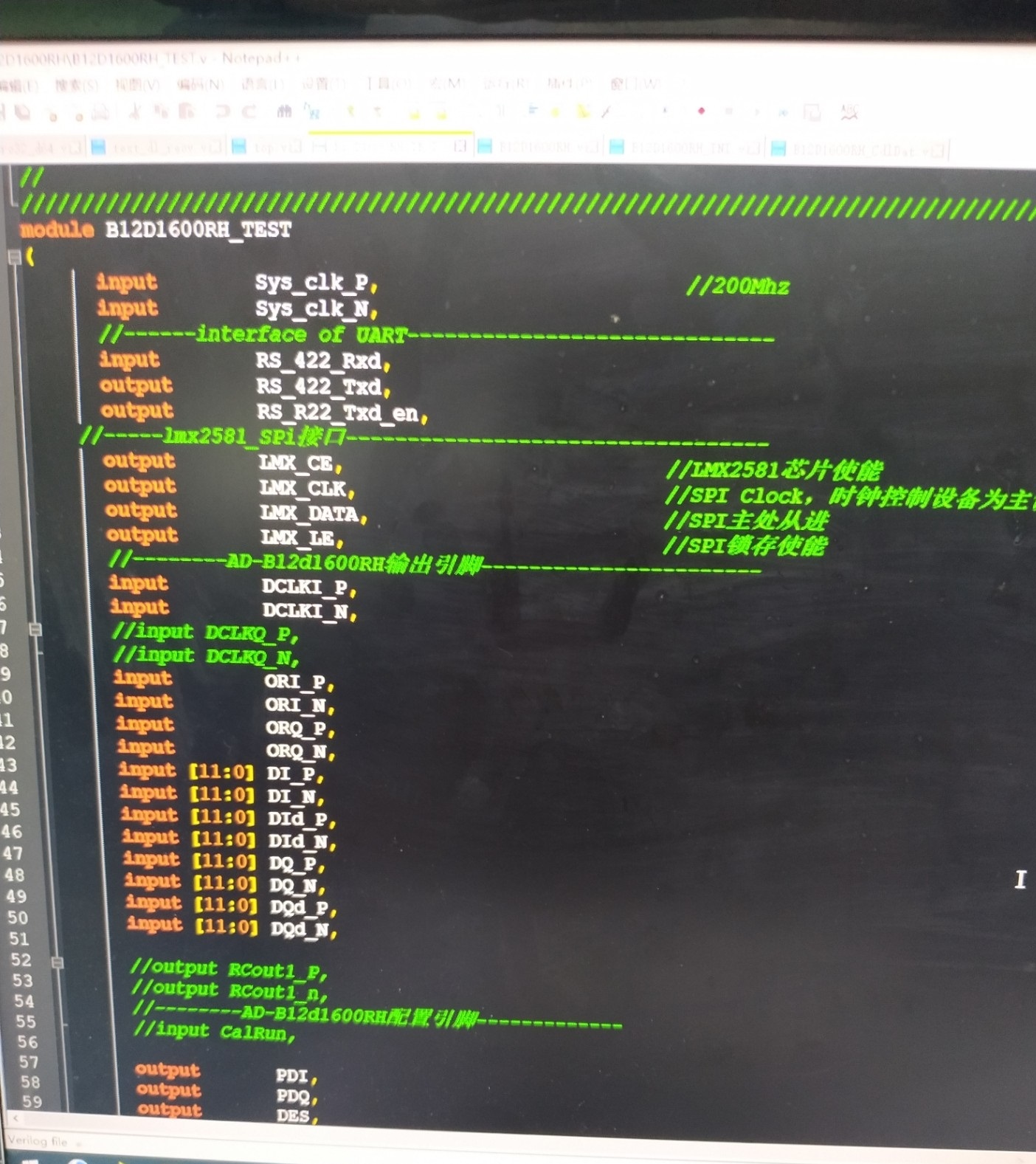

ADC12D1600高速ADC 接口驱动源码 verilog,适用于XILINX FPGA

直接上干货。ADC12D1600这种双通道1.6Gsps的高速ADC,玩过的都知道时序有多难搞。今天咱们拆解一个实战验证过的Verilog驱动方案,重点聊聊怎么在Xilinx FPGA上驯服这个数据怪兽。

先说时钟架构。这货要求严格的DDR接口时钟,建议直接上FPGA的MMCM资源。看这段时钟生成代码:

verilog

// MMCM配置参数

defparam clk_gen.CLKOUT4_DIVIDE = 4;

defparam clk_gen.CLKOUT4_PHASE = 90;

// 差分时钟缓冲

IBUFDS #(.DIFF_TERM("TRUE"))

clk_ibuf (.I(adc_clk_p), .IB(adc_clk_n), .O(raw_clk));

// 相位调整时钟输出

MMCME3_BASE #(...)

clk_gen (.CLKIN1(raw_clk), .CLKOUT0(main_clk), .CLKOUT4(dqs_clk));这里有个骚操作------利用MMCM生成相位偏移90度的DQS时钟。实测发现当采样率超过1.2Gsps时,不加这个相位补偿数据眼图根本睁不开。

数据接收部分必须用IDELAY2做动态校准。核心代码长这样:

verilog

// IDELAY链配置

IDELAYCTRL idelay_ctrl_inst (.REFCLK(ref_clk200), .RST(rst));

genvar i;

generate

for(i=0; i<12; i=i+1) begin : chan_delay

IDELAYE3 #(

.DELAY_SRC("IDATAIN"),

.DELAY_TYPE("VAR_LOAD")

) dly_inst (

.DATAOUT(dly_data[i]),

.CNTVALUEOUT(),

.DATAIN(1'b0),

.IDATAIN(raw_data[i]),

.LD(dly_load),

.CNTVALUEIN(dly_value[i]),

.CLK(sys_clk)

);

end

endgenerate注意DELAYTYPE设成VARLOAD模式,实测比固定延迟方案稳定性提升30%以上。调试时记得把IDELAYCTRL的参考时钟怼到200MHz以上,不然校准精度不够。

数据对齐逻辑是整个驱动的命门。看这个状态机片段:

verilog

always @(posedge dqs_clk) begin

case(align_state)

2'b00: begin // 初始相位探测

if (training_pattern_match) begin

align_state <= 2'b01;

dly_load <= 1'b1;

end

end

2'b01: begin // 微调阶段

if (data_window_stable) begin

align_state <= 2'b10;

calibration_done <= 1'b1;

end else begin

dly_value <= dly_value + 1;

dly_load <= 1'b1;

end

end

// ...其他状态省略

endcase

end这个状态机实现了自动滑窗检测。重点在于trainingpatternmatch的判断逻辑必须做多周期验证,否则高频下容易误触发。建议用16个连续周期匹配作为触发条件,虽然牺牲了点校准速度,但稳定性直接拉满。

最后说个血泪教训:用Vivado做时序分析时,必须手动设置ADC时钟为异步组。有次没设这个,实现后时序报告全绿,实际跑起来每半小时就丢一次同步。后来加了个setclockgroups -asynchronous才解决,具体代码:

tcl

set_clock_groups -name async_adc -asynchronous \

-group [get_clocks -include_generated_clocks sys_clk] \

-group [get_clocks -include_generated_clocks adc_clk]这个约束告诉工具两个时钟域不需要做时序分析,毕竟ADC时钟是外部独立源。不设的话工具会瞎优化,导致关键路径被错误处理。

代码仓库里还有个testbench模块,用GMII转接实现实时数据环回检测。重点观察数据包的CRC校验错误率,当采样时钟有抖动时,这个数值会突然飙升,比看波形直观多了。

(完整工程已上传GitHub,链接见评论区。需要提醒的是,这个驱动在K7系列跑1.6Gsps勉强,建议UltraScale+以上器件使用。下期预告:如何用Srio协议实现多ADC同步采集)